- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: Cannot program LPC4088-based custom board

Cannot program LPC4088-based custom board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cannot program LPC4088-based custom board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

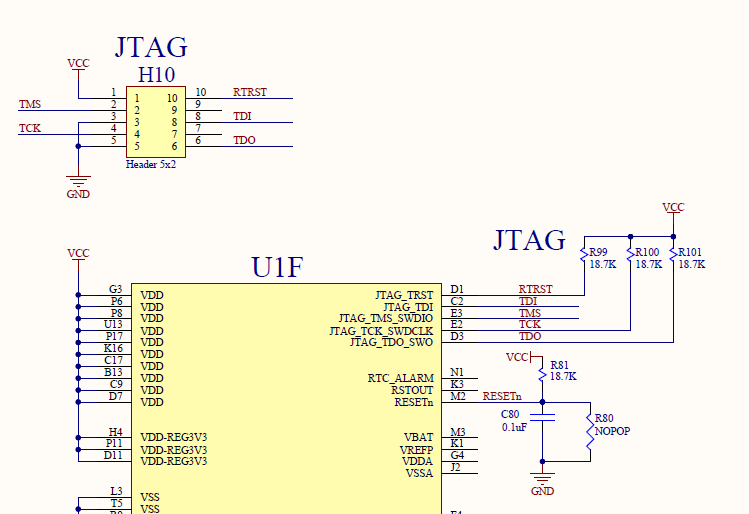

We cannot program or even erase the LPC4088 micro on our custom board. The board is based on the Embedded Artists LPC4088 QuickStart Board. Based on this schematic excerpt, what might we have done wrong?

We did already try connecting a jumper wire from the RESETn node to the RTRST node.

We're using an LPC-Link 2 to attempt the erase. As pictured below, we're using the Flash Programming GUI from the latest version of MCUXpresso IDE (v10.0.2 [Build 411] [2017-07-11]). We've tried both "Mass erase" and "Erase by sector" options; and we've tried with the "Use JTAG interface" option checked and unchecked. We get errors as shown below.

We are able to program and erase the LPC4088QSB with the same debugger (LPC-Link 2) and method (flash programming GUI), using the 20-pin ribbon cable, so I'm confident the problem lies either in the connection between the debugger and the board, or on the target board itself.

Output / error details:

Ns: MCUXpresso RedlinkMulti Driver v10.0 (Jun 22 2017 23:31:55 - crt_emu_cm_redlink.exe build 272)

Pc: ( 0) Reading remote configuration

Wc(03). No cache support.

Pc: ( 5) Remote configuration complete

Nc: Reconnected to existing redlink server (PID 4294967295)

Nc: Connecting to probe 2 core 0 (server PID unknown) gave 'OK'

Nc: Probe Firmware: LPC-LINK2 CMSIS-DAP V5.182 (NXP Semiconductors)

Nc: Serial Number: I3FUF1CU

Nc: VID:PID: 1FC9:0090

Nc: USB Path: \\?\hid#vid_1fc9&pid_0090&mi_00#7&19365f6e&0&0000#{4d1e55b2-f16f-11cf-88cb-001111000030}

Nc: connection to debug bus (DpID 0x2BA01477 AP Index[0]: 0xFFFFFFFF) <unknown wire type> failed - 'Em(04). Cannot provide power to DAP bus.'

Nc: connection failed - Em(04). Cannot provide power to DAP bus... Retrying

Nc: connection to debug bus (DpID 0x2BA01477 AP Index[0]: 0xFFFFFFFF) <unknown wire type> failed - 'Em(04). Cannot provide power to DAP bus.'

Ed:02: Failed on connect: Em(04). Cannot provide power to DAP bus.

Et: Probe(0): Connected&Reset. Was: NotConnected. DpID: 00000000. CpuID: 00000000. Info: <None>

Nc: Last stub error 0: OK

Nc: Last sticky error: 0x0 AIndex: 0

Nc: No debug bus (MemAp) selected

Nc: DAP Speed test unexecuted or failed

Nc: Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Pc: (100) Target Connection Failed

Nc: error closing down debug session - Em(02). MEM-AP is not selected.

LPC-Link 2 with harness (target board not shown):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Eight layer PCB design for best EMC performance, with controlled impedance and length matched routing for critical signals ..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

On startup it's running off the IRC at 12MHz. The maximum JTAG speed (supported) is 1/6 of CCLK (or PCLK?). So you shouldn't use 4000kHz for the adapter speed - set it to 2000kHz and the flash clock to 12MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan McDonnell,

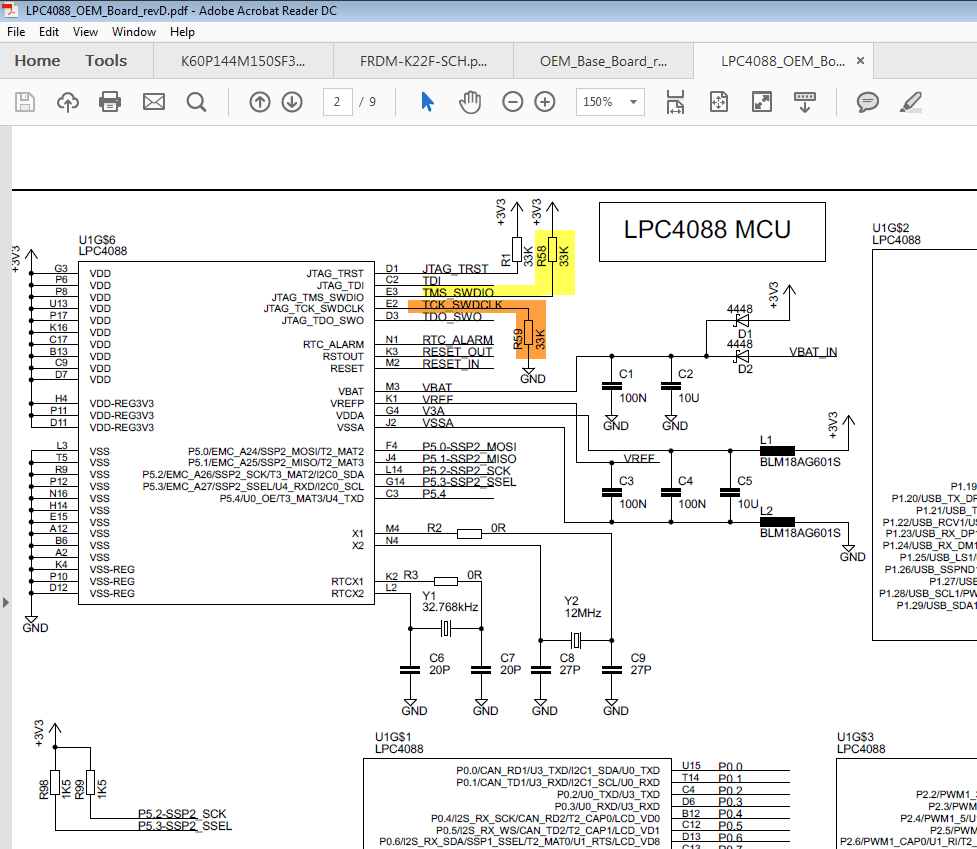

I find there has some errors on your table:

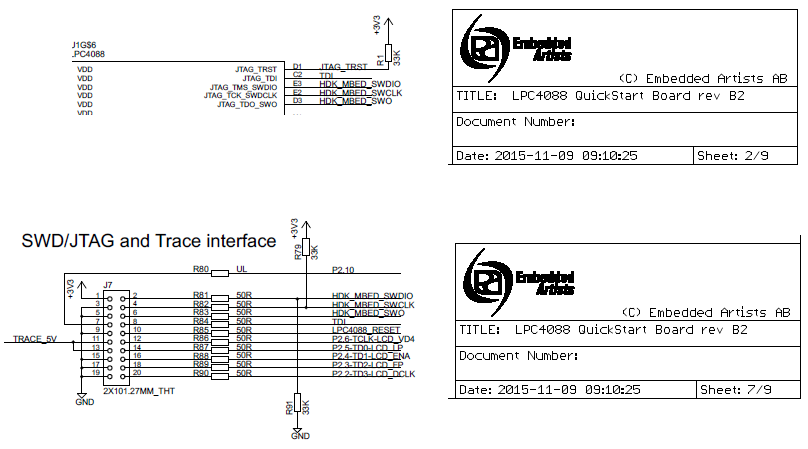

EA LPC4088 board, JTAG_TMS/SWDIO is pull up, JTAG_TCK/SWDCLK is pull down.

Please check the EA LPC4088 schematic:

I think you still can refer to the EA lpc4088 board, then configure the LPC-LINK2 to JLINK, use JLINK command, to check, whether it can find the core or not?

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry Zhou wrote:

I find there has some errors on your table:

...

EA LPC4088 board, JTAG_TMS/SWDIO is pull up, JTAG_TCK/SWDCLK is pull down.

It's not an error. I'm talking about the EA LPC4088QSB, not the LPC4088 OEM board.

EDIT: In fact, the OEM board is represented on the next line in the table.

I think you still can refer to the EA lpc4088 board, then configure the LPC-LINK2 to JLINK, use JLINK command, to check, whether it can find the core or not?

We did. Results described above.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan,

Thank you for your updated information.

Please make sure your P2[10] have the external pull up, this is very important.

These two EA LPC4088 board's connection is really conflict.

Now, if you can test, I think you can just use the SWD to try it, because SWD just need these pins: VDD, GND, SWD_CLK, SWD_DAT, RESET.

In the JLINK commander, select SWD interface. Hardware side, please try two connections:

1. SWD_CLK pullup, SWD_DAT pull down

Test it with SWD mode.

2. SWD_CLK pull down, SWD_DAT pull up

Test it with SWD mode

After you test it, please post me the JLINK Commander result for each connection. Besides, do you have any other customer board? Test another one, just make sure, it is not the board broken problem.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry Zhou wrote:

Please make sure your P2[10] have the external pull up, this is very important.

Thanks for the confirmation on that. (Note to readers, P2[10] is the ISP pin discussed above.)

This pin is buried under the BGA - there is no test point on the board - so we can't test any further with this board. We'll fix it on the next revision, and hopefully then we can program them!

These two EA LPC4088 board's connection is really conflict.

Yes, I'm still confused about that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan,

Yes, it is really very confused if you don't have the test point.

In the user manual:

Pin P2[10] is used as a hardware request signal for ISP and therefore requires special

attention. Since P2[10] is in high impedance mode after reset, it is important that the user

provides external hardware (a pull-up resistor or other device) to put the pin in a defined

state. Otherwise unintended entry into ISP mode may occur.

But, I think, it may not the root problem, because, even enter the ISP mode, the SWD interface should still can be enabled to download the code. I also test on my side, I enter the ISP mode by connect the P2[10] to 0, I still can enter the debug mode.

I even tried connect P2[10] all the time, but the debug mode still can be entered with SWD, if you have the EA lp4088 board, you also can try it.

Please use the SWD mode, and the JLINK command test it again, with:

1. SWD_CLK pullup, SWD_DAT pull down

Test it with SWD mode.

2. SWD_CLK pull down, SWD_DAT pull up

Test it with SWD mode

Then send the picture like this:

I need to check it again.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried the SWD interface earlier when I tried the JTAG interface, with the same or similar results.

At this point, we're going to wait for the next revision of our boards, which will have the ISP pin pulled-up, and the layout to support pull-ups and pull-downs on all the programming pins.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan,

OK, after you test your new board, any updated information, please kindly let me know!

Thank you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan,

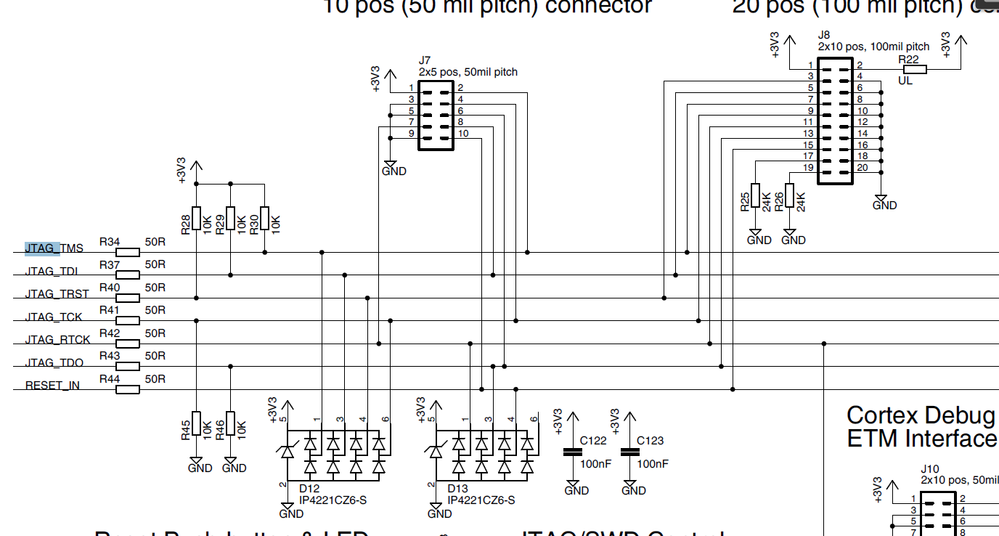

1. I found your schematic have some problems, especially the JTAG interface, the pull up pins is not correct, please refer to this picture:

TMS, TDI, TRST, need the external pull-up resistor.

But, TCK, TDO need the pull down, not the pull up resistor.

2. When you use the LPC_LINK2 J6 as the debugger interface.

Please make sure you shorten the JP2, otherwise the J6 won't work.

After you connect the JP2, and connect the LPC-LINK2 to your LPC4088 board, please change the lpc_link2 debugger firmware to JLINK, then open the JLINK Commander window, to check whether you can find the ARM core or not? If you can't find the core, you still need to check the hardware, the hardware still have problem.

If you can find the core, then you can use the IDE with JLINK to download the code.

Please follow my suggestion and try it again.

Any updated information, please kindly let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry,

Thank you kindly for your input. Adding the pull-ups / pull-downs resolved our issue, and enabled the LPC-Link 2 to communicate with the target micro [TEMPORARILY...see below].

For my reference, what device is that schematic from, and where did you get it? Do you know why the pull-up/pull-down resistors are required for our board, but not for the Embedded Artists' LPC4088QSB?

-----

EDIT: Looks like I spoke too soon. We were able to connect to the target a few times, but now I get the error shown below. BUT we currently have the resistors on the programmer side, not the target side, so there may be noise or grounding issues or somesuch. We are continuing to investigate.

Anyway, if you can still answer the questions above, that would be helpful.

SEGGER J-Link Commander V6.16b (Compiled Jun 9 2017 18:04:04)

DLL version V6.16b, compiled Jun 9 2017 18:03:30

Connecting to J-Link via USB...O.K.

Firmware: J-Link LPC-Link 2 compiled Sep 23 2016 12:15:22

Hardware version: V1.00

S/N: [redacted]

VTref = 3.300V

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: LPC4088

Type '?' for selection dialog

Device>?

Please specify target interface:

J) JTAG (Default)

S) SWD

TIF>

Device position in JTAG chain (IRPre,DRPre) <Default>: -1,-1 => Auto-detect

JTAGConf>

Specify target interface speed [kHz]. <Default>: 4000 kHz

Speed>

Device "LPC4088" selected.

Connecting to target via JTAG

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x4BA00477, IRLen: 04, CoreSight JTAG-DP

Scanning APs, stopping at first AHB-AP found.

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x4BA00477, IRLen: 04, CoreSight JTAG-DP

****** Error: Could not find AHB-AP to communicate with Cortex-M core.

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x4BA00477, IRLen: 04, CoreSight JTAG-DP

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x4BA00477, IRLen: 04, CoreSight JTAG-DP

Cannot connect to target.

J-Link>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brendan,

1. EA board pullup or pull down question.

Actually, EA board also have the pull up or pull down resistor, this is on the OEM_Base_board.

JTAG or SWD interface is the typical circuit, all the MCU are using this design. So, both your own board or the EA board should add the according external pull-up or pull-down resistor.

2. LPC-Link 2 to communicate with the target micro [TEMPORARILY...see below].

Do you mean, you sometimes can connect, but sometimes, you can't connect?

If yes, please try to shorten your JTAG wire, I check your connection picture between the LPC_LINK2 and your LPC board, the wire is too long, it will cause the signal not stable.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

EDIT again:

I may have found our issue. We don't have a pull-up on the ISP pin. I'll report back later.

Here is the relevant excerpt from Design Considerations for Debug:

- ISP

- Most NXP MCU's have an ISP pin which (when pulled low) can be used to cause the MCU to enter a bootloader on reset.

- For example on LPC17xx this is P2.10 and on LPC11xx and LPC13xx it is P0.1.

- Always ensure that you have a 10K to 100K Ohm pull up resistor on the ISP pin, otherwise you are unlikely to be able to make a successful debug connection.

- NOTE : LPC-Link2 (in both standalone form and as built in to the LPCXpresso V2 / V3 boards) has the ability to force an ISP reset via pin 7 of the Cortex 10-pin 0.05" JTAG/SWD Connector. For more details see the FAQ "ISP Reset over debug".

"Original" post below.

-----

Kerry Zhou wrote:

1. EA board pullup or pull down question.

Actually, EA board also have the pull up or pull down resistor, this is on the OEM_Base_board.

JTAG or SWD interface is the typical circuit, all the MCU are using this design. So, both your own board or the EA board should add the according external pull-up or pull-down resistor.

Perhaps the OEM_Base_Board is different, but that's not the example we're using.

There appears to be a variety of options, as summarized in the table below, but there are some odd contradictions. (Note that the user manual (UM10562) says that there are some internal pull-up resistors.)

What is going on with TMS/SWDIO and TDO/SWO? How can pull-up, pull-down, or nothing all be valid options?

| Doc | JTAG_TRST | JTAG_TDI | JTAG_TMS / SWDIO | JTAG_TCK / SWDCLK | JTAG_TDO / SWO |

|---|---|---|---|---|---|

| NXP Design Considerations for Debug | (not specified) | pull-up | pull-up | pull-up OR down OK (must not float) | pull-up |

NXP UM10562 (section 39.5) | none | none | none | pull-up | pull-up |

EA LPC4088QSB schem | pull-up | none | pull-down | pull-up | none |

EA OEM_Base_board (per Kerry Zhou) | pull-up | pull-up | pull-up | pull-down | pull-down |

our board | pull-up | none | none | pull-up | pull-up |

2. LPC-Link 2 to communicate with the target micro [TEMPORARILY...see below].

Do you mean, you sometimes can connect, but sometimes, you can't connect?

If yes, please try to shorten your JTAG wire, I check your connection picture between the LPC_LINK2 and your LPC board, the wire is too long, it will cause the signal not stable.

What I meant was that I was able to connect a couple of times on one board, and then never again on any of our boards. Odd.

We tried a shorter connection, but it didn't help.

We may try to build up a few more of our boards to try.