- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- Re: How to Save Input with pcm Frame scheme ?

How to Save Input with pcm Frame scheme ?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to Save Input with pcm Frame scheme ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

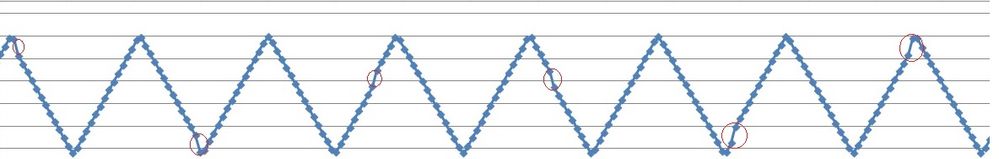

I want to save a Input signal ( see picture) and don’t know how to configure my i2s for this scheme . I have a frame of 21 words each word 24 bit . Only the first 8 words must be saved. But the adc need the time of 21 words to transmit data again. If the framesyn takes high state the adc send the data daisy chained on the rising edge of the frame sync. How can I realize the scheme in the picture ? Thx for replie

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Philipp,

Regaring the losing data, I have not idea. If you use DMA to transfer, how about setting the watermark as 1, DMA will fetch one data for one trigger. Secondly, you can use interrupt mechanism to fetch data.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Philipp,

Do you use the receiver bit clock as transmitter bit clock? if it is not the case, how do you generate the bit clock of SAI transmitter?

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Xiangjun,

i'm using the Receiveframesync , Receiver bitclock and the Receiver Data Pin of the TWR-K60F120m Evalboard. These Pins are connected with the ADS1278EVM Board from Ti. On this board is the adc placed. Yes i'm using the Receiverbitclock as SCLK for the adc.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I only want to receive the adc data. there is not transmit from twrk60f120m to the adc.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The SAI Module works in asynchron mod an generate the receiver bit clock and framesync signal . I don't cancel the communications of the EVM and the adc module

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Philipp,

i think the desynchronization leads to the problem, how do you generate the I2S transmitter bit clock? the ratio of the I2S transmitter bit clock frequency and TDM receiver bit clcok frequency is 8:21.

BR

xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Philipp,

From your brief description, I understand that you have a stream which has TDM format. The frame convers 21 slots, only the first 8 slots have valid data, the other 13 slots have invalid data. You want to acquire the 8 valid slot data and send them out via I2S format, is it correct?

For the input data stream, it is okay to use SAI module to acquire all slots data, you can discard the invalid 13 slots data and only save the 8 valid data to buffer, it is easy.

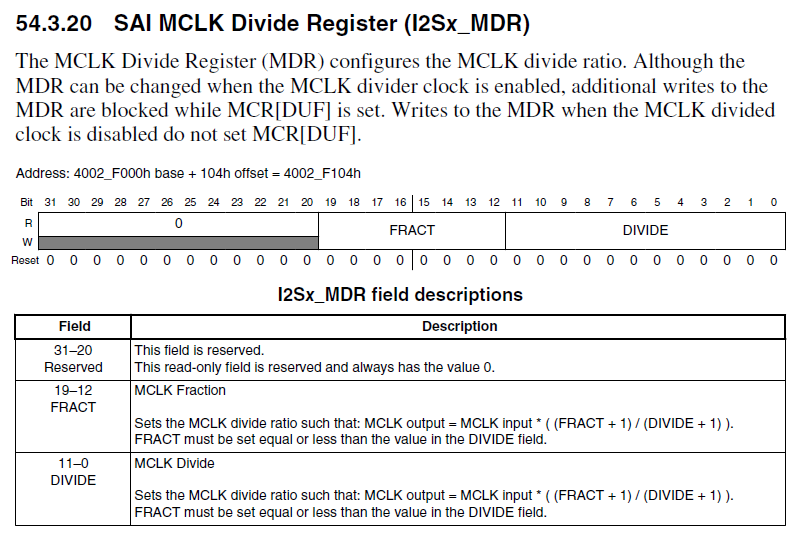

But you have to output the valid data stream via I2S format, the difficult task is synchronization, the (input bit clock frequency)/(output bit clock frequency)=21/8. Fortunately, the SAI module supports the feature, you can use the SAI transmitter/receiver in asychronous mode, in the case, transmitter and receiver use independent bit clock and frame clock, youn can connect the bit clock of receiver to MCLK, you can set the FRACT=7, DIVIDE=20, you can get the transmitter bit clock which is (7/21)*(receiver bit clock frequency).

In conclusion, you can use SAI receiver to acquire the valid data and save them in buffer. You can connect the Bit clock of SAI receiver to MCLK, use MCLK clock to get the bit clock of SAI transmitter, then use the SAI transmitter to transfer the 8 valid slot data.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you very much, sorry for the late response

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The sai with dma communication works fine now. The adc send data to the µC and the µC saves the data via dma. But i lose data. And i don't know how to fix it. I want to implement a continuous communication with the adc. After framesync is set i receive 8 words (25 bit) and 13 words will be ignored. The FIFO request Triggers the dma: watermark sai set on 2; dma Transaction set on 2 request 1.

red circles = lost data