- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: reception not possible in uart

reception not possible in uart

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Why does only transmission happens in UART communication (Using sample code LQRUG_uart_ex1 for KL25Z128 MCU) where data is not receiving instead it reaches to default handler function given below and suspends?

void Default_Handler()

{

__asm("bkpt");

}

can anyone please help me in this?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manvitha,

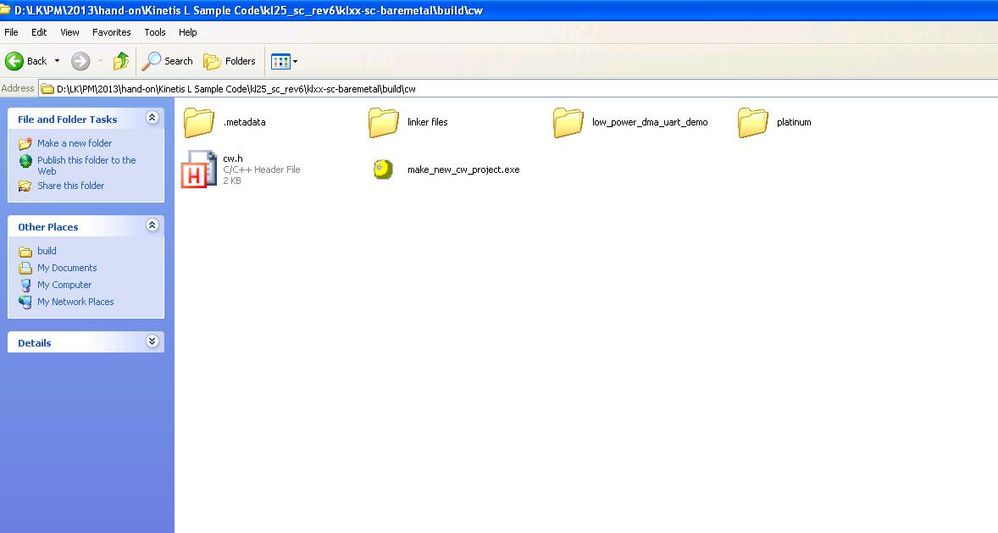

IAR and CW are different IDE tools , and the main difference is the compiler. So you can not directly import the source code for a IAR project into CW workspace, some definitions might be different and some might miss, To creat the CW based project, please run "make_new_cw_project.exe" in "Kinetis L Sample Code\kl25_sc_rev6\klxx-sc-baremetal\build\cw". Please kindly refer to FRDM_KL25ZSCG_CW.pdf in "Kinetis L Sample Code\kl25_sc_rev6" for more details.

can we configure two different port pins for Tx and Rx or is there any other way?

-Yes, you can do that. just remember don't enable two sets of TX and RX for the same UARTx module.

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Manvitha

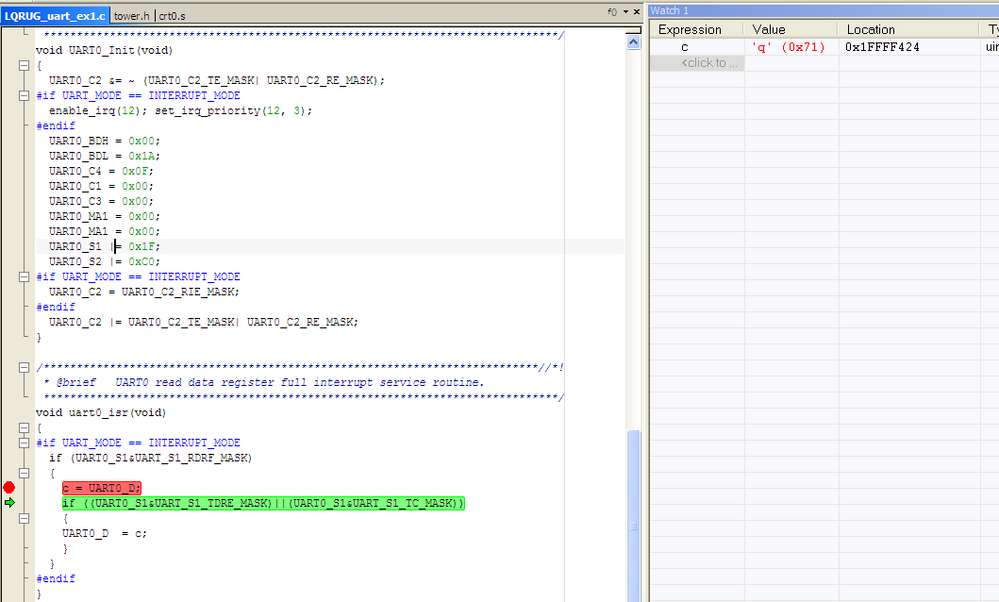

I tested project from path \Kinetis L Sample Code\kl25_sc_rev6\klxx-sc-baremetal\build\iar\LQRUG_uart_ex1. It can work well. Please reference following picture. As you can see, I use HyperTerminal and press character q, then c get the value of q.

I think your project might not be newest one, would you please help to download and test again. And also pay attention to baudrate is 115200.

Hope my reply can help you.

Best Regards

Paul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Zhe Tian

Even I am doing with the same code with port A 2 and port A 1

pins and given the same baudrate (#define TERMINAL_BAUD 115200) but it

is pointing to Default_Handler() (attached image 2) when it reaches printf

statement in the beginning of code(attached image 2)

I test the code in following steps

- Build the selected code

- connecting the board with pc and open the tera term with selecting

particular com port with baud 115200

- debug and run the code step by step(F6)

it will halt(suspend) pointing to default handler. can I know where my

fault is?

Thanks and Regards,

Manvitha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manvitha,

Could you post screen shots of your register values before you enter the Default_Handler for the following registers: SIM_SOPT2, SIM_SCGC4, UART0_BDL, UART0_C4, PORTA_PCR1 & PORTA_PCR2?

Thank you,

Martyn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martyn,

attached is the screenshot of register initialisation(image 1). it

will enter this initialisation register(during step by step execution)

while printf statement in the beginning is disabled.(image 2)

Thanks and Regards,

Manvitha.

On Thu, May 30, 2013 at 7:46 AM, Martyn Hunt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the attachment, seems you are using the CW , but I am confused as there is no CW based LQRUG_uart_ex1 project in the latest Kinetis L Sample Code

so are you referring to your custom CW project which is ported from the IAR based LQRUG_uart_ex1 project? would you please help to clarify? Thanks for your patience!!

BTW, if you are doing the porting, there is one thing to notice:

UART port is initialized in sysinit.c, for FRDM-KL25Z, PTA1 and PTA2 are used as UART0, but if the PORT_Init() in the main() configures another set of UART0 port, RX function might have problem, though TX should still be fine.

Transmit works just fine if you accidentally configure two pins for the same function, because they are both driven by the same module, but if you configure the input function on two pins then you get undefined behavior, because they are both driving the same thing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kan Li,

yes I referred to custom CW project which is ported from the IAR

based LQRUG_uart_ex1 project I mean to say that i just imported the code with

all source files(common, cpu, drivers, platform and sysint). from the path

*..\Kinetis L Sample

Code\kl25_sc\klxx-sc-baremetal\src\projects\LQRUG_uart_ex1** *

Is there any problem in doing that? please clear me on this.

And coming back to porting by configuring the input function on two pins we

will get undefined behavior then can we configure two different port pins

for Tx and Rx or is there any other way?

Thanks and Regards,

Manvitha.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manvitha,

IAR and CW are different IDE tools , and the main difference is the compiler. So you can not directly import the source code for a IAR project into CW workspace, some definitions might be different and some might miss, To creat the CW based project, please run "make_new_cw_project.exe" in "Kinetis L Sample Code\kl25_sc_rev6\klxx-sc-baremetal\build\cw". Please kindly refer to FRDM_KL25ZSCG_CW.pdf in "Kinetis L Sample Code\kl25_sc_rev6" for more details.

can we configure two different port pins for Tx and Rx or is there any other way?

-Yes, you can do that. just remember don't enable two sets of TX and RX for the same UARTx module.

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kan,

I had no idea about IAR IDE compiler hope I will do good now. thank

you for the guidance.

Regards,

Manvitha.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, make sure that NO_PLL_INIT is defined. If it is, make sure that the following section in sysinit.c looks like this:

#if defined(NO_PLL_INIT)

mcg_clk_hz = 21000000;

SIM_SOPT2 &= ~SIM_SOPT2_PLLFLLSEL_MASK; // clear PLLFLLSEL to select the FLL for this clock source

uart0_clk_khz = (mcg_clk_hz / 1000); // the uart0 clock frequency will equal the FLL frequency

In addition, make sure that UART0 is being re-initialized to the correct baud rate (115200). The UART0 register settings in the UART0_Init function should look like so:

UART0_BDH = 0x00;

UART0_BDL = 0x1A;

UART0_C4 = 0x06;

UART0_C1 = 0x00;

UART0_C3 = 0x00;

UART0_MA1 = 0x00;

UART0_MA1 = 0x00;

UART0_S1 |= 0x1F;

UART0_S2 |= 0xC0;

For future reference, the UART baud rate is defined as such:

/*

* baud rate = CLK / [(OSR + 1) x BR]

* Where CLK is the bus clock speed in hz,

* OSR is over sampling ratio (UARTx_C4 bits 0-4),

* and BR is baud rate modulo divisor (UARTx_BDL bits 0-7).

*/

Further explanation can be found in Chapter 39 of the KL25 Reference Manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why write to UART_MA1 twice?

- UART0_MA1 = 0x00;

- UART0_MA1 = 0x00;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Markosiponen,

I think it should be a typo issue, and it should be like that:

- UART0_MA1 = 0x00;

- UART0_MA2 = 0x00

Please kindly let me know if you have any further question.

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martyn,

I came to know that I had imported IAR project to CW workspace.

Only with this changes will it work fine?

Thanks and Regards,

Manvitha.

On Fri, May 31, 2013 at 7:16 AM, Martyn Hunt