- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- fcrdiv

fcrdiv

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

fcrdiv

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

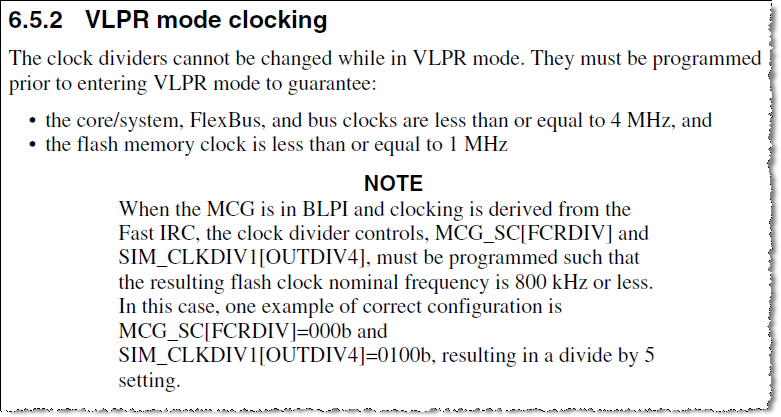

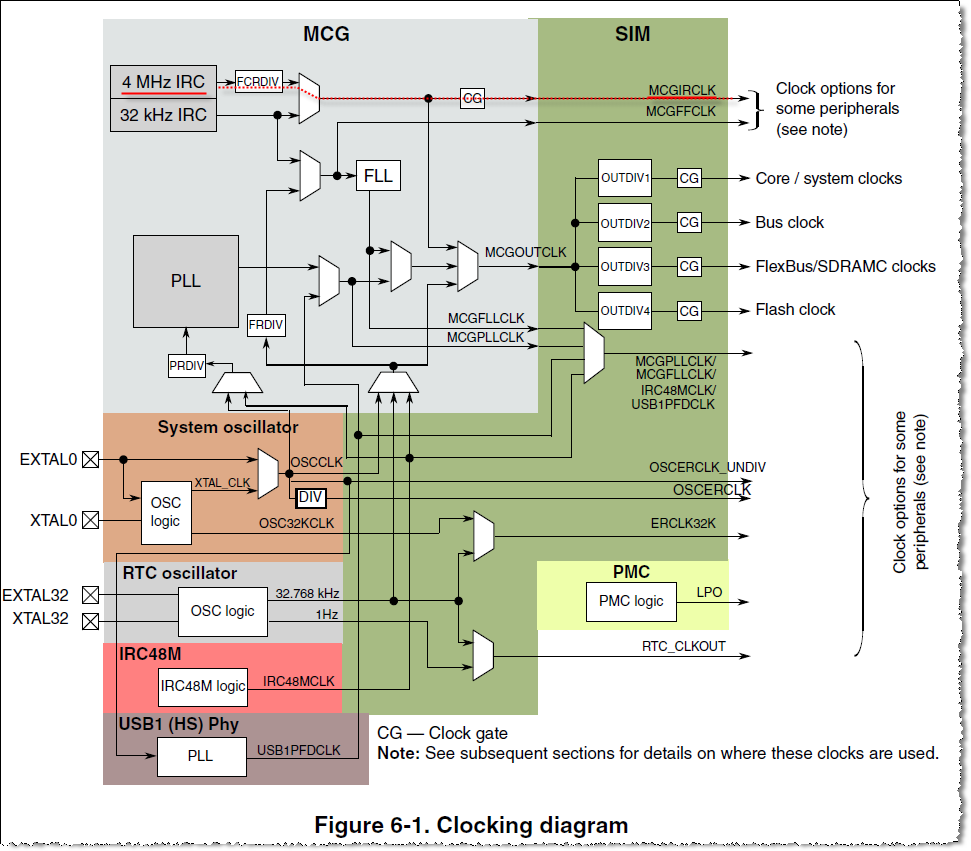

using FCRDIV to get to 4 Mhz in VLPR mode on the Kinetis K65.

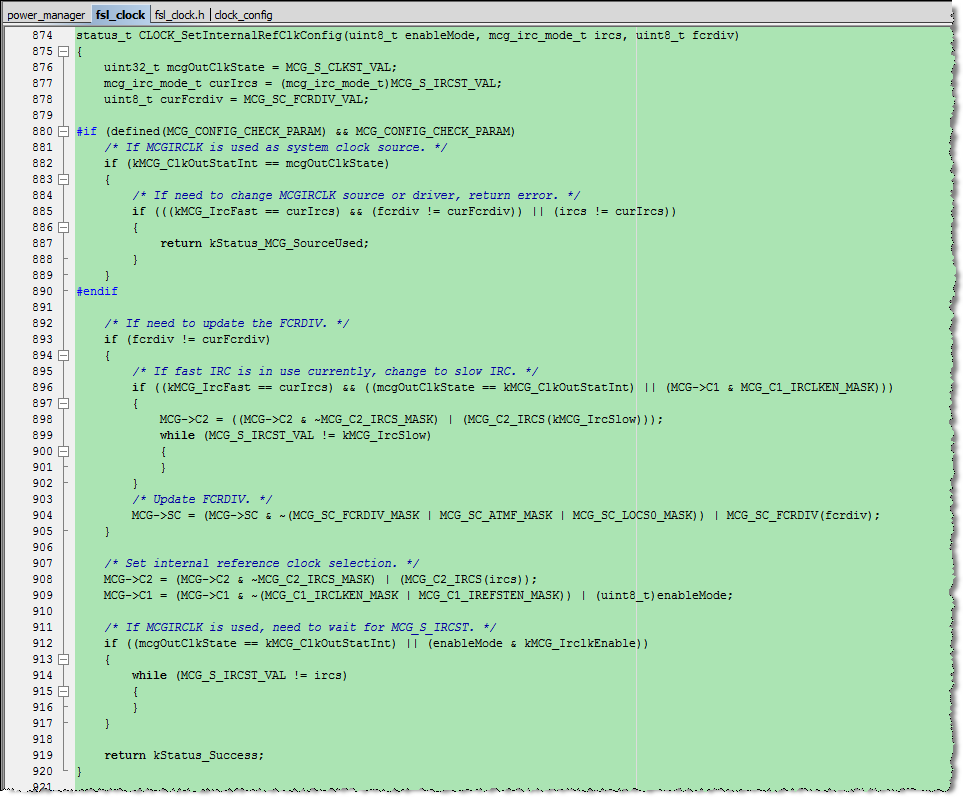

Upon bootup while in FEI state I set MCG_SC_FCRDIV(0).

The code then transitions to RUN mode running of an external oscillator.

Our code will transition into and out of VLPR mode from the run mode depending if there is processing that needs to be done.

Whenever we go into VLPR mode running off the internal 4 Mhz clock we only see a clock out of 2 Mhz. It acts like my setting of FCRDIV is not working. If I set it to zero the divider should be 1 and then I should see a 4 Mhz output.

While in VLPR the SIMDIV has been set to 0 for core, system, and flexbus. That means there is no divider on MSGCLKOUT. The flash clock is set to make sure the flash clock restriction is met while in VLPR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you robin. Unfortunately the code that I work with will not work on the tower.

I do have some more questions.

1. I am setting the MGC_SC and the SIM_DIV registers before entering VLPR. I actually set up the MGC_SC register in the FEI state. Does the FCRDIV setting have any effect while in in any other mode such as RUN as long as the internal fast clock is not enabled?

2. Does this setting of FCRDIV look correct? I am setting this in the FEI state.

// Set FCRDIV to 0 so that when the internal fast clock is used it will not

// be divided down. This will allow us to get to the max frequency of the

// 4 Mhz fast clock.

unsigned char tempRegister = MCG_SC;

tempRegister &= ~(MCG_SC_FCRDIV_MASK);

tempRegister |= MCG_SC_FCRDIV(0);

MCG_SC = tempRegister;

3. I am setting the dividers just before entering VLPR mode. MSGCLKOUT should be at 4 Mhz because of the setting of FCRDIV. Does this look correct?

// The MSGCLKOUT is then divided by SIMDIV of 0, 0, 0, 7.

//

// 0 = divide by 1

// 7 = divide by 8

//

// Thus, the following rates apply in this situation:

// Core/System = 4Mhz

// Bus = 4Mhz

// Flexbus = 4Mhz

// Flash = 500Khz // Cannot go over 800 due to security processor errata

// see section 6.5.2 VLPR mode clocking in reference manual

SetSysDividers2( 0, 0, 0, 7 );

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chris,

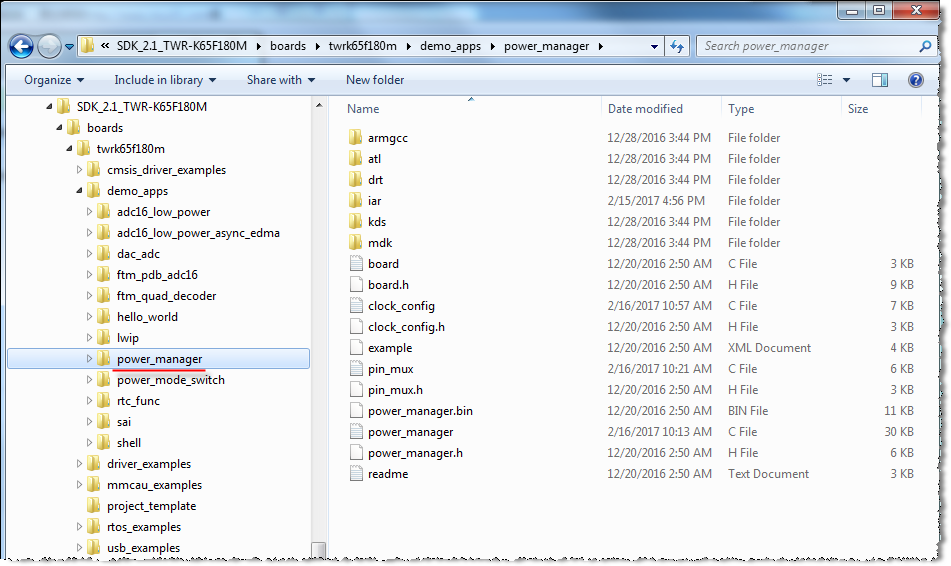

The MCG\SIM\OSC module of MK65FN2M0VMI18(on TWR-K65F180M) and MK65FN2M0CAC18 is the same.

You can refer the code in that exmaple.

And have you try to observe the 4MHz MCGIRCLK on CLKOUT pin(PTC3)?

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

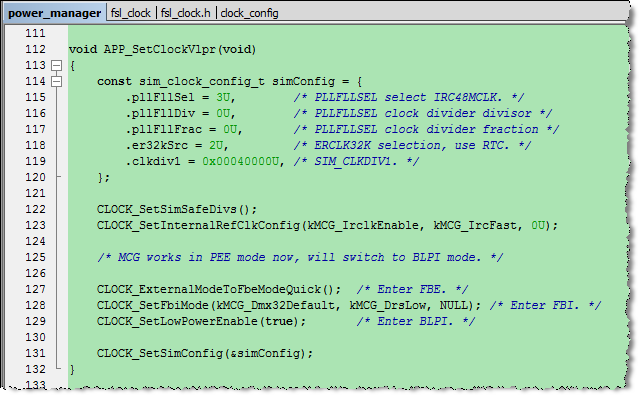

Hi Chris,

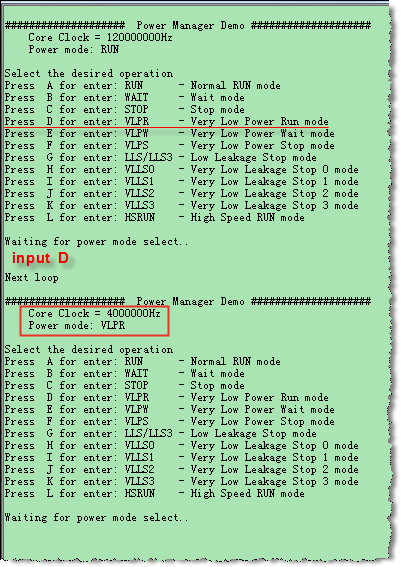

Have you try to test the power_manager demo in SDK_2.1_TWR-K65F180M.

After input D , the MCU will enter VLPR. And you will get the Core Clock = 4MHz.

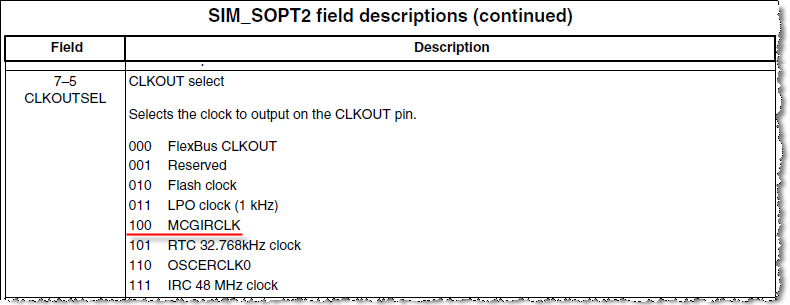

You can observe the 4MHz MCGIRCLK on CLKOUT pin(PTC3):

1. Open the Clock Gate of PORTC. CLOCK_EnableClock(kCLOCK_PortC);

2. Select the Pin Mux of PORTC3 to Alternative 5 as CLKOUT function. PORT_SetPinMux(PORTC, 3u, kPORT_MuxAlt5);

3. Select the MCGIRCLK to output on the CLKOUT pin. CLOCK_SetClkOutClock(0x04);

See also below information.(It seems that you have already notice these informations.)

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

![MCG_SC[FCRDIV].png MCG_SC[FCRDIV].png](/t5/image/serverpage/image-id/21052i137B5636D2F0954C/image-size/large?v=v2&px=999)