- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- What are the voltage levels for detecting logical low/high on the MKE04P80M48SF0?

What are the voltage levels for detecting logical low/high on the MKE04P80M48SF0?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What are the voltage levels for detecting logical low/high on the MKE04P80M48SF0?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

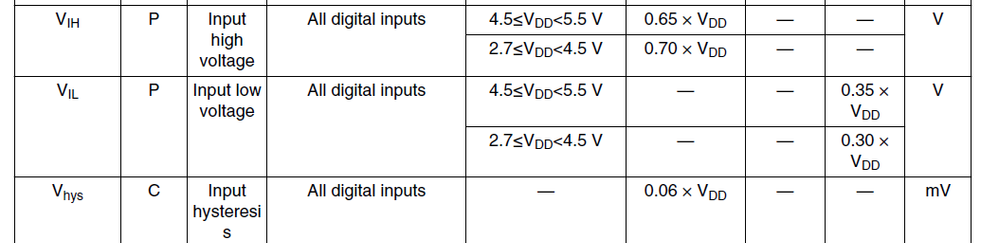

Reading the datasheet i can see that the voltage levels are suppose to be: (column 6 is min and 8 max)

Which means i should detect a low under 5V*0.35 = 1.75V and a high over 5V*0.65 = 3.25V

and the hysteresis 5V*0.06 = 0.3V

When i did my own measurements i got the following:

High to low : 2.26V

Low to high: 2.76V

Hysteresis: 0.5V

Neither of my results agree with the datasheet. Am I interpreting the datasheet wrong? Did i configure the port wrong?

The voltages was measured with a DMM at the pin on the uC and a program with just reads out the register status.

/Marcus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are just looking at the difference between 'datasheet guaranteed response points' and typical-part values. That is, you can generally expect 'wider than 300mV hysteresis', and 'well centered about 1/2Vdd'. The datasheet just has 'margin built in' to allow for per-part process variations.

The other thing to always keep in mind about CMOS logic is that any 'intermediate voltage' creates some rail-to-rail cross-conduction in the input-stage transistors, leading to a small increase in device current.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Earl,

This built in margin, where can I see in the datasheet that they have added it? or is this a general knowledge.

So this mean that if i want to find the actual 'switching' level of a port I need to measure it.

Could you pleas elaborate a bit more what you mean in the second part. Why would this effect my 'logical' reading of the port?

/Marcus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think we will classify this under 'general knowledge'. That is, ANY digital-function device will list the voltage above which an input is GUARANTEED to be sensed as a logic '1', and another voltage below which it is GUARANTEED to be sensed as a logic '0', and 'between those' is a no-man's-land for which the forwarded logic-level is indeterminate. Now these parts have hysteresis on the inputs, so at least a 'mid voltage input' will not bounce around and do 'silly things', but (to use your 5V example) any voltage between 1.75V and 3.25V CANNOT be expected to resolve as 'any particular' logic level (and, as I also mentioned, will result in increased input-stage current). 'In general' you can 'expect' the P and N FETs of a CMOS input stage to be 'fairly well balanced', and thus to switch 'very near 1/2 Vdd'. This 'datasheet margin' (+/-0.75V on your 5V example) is there to allow some imbalance to exist over a range of parts and pins (and thus tolerance for the manufacturing variables such as those defining circuit element dimensions and 'transistor doping' levels), yet give a circuit designer 'known limits' to work within.

Even if you 'measure' a particular part&pin 'switch point' at some particular temperature, you MUST expect that 'switch point' to be different for other parts/pins/temps, anywhere within the 'guaranteed limits' of the datasheet.

If you need ANY kind of 'assured switching points', you need to use 'real' comparator(s), either internal or external, which give 'much tighter' switch-points against some reference voltage (at the expense of being slower analog circuits, of course!).