- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Valid Clock Frequencies for K32 ADC

Valid Clock Frequencies for K32 ADC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Valid Clock Frequencies for K32 ADC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to understand the effect of the ADC CFG2[ADHSC] (High-Speed Configuration bit) for the K32. Supposedly it configures the ADC for very high-speed operation, but it always adds two addition ADCK cycles to the total conversion time.

Judging from the data sheet, one must set ADHSC = 1 to use the maximum ADC conversion clock frequencies. What frequencies require this? What are the range of valid clock frequencies if ADHSC = 0?

Additionally, what is the impact of ADLPC (Low-Power Configuration)? What are the range of valid clock frequencies if ADLPC = 1?

The data sheet only lists minimum and maximum clock frequencies, but not the range of valid frequencies for a given configuration.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

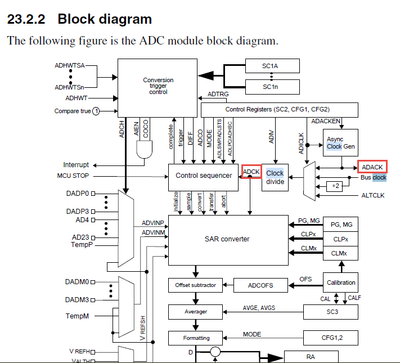

I suppose that you use K32L2 family, this is the ADC block diagram, from the diagram, you can see that the ADC clock ADCK can be from 4 sources:ADCACK(fADCACK ADC asynchronous clock source), Bus clock, divided2 bus clock, ALTCLK.

If you want to get the highest conversion rate, you have to select Bus clock, which can reach up to 24mhz, the ADC conversion rate can reach up to 1.2MBPS.

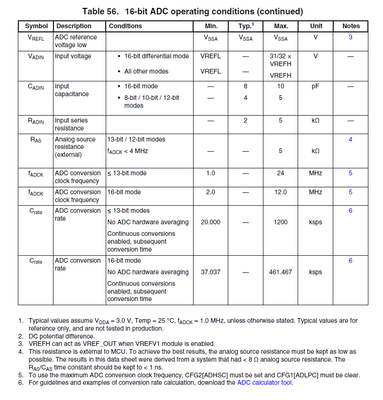

This is the table using bus clock:

If you want to get the normal conversion rate, you can select asynchronous clock ADACK, which can reach up to 6.2mhz typically, when ADLPC=0, ADHSC=1.

This is ADC block diagram.

For the detailed conversion rate computation, pls refer to 23.5.4.5 Sample time and total conversion time in K32L2B3xRM.pdf

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Judging by table 57 from the datasheet, it appears that ADHSC only affects the achievable clock frequencies when using the Async Clock. Is that correct? (Though it always adds 2 cycles if enabled, regardless of clock source?)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, when you set the ADHSC bit,two more ADCK cycles are required to convert one analog channel.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I understand the additional 2 clock cycle penalty. But is there any reason to use ADHSC if not using the Async Clock? For example, if using the Bus Clock, using "High-Speed Configuration" seems to simply slow down conversion by adding two clock cycles, and has no impact on the actual clock speed. Is that correct? If so, even though called "High-Speed Configuration", it actually slows things down. The documentation is frustratingly unclear about this point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you want to get high conversion rate for ADC of K32L2 family, you have to use BUS clock, the ADCK clock must be less than 24Mhz, the ADCK clock is the output of the ADC clock divider, while you have to set the ADHSC bit and clear the ADLPC bit.

The high speed mode is enabled by setting the ADC_CFG2[ADGSC], the ADC high speed mode is a mechanism of ADC conversion.

Hope it can help you

BR

Xiangjun rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now I see in footnote (5) of Table 56 that ADHSC maybe does apply even when using a clock source other than the Asynchronous Clock ADACK.

I also see in the reference manual:

CFG2[ADHSC] must be used when the ADCLK exceeds the limit for CFG2[ADHSC]=0.

Are these limits published anywhere? In Table 56, it lists the minimum and maximum f_ADCK, but it doesn't describe what the limiting case for ADHSC = 0 is.

For example, with ADICLK = BUS Clock (24 MHz), and divisor = 2, the ADCK is 12 MHz. This is at the maximum for 16-bit conversions, so I assume this requires ADHSC = 1 . Is that correct?

With divisor = 4, the ADCK = 6 MHz, which is in between the minimum and maximum f_ADCK for 16-bit conversions. Is this achievable with ADHSC = 0?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For the ADC of K32L2 family, the UM is unclear about the high speed and low speed ADC clock frequency.

This is an internal table for the ADC setting.

Hope it can help you

BR

XiangJun Rong