- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Setting up clock rate for I2S with SGTL5000

Setting up clock rate for I2S with SGTL5000

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Setting up clock rate for I2S with SGTL5000

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

G'day!

I've been reading up on how to use the I2S module in my K70 elevator tower with the SGTL as the TWR-AUDIO extension.

I am a little confused as to what the right question to as is..

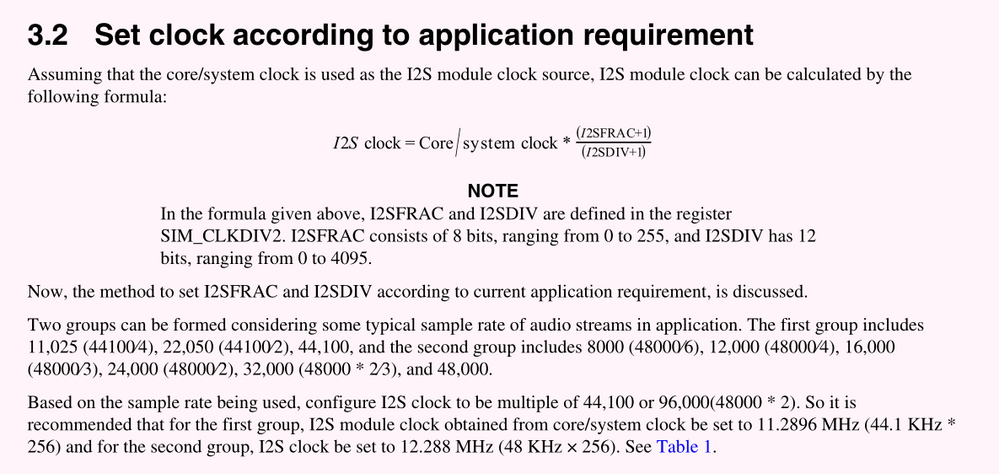

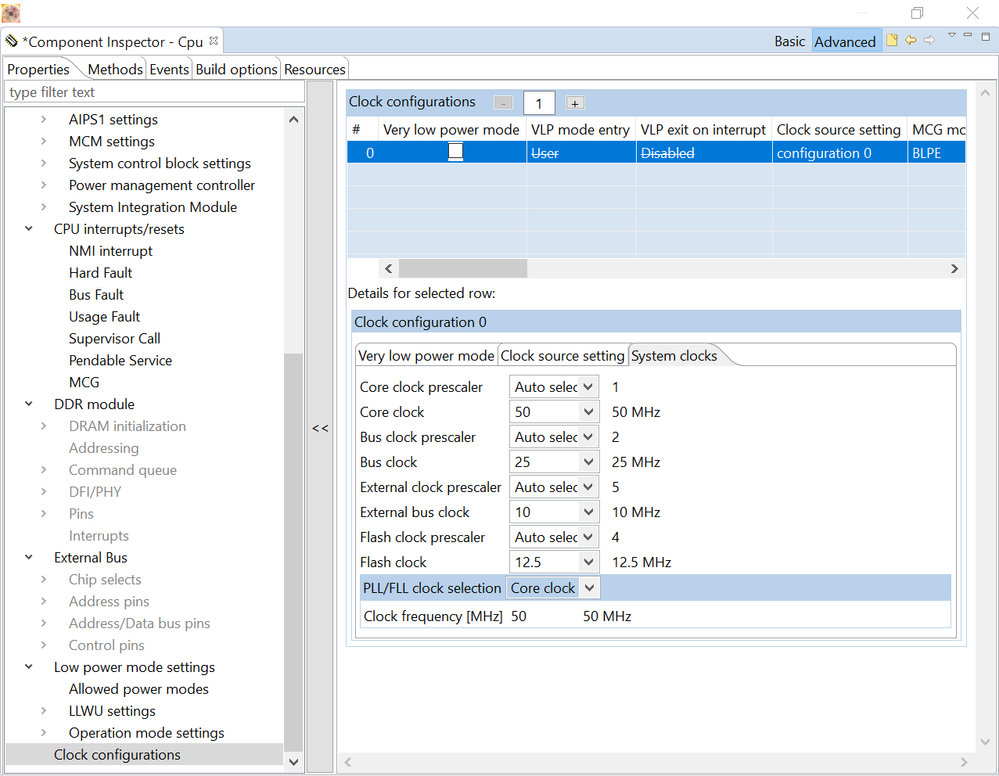

So I have the system oscillator set at 50Mhz as default and have noticed the I2S module is derived from the (Core/System clock)*((I2SFrac+1/I2SDiv+1)). For example, If I wanted 48 Khz as my sampling rate, I would multiply by 256 to get 12.288 Mhz for the I2S clock.

And further more, on the next page,

I could not find the I2Sx_PCCR register in the K70 Sub-Family Reference Manual, so I don't know what PM stands for.

My question is "should I be changing the K70 OSC0 to 12.288Mhz or 4Mhz"?

Which I think would be a bad idea due to other clocks prescalar on it...

Another idea I had was that I just keep it at 50Mhz and derive the 12.288Mhz on the Bus Clock but the closest I can get it is 12.5 Mhz which is not good enough.

Thank you for your time!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Pang,

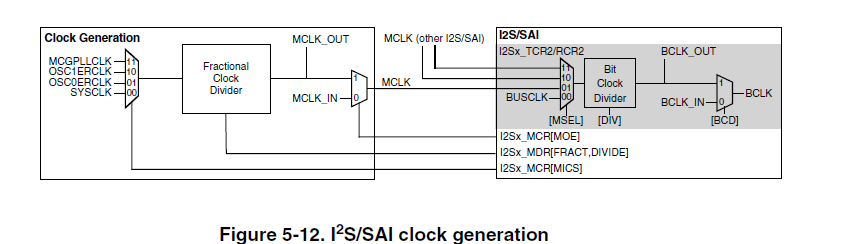

When the I2S is configured as master, the bit clock and frame clock sources are internal or external. This is the I2S clock source diagram for K70, I copy it from reference manual of K70.

Assume that the sampling clock is 48KHz, you use 32 bits data for left/right channel, the required bit clock frequecy BCLK is 64*48K=3.072MHz. No matter how you divide the clock source and where the clock source is, it is okay if the bit clock frequency is 3.072MHz.

There is not I2Sx_RCCR register for K70, probably you refer to wrong processor by mistake.

Assume that the core/system clock is 50MHz for your case, the Bit Clock Divider is 4, the MCLK must be 3.072M*4=12.288MHz, the MCLK frequency is 12.288MHz. 50MHz/12.288MHz=4.069, I suppose that you can set the FRACT=0, DIVIDE=3, it is okay. The actual bit clock will be 50MHz*1/(4*4)=3.125MHz.

as an alternative, assume that the core/system clock is 50MHz for your case, the Bit Clock Divider is 1, the MCLK must be 3.072MHz. The 50MHz/3.072MHz=16.276, I suppose that you can set the FRACT=99, DIVIDE=1626, it is okay, the actual MCLK will be 50MHz*(99+1)/(1626+1)=3.073MHz, it is okay.

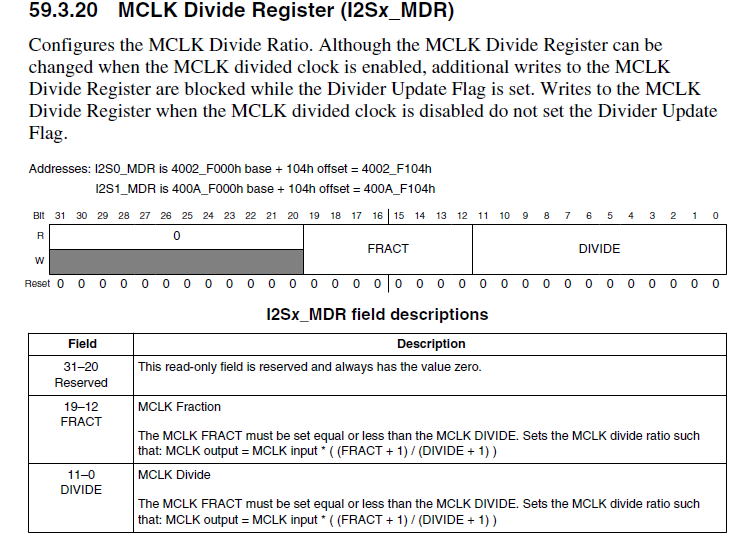

This is the register setting, which I copy from RM of K70:

Hope it can help you

BR

Xiangjun Rong