- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Selection of crystal values for MK70FN1M0VMJ12

Selection of crystal values for MK70FN1M0VMJ12

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Selection of crystal values for MK70FN1M0VMJ12

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear community members,

Request you to give details on how to select external crystal values so that I can operate MK70FN1M0VMJ12 at 120MHz. I was going referring the Tower board schematics in which two

crystal were used i.e. 12 MHz and 50MHz and I want to know based on what factors these 2 crystals (12MHz and 50 MHz) were chosen and also want to know if single crystal is enough to operate MK70FN1M0VMJ12 at maximum speed of 120MHz.

Request you to reply at earliest

Thanks and Best Regards,

Puspam Nayak

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Puspam Nayak,

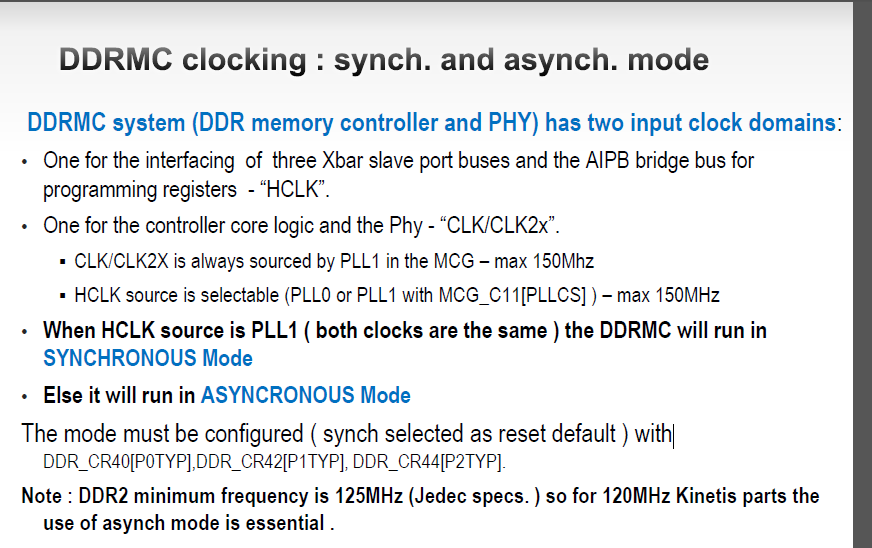

You might have referred to TWR-K70F120M, so you have question why 50MHz and 12MHz are selcted, actually, 50MHz is for Ethernet application when RMII interface is used, because when the K70 Ethernet MAC is operating in RMII mode, synchronization of the MCU input clock and the 50 MHz RMII transfer clock is important. In this mode, the MCU input clock must be kept in phase with the 50 MHz clock supplied to the external PHY. and 12MHz is for DDRC module and DDRC's PHY, because DDRC module has two modes, sync and async, with the 12MHz crystal, you may get DDRC in sync mode. Please kindly refer to the following for more details.

!

so if your application doesn't use Ethernet or DDR2 RAM, one single crystal is enough. To calculate the PLL output, you may use the Process Expert of CW 10.6 to simulate MCG module configration, please also note the PLL ref clock is 8MHz at least.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kan,

Thanks for sharing the valuable information. I need some more

information on this, I am using DDR2-800, NAND Flash (response time is 20 ns

or 50 ns), USB 2.0 for my application but not Ethernet so please let me

know how should I select crystal values so that I will get best response. Want

to know if I can use either EXTAL0 (PLL0) or EXTAL1 (PLL1) for my

application or I have to use 2 crystals i.e. EXTAL0 and EXTAL1.

Secondly I was going through the document which you shared but

not able to understand the statement “ One for the controller core logic and

the PHY CLK/CLK2x. CLK/CLK2x is always sourced by PLL1 in the MCG-max

150MHz”. Request you to give some more detailed clarification on this.

Thanks and regards

Puspam Nayak

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Puspam Nayak,

Since you are using MK70FN1M0VMJ12, you may have the following solution for the clock settings:

- PLL0 is 120MHz, and PLL1 is 150MHz(possible for 120MHz part), DDRC in async mode;

- Just PLL1 is used, and PLL1 is 120MHz, DDRC in sync mode.

with solution 1, you have to use both PLL0 and PLL1, and there can be additional latency when accessing the DDR if you run DDR2 in async mode, so I think you would prefer solution 2, just need one crystal, 8MHz can be selected, but DDR2 performance should be less than spec because DDR2 clock is below 125MHz. so moving to 150MHz part should be better option, though it might cost more... so I think you may start with 120MHz part and switch to the 150MHz if you need additional performance for the system and/or DDR. For 150MHz part, I think you may use a 8MHz crystal as well, but to get the 48MHz USB clock, you can not set PLL1 output 150MHz, but 144MHz instead, because of the ratio determined by SIM_CLKDIV2[USBFRAC,USBDIV].

For your question, I think you may refer to RM's "Chapter 5 Clock Distribution-> 5.7.5 DDR Memory Controller Clocking" and "Figure 25-1. Multipurpose Clock Generator (MCG) Block Diagram", you may find more details regarding CLK/CLK2x.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kan,

Thanks for sharing your knowledge. Surely it will help in the design as i am using freescale part in my project. I will go through the RM's "Chapter 5 Clock Distribution-> 5.7.5 DDR Memory Controller Clocking" and "Figure 25-1. Multipurpose Clock Generator (MCG) Block Diagram" in more details.

Thanks once again

Best Regards

Puspam Nayak