- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- SPI data transfer using DMA and PIT?

SPI data transfer using DMA and PIT?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SPI data transfer using DMA and PIT?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

SPI data transfer using DMA and PIT

uC: MPC 5643

1. Want to send 5 SPI commands for 20 times with PIT configuration.

2. Configure PIT0 for time x and PIT1 for 20 * x and send first 5 SPI commands in DMA and retrigger the same set of commands for 20 times.

3. Once 20 iterations completed, PIT1 must trigger interrupt and disable PIT

4. This I am trying to achieve without software intervention, the software intervenation will be after 20 iteration to service the interrupt.

5. I am not able to achieve this with MPC56, How can achieve this? Is there any dependency

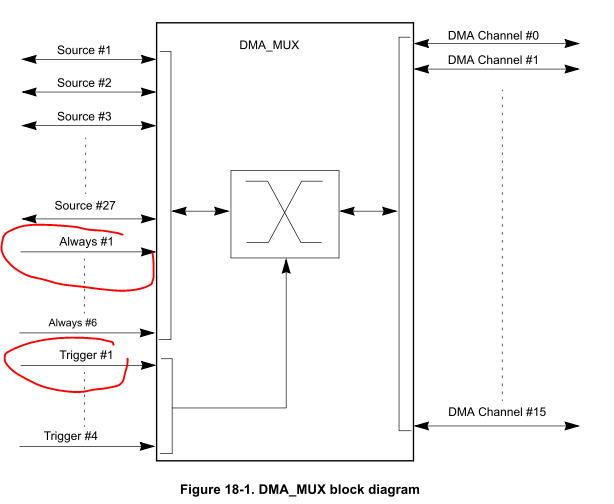

6. The PIT0 is not triggering DMA after first transfer, configured the registers in DMA_MUX, Once the PIT0 triggers DMA data transfer, do we need software intervantion or it is possible to send data transfer without software intervation?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

yes, this can be achieved.

Use "Always enabled" together with PIT Trigger.

Configure the descriptor for Always Enabled channel in a way that it starts 5 SPI transfers - you can write to DMASERQ register to enable DMA channel which sends data to SPI. You should set d_req (disable request) bit to disable DMA channel after 5 bytes.

You can enable interrupt (int_maj bit) in descriptor for Always Enabled channel, so you will get an interrupt when last 5-byte SPI transfer is triggered.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you Lukas,

I have some more questions.

1. I want to send 5 SPI Commands (May increase to 15 SPI Commands)of 32bit for 20 times, with help of PIT timer.(PIT1, PIT2)

2. For 5SPI commands, I have configured PIT2 and Source of DMA as SPI1 Tx for DMA channel 2(0,1,2)

3. To check the 20 times transfer, I have configured PIT1 with value as 20 * PIT2, PIT2 as ISR, once it raises ISR, I will read the buffer.

4. Will this work for retriggering of SPI commands or I need to do some software handling after 5SPI commands.

5. For Reception, how to handle the data (overflow) without intervention of software in between.