- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: SPI Flash memory problem

SPI Flash memory problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working with KL25Z controller.

I am using spansion SPI Flash S25FL128S

Can I directly use the low level driver to read particular register from DDR flash?

Or I have to do some initial setting?

I have directly read the RDID of flash by using SPI (Master) read.

RDID is unique IS of SPI Flash IC.

But i am getting 0x00 value in read buffer.

-Amreen

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was checking the Datasheet of the flash you are trying to interface and it looks it does not need any special configuration to read data. Like it mentions you just need to configure the SPI module in 2 of the tree different modes: mode0 or mode 3, check the section 4. Signal protocols in the document (http://www.spansion.com/Support/Datasheets/S25FL128S_256S_00.pdf)

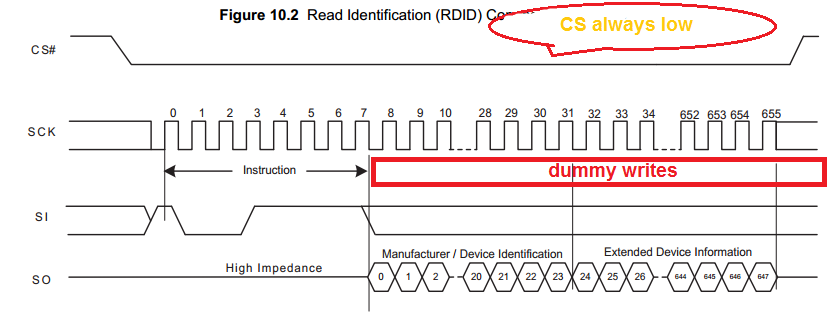

The section 10.2.2 Read identification states that if you want to read the identification of the device you just need to write the command 9F, you need to have in mind that every time you want to read something from the device you write the command and after that you need to send dummy writes to the device in order to pop the data.

Try to check the signals in an oscilloscope and add the picture.

Hope this information can help you.

Regards,

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. It would be nice!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was checking the Datasheet of the flash you are trying to interface and it looks it does not need any special configuration to read data. Like it mentions you just need to configure the SPI module in 2 of the tree different modes: mode0 or mode 3, check the section 4. Signal protocols in the document (http://www.spansion.com/Support/Datasheets/S25FL128S_256S_00.pdf)

The section 10.2.2 Read identification states that if you want to read the identification of the device you just need to write the command 9F, you need to have in mind that every time you want to read something from the device you write the command and after that you need to send dummy writes to the device in order to pop the data.

Try to check the signals in an oscilloscope and add the picture.

Hope this information can help you.

Regards,

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. It would be nice!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello adriancano,

Thanks for reply it was really helpful.

I have some doubt in it.

I am working with KL25Z128VLH4 controller using CW 10.3.

I have generated code for SPI0 (mode 0) using PE in CW 10.3.

As I said I was not able to read the ID from Spansion memory IC.

My code was not working.

But refereed from the "READ_ID Command Sequence" .

I disable the CS pin from SPI setting (All other parameters are same) and make CS pin as "BitIO_LDD"

And I Clear the bit before reading ID and again set it.

Now its working.I can read RDID of memory IC.

When I tested SPI communication on two controllers one as a master and other as a slave its working fine.

Is this setting of CS (Chip select) pin as a "BitIO_LDD" is required for all types of SPI communication from controller to any SPI based device.

or this setting of CS is required for all types of Flash?

or It is related to this spansion flash only?

Also the mentioned flash S25FL128S is supports DDR option.

Is the use of this DDR option depends on the controller KL25Z128VLH4.

What parameters do i need to consider for that?

-Amreen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is not exclusive for the Flash memories, it is a very recurrent practice when you are using SPI communication and you want to control and ensure when the CS signal is going low or high. It is used for the SPI protocol itself, this is because is the CS signal is the one that indicates the start and the end of the frame.

As in the datasheet of the flash says the DDR option is also supported, in the section 4.1.2 Double Data Rate (DDR) mentions: “Mode 0 and Mode 3 are also supported for DDR commands. In DDR commands, the instruction bits are always latched on the rising edge of clock, the same as in SDR commands. However, the address and input data that follow the instruction are latched on both the rising and falling edges of SCK.” The problem here is that the SPI module in the Kinetis KL (nor Kinetis K) devices is a simple SPI module and it does not support this type of frame where the data is latched on the rising and falling edges, it only supports one edge for the data.

I hope this information solves your queries.

Regards,

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. It would be nice!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I know that CS should go low while transmission of data and again high after data transmission.

When I used PE generated code my CS bit is going low for every byte and again high after byte transfer.

But from memory IC datasheet the CS should be Low for whole data transfer. So I made it as BitIO_LDD and clear and set pin before and after data send. With this my code is working.

I am cleared about the DDR concept.

Thanks,

Amreen