- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Potential Problem with MCGFFCLK in K64, K65, K66

Potential Problem with MCGFFCLK in K64, K65, K66

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Potential Problem with MCGFFCLK in K64, K65, K66

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All

I haven't been able to use MCGFFCLK from the slow clock on these part, although it works from the divided FLL external clock.

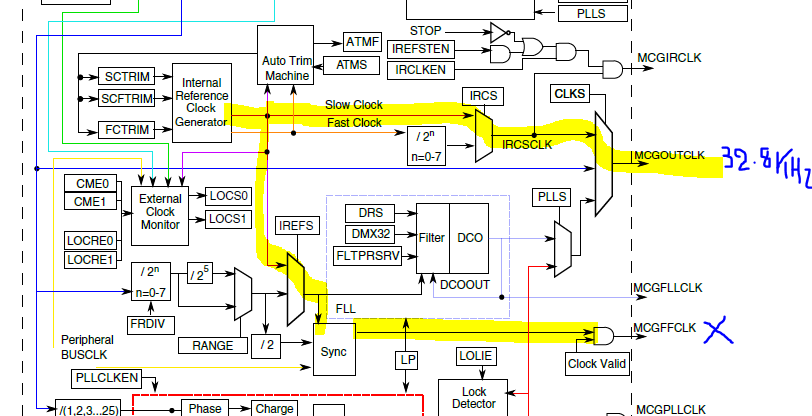

Here I have IREFS set to '1' but there is no output on MCGFFCLK (that is, peripherals clocked from it don't count). The slow clock is available as shown by the physically measured 32.8kHz on the CLKOUT pin.

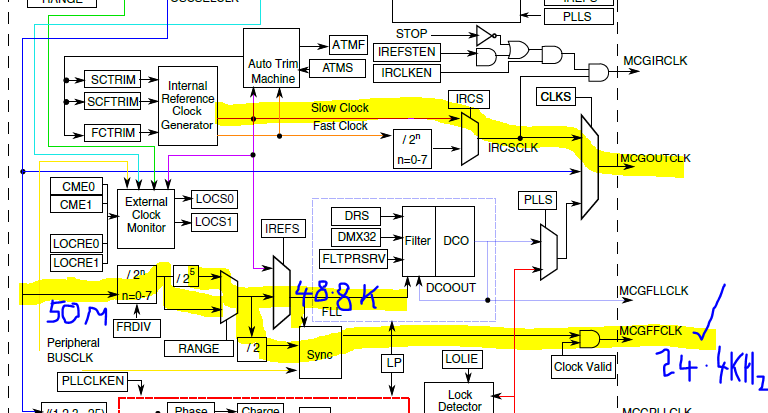

On a K64 I have 50Mhz external clock divided by 1024 at the non-selected input to the FLL and, as shown in the next diagram where I simply set IREFS back to '0'

the internal peripherals on MCGFFCLK are correctly clocked (and count) at 24.4kHz.

The design is different to other parts with the "Sync" block having three inputs, one from the FLL input, one from the external reference input divided by 2 and one from the bus clock (60Mhz in both cases).

Presumably the clock is not being gated out due to the clock valid bit not being set.

Therefore:

- why does the 48kHz external clock input work but the internal 32.8kHz not?

- what would cause the clock validity check to not allow it? (Adjusting the external reference clock divide didn't change anything)

- is there some trick needed that is not described in the manual?

- has the operation been verified?

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please notice:

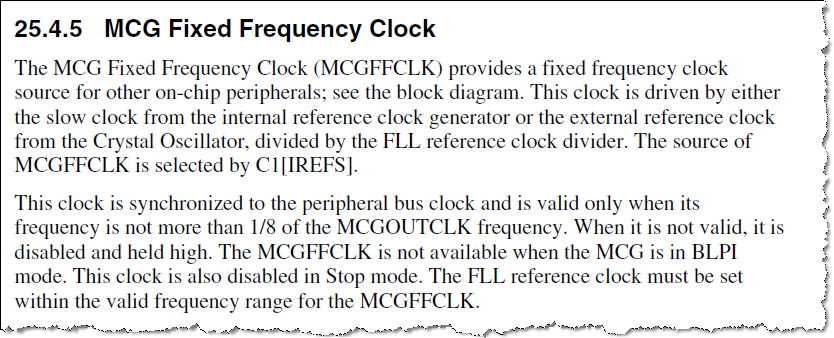

This clock is synchronized to the peripheral bus clock and is valid only when its frequency is not more than 1/8 of the MCGOUTCLK frequency. When it is not valid, it is disabled and held high.

Please configure MCGOUTCLK to a higher frequency

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Robin

I have 120MHz for MCGOUTCLK (my diagrams are wrong - I thought I was showing the CLKOUT [which is set to IRC 32kHz to verify that it is oscillating]).

Therefore 32kHz < 120MHz/8 [32kHz < 15MHz]

Since there is no problem with 48kHz (also < 15Mhz and > IRC 32k) I still don't see why 48kHz is valid but 32kHz is not.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark,

Have you check the value of MCG_S[IREFST] after set MCG_C1[IREFS]?

Which MCG mode are you testing with IREFS set to '1'?

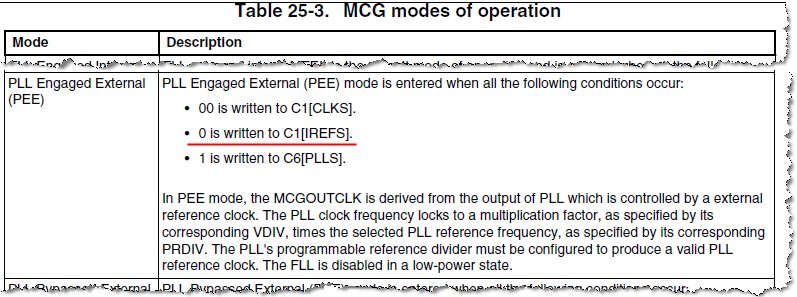

How did you configure 120MHz for MCGOUTCLK? When PEE mode is selected, the IREFS shoud be set to '0'.

I am using FEI mode and select MCGFFCLK(32.768kHz IRC) as FTM clock source, the FTM is able to output PWM.

Please select the MCG mode which IREFS=1, and then test if the FTM module is able to work.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Robin

When I set IREFS I see the value correctly reflected in IREFST.

MCGOUTCLK is from the PLL at 120MHz.

In this state I can change IREFS between 0 and 1 without affecting the PLL operation (which may contradict the PEE requirement). With IREFS at 0 the FTM operates from MCGFFCLK; with IREFS at 1 the FTM doesn't operate (although 32kHz IRC is oscillating as measured on CLKOUT pin).

I will try with other MCGOUTCLK configurations to see whether there is a restriction in PEE.

If you have a working binary for FRDM-K64F or FRDM-K66F could you post it so that I can load it and compare?

Thanks

Mark

![MCG_S[IREFST].png MCG_S[IREFST].png](/t5/image/serverpage/image-id/62229i2FF4067EDF653740/image-size/large?v=v2&px=999)