- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Not satisfied with noise on K22FN

Not satisfied with noise on K22FN

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kinetis-Team,

i have a complain about the Kinetis MCUs, K22FN512.

I did all the art for a good adc result:

1. Voltages are highly stable and noise free

2. ADC inputs are driven by ADC-Driving OpAmps

3. Reference voltage is stable.

4. Solid GND Plane

However, I get noise on my result:

Its 12 binary digits noise at 12 Bit conversion. Thats too much for me, as I want to use the adc in a control loop.

Its approx 0,2%-0,3% noise in the measurement range but this is too much for a good adc, like the datasheet promises.

What can I do better to improve my performance? I want to switch to Kinetis KV44. Will there be better results?

I'm pretty sure you won't do a new revision, but please make more sure next time, you get a good and stable adc result.

Other people also complained with similar results.

https://community.nxp.com/thread/322988

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks Ma Hui for your support. I checked that I followed all the recommended steps.

What I tried and did not help:

Current state: 0.15% noise

Practically, I have the same problem as you describe in the 19 counts off example.

-Replaced switching regulator with lab power supply. Same issue.

-Vss&Vref are already highly bypassed.

-No chance to place ferrite beads in the design. However, as no more switching device is left, nor any noise can be seen with 12 bit oscilloscope, i guess this will not make a difference.

-played with sample time: No difference. ADC Channels are actively driven by opamp, so i guess this won't be an issue anyhow.

-reduce the clk divder highly. Same issue.

What helped (if you have same problem):

Changed clk source from Bus Clk to Oscillator Clock: OSCERCLK

So I recommend using OSCERCLK with 8MHz.

Now i have 0.07% noise, which meets the Freescale minimum spec of 10.4 effective bits.

How to calulate: 1/2^ENOB=0,074%

What I guess (it's just a guess, based on the made experience): The Busclock is not stable enough, has some gitter? I use standard 120MHz option for KN512. When I change the frequency from 10MHz to 5MHz same issue.

In case everything else fails:

Oversampleing and averaging.

Generally I would like to have a more stable adc.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update: The KE1xF seems to have an decent ADC. Guess, I will use that part.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

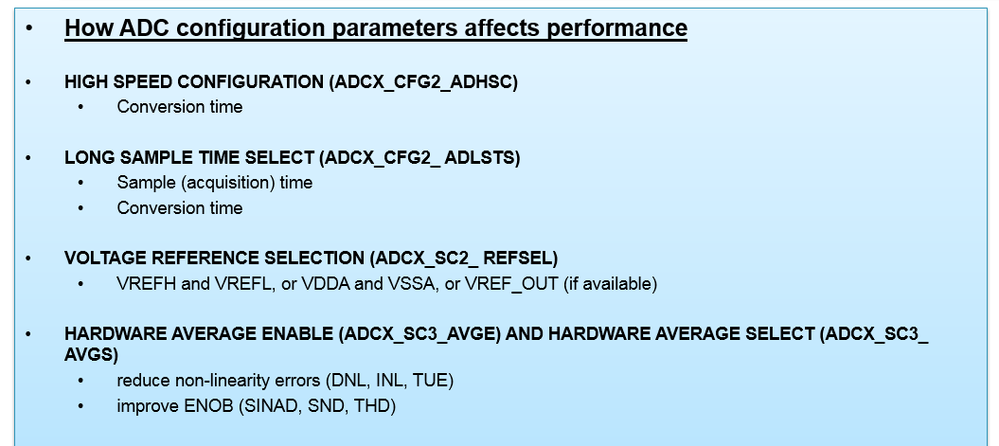

There with some suggestions about how to get better performance of Kinetis SAR ADC:

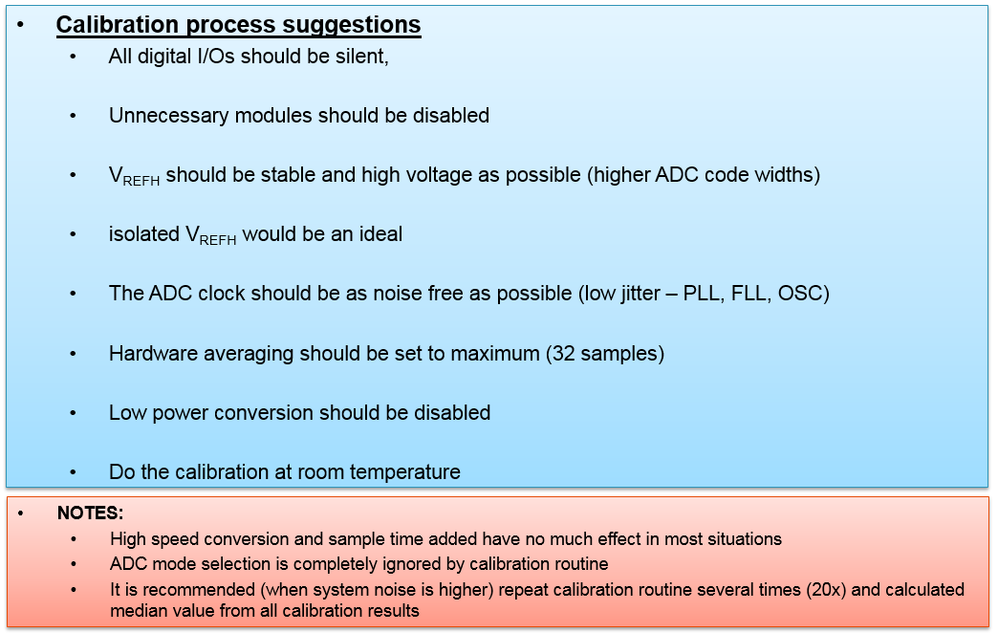

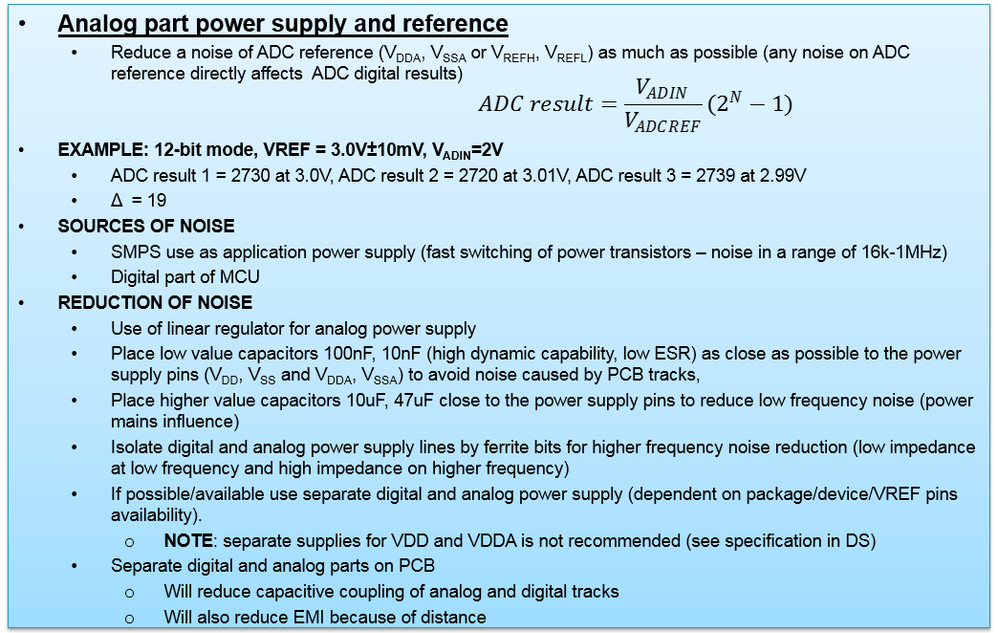

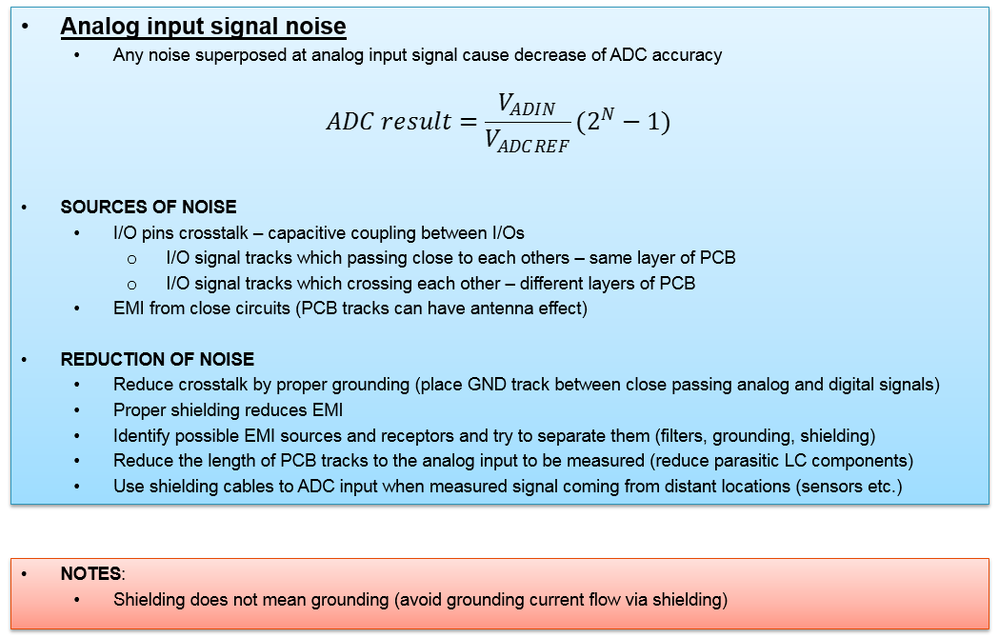

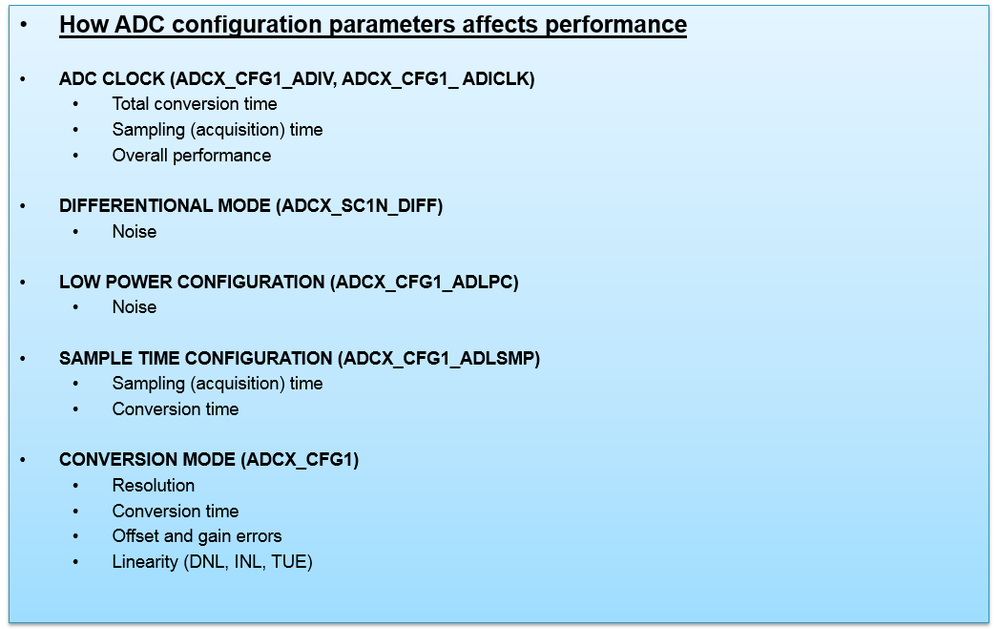

[ADC Calibration]

[Hardware Configuration]

[ADC Configuration]

There also with an application note AN4373 about SAR ADC cookbook, please check here for the detailed info.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks Ma Hui for your support. I checked that I followed all the recommended steps.

What I tried and did not help:

Current state: 0.15% noise

Practically, I have the same problem as you describe in the 19 counts off example.

-Replaced switching regulator with lab power supply. Same issue.

-Vss&Vref are already highly bypassed.

-No chance to place ferrite beads in the design. However, as no more switching device is left, nor any noise can be seen with 12 bit oscilloscope, i guess this will not make a difference.

-played with sample time: No difference. ADC Channels are actively driven by opamp, so i guess this won't be an issue anyhow.

-reduce the clk divder highly. Same issue.

What helped (if you have same problem):

Changed clk source from Bus Clk to Oscillator Clock: OSCERCLK

So I recommend using OSCERCLK with 8MHz.

Now i have 0.07% noise, which meets the Freescale minimum spec of 10.4 effective bits.

How to calulate: 1/2^ENOB=0,074%

What I guess (it's just a guess, based on the made experience): The Busclock is not stable enough, has some gitter? I use standard 120MHz option for KN512. When I change the frequency from 10MHz to 5MHz same issue.

In case everything else fails:

Oversampleing and averaging.

Generally I would like to have a more stable adc.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just checked with the datasheets: The ADC of the Kinetis just seems so bad, as i measured.

If you look at STM parts, eg. STM32F334, they have a 10dB better SNR ADC build in. I strongly recommend to improve the ADC on the Kinetis devices.

The KV4x 4MSPS ADC gets even worse: It has 9.1 effective bits. Oversampling by a factor of 4 increases the effective bits by 1. This means that that ADC is useless in the KV4x. I need a better ADC on the KVx series!

The KV5 ADC is better, but I cannot afford double the price...