- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- MKM34 WDOG behaviour after power on reset

MKM34 WDOG behaviour after power on reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

I have an own pcb with the MKM34 on it. My software is running well so now I want to implement the WDOG. However, I found out that after a power on reset the WDOG behaves different to what I expected with the default settings described in the manual.

According to the reset values the WDOG is enabled with the clock source from LPO and a timeout value of 0x4C4B40 which should be a timeout of 83 minutes.

But with this small piece of code which is executed immedeately after reset without any other code in between I found out that the WDOG generates a reset 200 µs after power on reset.

void Startup(void)

{

// configure Port B3 as output

SIM->SCGC5 |= SIM_SCGC5_PORTB_MASK;

PORTB->PCR[3] = 0x100;

GPIOB->PDDR |= 0x8;

// set Port B3

GPIOB->PSOR |= 0x8;

while (TRUE) ;

}

I confirmed that it is really a WDOG by setting port B3 only if RCM_SSRS0_SWDOG_MASK was set.

Does anybody have an explanation for this?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raul,

You must unlock the registers within WCT { 256 bus clock cycles } after system reset, failing which the WDOG issues a reset to the system... For more details, refer to MKM34Z128 reference manual, section Watchdog configuration time.

The WCT of 256 bus clock cycles for 1MHz bus clock equals to 256 us timeout.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

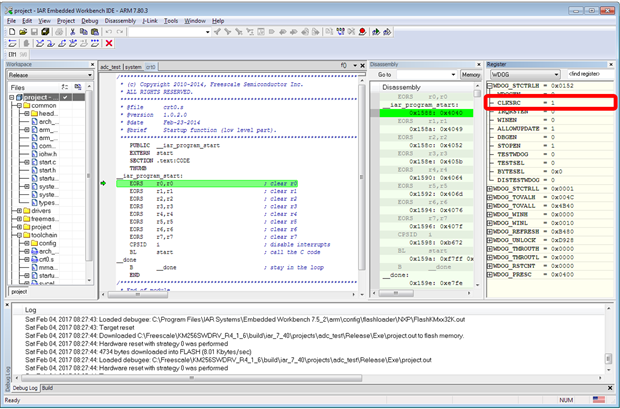

after device power up the WDOG_STCTRLH[CLKSRC] is set to 1 meaning that WDOG is sourced from alternate clock source (32.768 kHz RTC oscillator) after power on reset. I will ask our documentation team to change WDOG_STCTRLH[CLKSRC] reset value from 0 to 1 in next revision of the reference manual.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

Thank you for the information. But this should give a timeout of 152 seconds after power on reset whereas I observed 200 µs. Do you know the reason for this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raul,

I don't have any quick explanation for such short timeout.

Have you populated external 32.768kHz crystal on your PCB - if not please refer to: Watchdog configuration in MKMxxZxxACxx5RM.

You can also run wdog_test example from Kinetis-M bare metal drivers on your board to reveal potential issue in code.

If none of suggestions work for you please share your watchdog configuration example with me so I can run it on my TWR board.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

My board has an external 32.768 kHz crystal.

I haven't made any WDOG configuration since I wanted to see the WDOG behavior after power on. So the piece of code in my first post is really all what is running on my board. The Startup() routine is called directly by the reset vector.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raul,

You must unlock the registers within WCT { 256 bus clock cycles } after system reset, failing which the WDOG issues a reset to the system... For more details, refer to MKM34Z128 reference manual, section Watchdog configuration time.

The WCT of 256 bus clock cycles for 1MHz bus clock equals to 256 us timeout.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

It seems that I have missed that point. Thank you for your explanation, that's the reason for the behaviour.

Kind regards,

Raul