- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- MK22DX256VMC5 VOUT33 output not good when VREGIN changes

MK22DX256VMC5 VOUT33 output not good when VREGIN changes

MK22DX256VMC5 VOUT33 output not good when VREGIN changes

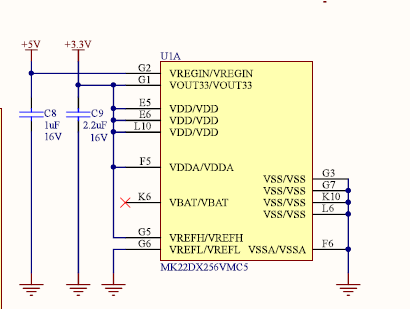

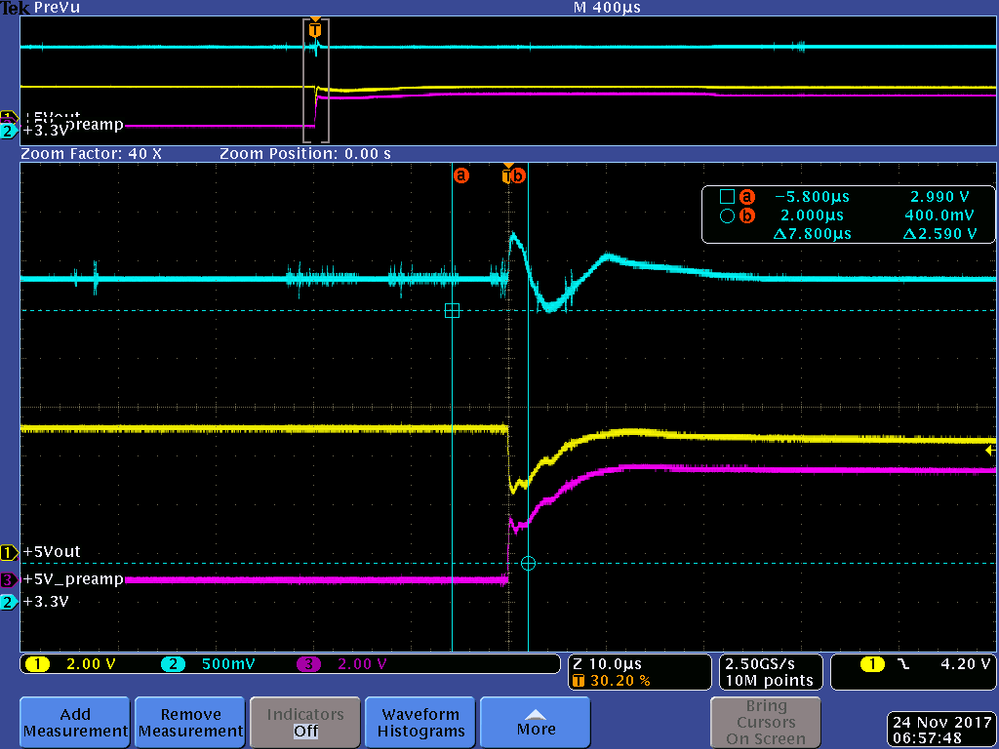

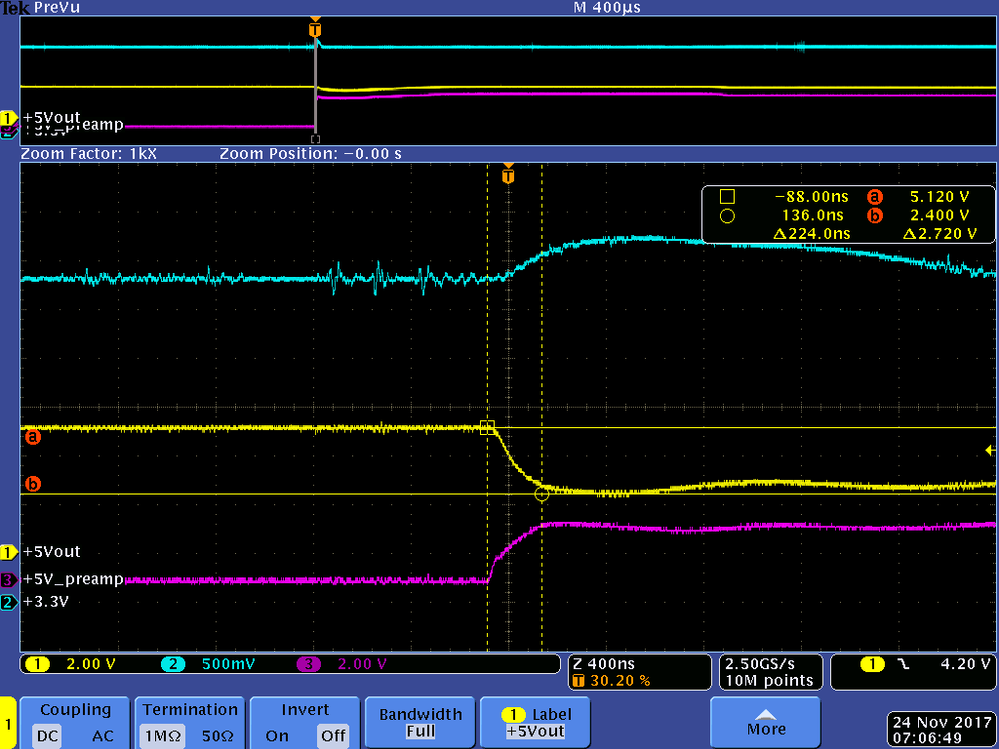

We are using the internal regulator, and VOUT33 output voltage(+3.3V on the schematic) rise to 3.8V when there is an fast voltage dip on VREGIN("+5V" on the sch, "+5Vout" in the graph), see below for the sch and graph.

We guess that is because of the PSRR, but we cannot find the PSRR parameter in the datasheet...

What is the root cause and how can we improve the performance?

Hi,

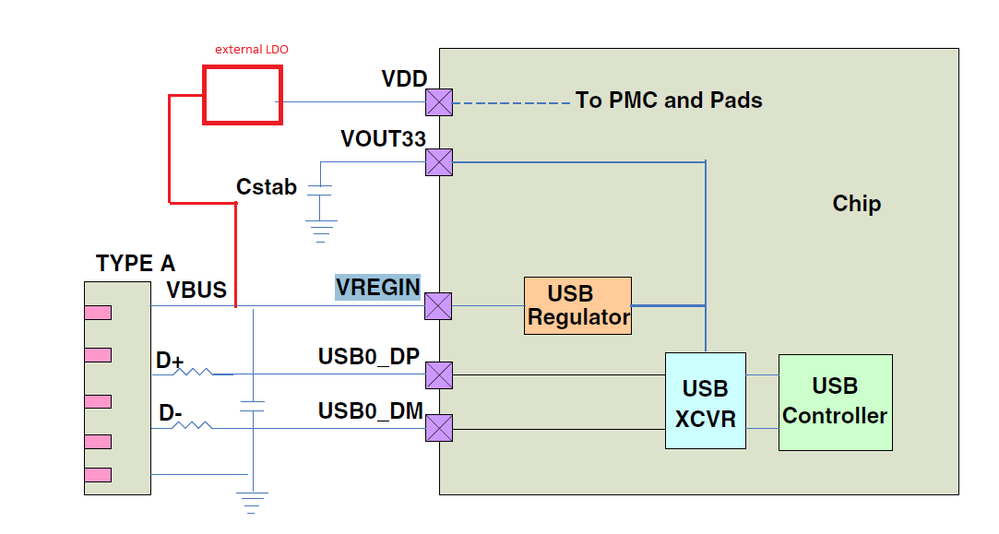

If you use USB, you have to use internal regulator to provide power for internal USB transceiver. In the case, you can connect VREGIN to 5V, connect the VOUT33 pin to a 2.2uF capacitor, connect the VDD pins to external 3.3V power supply, you can get 3.3V power supply with an external LDO or general regulator such as LM1117-3.3V device.

Hope it can help you

BR

'XiangJun Rong

Hi, HuiJie,

If you use external LDO to provide power for the K22, internal regulator is NOT used, in the case, when USB is not used in the application, it is recommended to

connect VREGOUT and VREG_INx together and tie to ground

through a 10kΩ resistor. Do not tie directly to ground, as this

causes a latch-up risk. For systems where only one of the

VREG_INx pins is ever used, it is also recommended to

connect the two VREG_INx pins together.

BR

Xiangjun rong

Hi Xiangjun,

Thanks for the reply.

But we will use the USB function, and if we use the external LDO, how to treat with VREGIN and VOUT3.3?

Hi, HuJie,

The VDD power supply ranges from -0.3V to 3.8V, so I think it is okay.

As you know that the VOUT33 is the internal regulator output, the internal regulator inputs 5V, it is not related to the PSRR(power supply rejection rate). how about using different capacitor on the VOUT33 pin, which can ranges from 1.76uF to 8.16uF.

Hope it can help you

BR

Xiangjun Rong

Hi Xiangjun,

Thanks for your quickly reply.

I have tried your suggestion to add additional capacitors to C9 and made it as 4.4uf, 6.6uf..., and did the test with the same method, but there was no improvement.

Based on the test, the fluctuation of the VOUT3.3 is reduced when the voltage dip is reduced and seams not so related to the capacitor, which meets the requirement of the datasheet.

Here is the question,

1) Do you have the PSRR of the regulator?

2) Is there any additional requirement for the VREGIN that related with VOUT3.3?

Hi Xiangjun,

Is there any update?

regarding the internal regulator,

We design the MCU as a USB device, if we use an external LDO, how to treat the VREGIN and VOUT3.3?

Do we MUST to, as the below picture,

1) connect VREGIN to VBUS

2) add Cstab to VOUT3.3(2.2uf? can that capacitor be used a smaller value one?)

3) connect VDD to external LDO output

Can we ONLY use the external LDO and just leave away(just float the VREGIN and VOUT3.3) the internal regulator?