- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: MK20 vs PK20

MK20 vs PK20

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have developed a application with K20 some years ago. I have about 100 devices thas is woriking fine. I have just mounted other batch and devices don't work.

I have noted that old items have PK20N512VLL100 (mask: 2N30D) and new ones have MK20DN512VLL10 (mask: 5N22D).

I can program devices but the SW don't run. In debug mode it goes in:

PE_ISR(Cpu_Interrupt)

{

/* This code can be changed using the CPU component property "Build Options / Unhandled int code" */

PE_DEBUGHALT();

return;

}

It seems an unmanaged interrupt, but I check it and all seems OK.

I need some helps to find the trouble and fix it.

Mirko

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mirko Manetti,

I have found the problem, your hardfault happens on MK20DN512VLL10 (mask: 5N22D), is that right?

It is caused by the different silicon reversion:

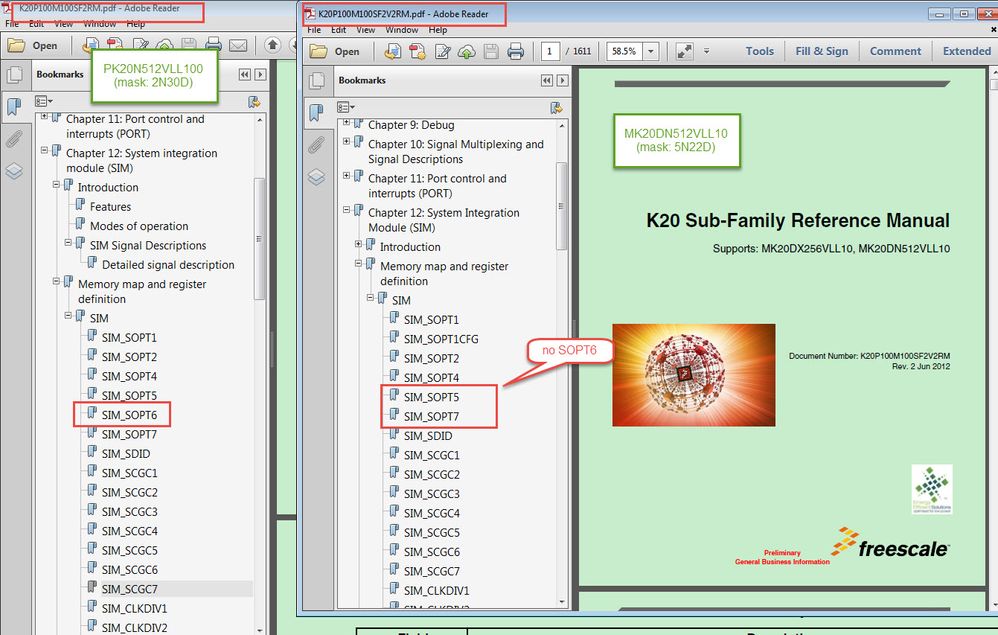

PK20N512VLL100 (mask: 2N30D): rev1, the reference manual is K20P100M100SF2RM.pdf

MK20DN512VLL10 (mask: 5N22D): rev 2, the reference manaul is K20P100M100SF2V2RM.pdf

You can find the reason from this shortscreen:

MK20DN512VLL10 (mask: 5N22D) don't have the SIM_SOPT6, so when you operate it, it will enter in hardfault.

About the difference of 100M rev1 and rev2, you can refer to our application AN4445.pdf.

http://cache.nxp.com/files/32bit/doc/app_note/AN4445.pdf?fsrch=1&sr=1&pageNum=1

So you can't use the PK20N512VLL100 (mask: 2N30D) code in MK20DN512VLL10 (mask: 5N22D) directly, there has a lot of difference.

Wish it helps you!

If you still have question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mirko Manetti,

Please refer to this post to check which code cased your hard fault:

https://mcuoneclipse.com/2012/11/24/debugging-hard-faults-on-arm-cortex-m/

After you check it, please tell me the code caused the problem, this will help me to analyze it.

Besides, please also check your hardware, add the 4.7K to 10K external pullup resistor in the NMI pin.

Waiting for your reply!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jingjing,

I'll try and follow your indication.

Mirko

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK, waiting for your reply!

Jingjing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jingjing,

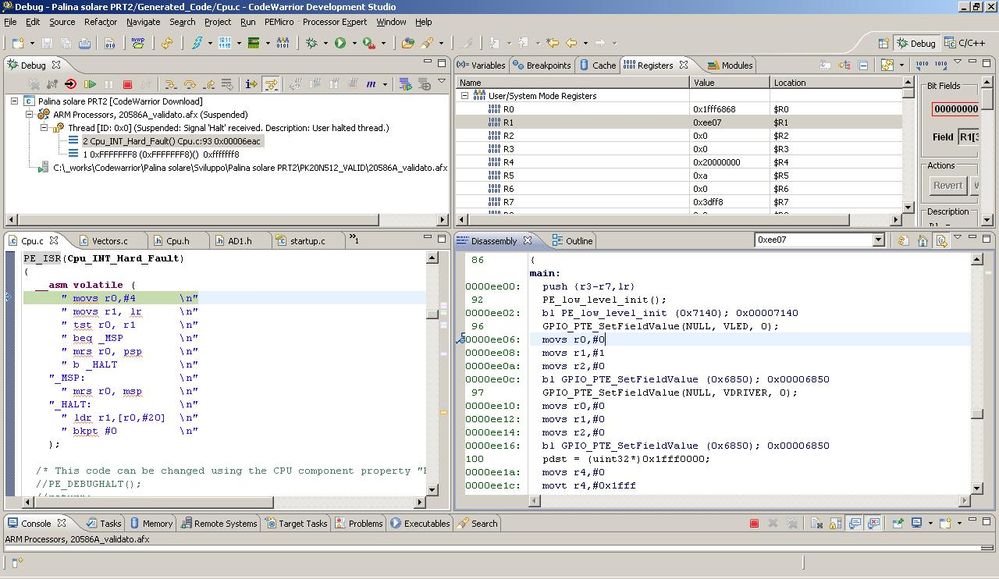

I have just check my application fault according your indication but I can't find the reason of the hardware fualt. It seems a "GPIO_PTE_SetFieldValue" call the reason but If I put a breakpoint at "GPIO_PTE_SetFieldValue", the program doesn't arrive at this breakpoint, so the truoble should be in PE_low_level_init():

void PE_low_level_init(void)

{

/* Initialization of the SIM module */

//#ifdef NO_INIT

/* PORTA_PCR4: ISF=0,MUX=7 */

PORTA_PCR4 = (uint32_t)((PORTA_PCR4 & (uint32_t)~0x01000000UL) | (uint32_t)0x0700UL);

/* SIM_SOPT6: RSTFLTEN=0,RSTFLTSEL=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_SOPT6 = (uint32_t)0x00UL; /* Set reset pin filter */

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= (uint32_t)0x04UL;

/* Initialization of the MPU module */

/* MPU_CESR: SPERR=0,VLD=0 */

MPU_CESR &= (uint32_t)~0xF8000001UL;

//#endif

/* Initialization of the AIPS0 module */

/* AIPS0_MPRA: MTR0=1,MTW0=1,MPL0=1,MTR1=1,MTW1=1,MPL1=1,MTR2=1,MTW2=1,MPL2=1,MTR4=0,MTW4=0,MPL4=0,MTR5=0,MTW5=0,MPL5=0 */

AIPS0_MPRA = (uint32_t)((AIPS0_MPRA & (uint32_t)~0x7700UL) | (uint32_t)0x77700000UL);

/* AIPS0_PACRA: SP0=0,WP0=0,TP0=0,SP4=0,WP4=0,TP4=0 */

AIPS0_PACRA &= (uint32_t)~0x70007000UL;

/* AIPS0_PACRB: SP0=0,WP0=0,TP0=0,SP1=0,WP1=0,TP1=0,SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0 */

AIPS0_PACRB &= (uint32_t)~0x77007700UL;

/* AIPS0_PACRE: SP0=0,WP0=0,TP0=0,SP1=0,WP1=0,TP1=0,SP4=0,WP4=0,TP4=0 */

AIPS0_PACRE &= (uint32_t)~0x77007000UL;

/* AIPS0_PACRF: SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0,SP7=0,WP7=0,TP7=0 */

AIPS0_PACRF &= (uint32_t)~0x7707UL;

/* AIPS0_PACRG: SP2=0,WP2=0,TP2=0,SP5=0,WP5=0,TP5=0,SP6=0,WP6=0,TP6=0,SP7=0,WP7=0,TP7=0 */

AIPS0_PACRG &= (uint32_t)~0x00700777UL;

/* AIPS0_PACRH: SP0=0,WP0=0,TP0=0,SP1=0,WP1=0,TP1=0,SP3=0,WP3=0,TP3=0,SP5=0,WP5=0,TP5=0,SP6=0,WP6=0,TP6=0 */

AIPS0_PACRH &= (uint32_t)~0x77070770UL;

/* AIPS0_PACRI: SP0=0,WP0=0,TP0=0,SP1=0,WP1=0,TP1=0,SP5=0,WP5=0,TP5=0,SP7=0,WP7=0,TP7=0 */

AIPS0_PACRI &= (uint32_t)~0x77000707UL;

/* AIPS0_PACRJ: SP0=0,WP0=0,TP0=0,SP1=0,WP1=0,TP1=0,SP2=0,WP2=0,TP2=0,SP3=0,WP3=0,TP3=0,SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0 */

AIPS0_PACRJ &= (uint32_t)~0x77777700UL;

/* AIPS0_PACRK: SP2=0,WP2=0,TP2=0 */

AIPS0_PACRK &= (uint32_t)~0x00700000UL;

/* AIPS0_PACRM: SP1=0,WP1=0,TP1=0,SP2=0,WP2=0,TP2=0,SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0,SP6=0,WP6=0,TP6=0,SP7=0,WP7=0,TP7=0 */

AIPS0_PACRM &= (uint32_t)~0x07707777UL;

/* AIPS0_PACRN: SP2=0,WP2=0,TP2=0,SP3=0,WP3=0,TP3=0,SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0 */

AIPS0_PACRN &= (uint32_t)~0x00777700UL;

/* AIPS0_PACRO: SP2=0,WP2=0,TP2=0,SP3=0,WP3=0,TP3=0,SP4=0,WP4=0,TP4=0 */

AIPS0_PACRO &= (uint32_t)~0x00777000UL;

/* AIPS0_PACRP: SP4=0,WP4=0,TP4=0,SP5=0,WP5=0,TP5=0,SP6=0,WP6=0,TP6=0 */

AIPS0_PACRP &= (uint32_t)~0x7770UL;

/* Initialization of the AIPS1 module */

/* AIPS1_MPRA: MTR0=1,MTW0=1,MPL0=1,MTR1=1,MTW1=1,MPL1=1,MTR2=1,MTW2=1,MPL2=1,MTR4=0,MTW4=0,MPL4=0,MTR5=0,MTW5=0,MPL5=0 */

AIPS1_MPRA = (uint32_t)((AIPS1_MPRA & (uint32_t)~0x7700UL) | (uint32_t)0x77700000UL);

/* AIPS1_PACRE: SP4=0,WP4=0,TP4=0 */

AIPS1_PACRE &= (uint32_t)~0x7000UL;

/* AIPS1_PACRF: SP4=0,WP4=0,TP4=0 */

AIPS1_PACRF &= (uint32_t)~0x7000UL;

/* AIPS1_PACRG: SP1=0,WP1=0,TP1=0 */

AIPS1_PACRG &= (uint32_t)~0x07000000UL;

/* AIPS1_PACRH: SP0=0,WP0=0,TP0=0,SP3=0,WP3=0,TP3=0 */

AIPS1_PACRH &= (uint32_t)~0x70070000UL;

/* AIPS1_PACRJ: SP4=0,WP4=0,TP4=0 */

AIPS1_PACRJ &= (uint32_t)~0x7000UL;

/* AIPS1_PACRN: SP2=0,WP2=0,TP2=0 */

AIPS1_PACRN &= (uint32_t)~0x00700000UL;

/* AIPS1_PACRP: SP6=0,WP6=0,TP6=0 */

AIPS1_PACRP &= (uint32_t)~0x70UL;

/* Initialization of the PMC module */

/* PMC_LVDSC1: LVDACK=1,LVDIE=0,LVDRE=1,LVDV=0 */

PMC_LVDSC1 = (uint8_t)((PMC_LVDSC1 & (uint8_t)~(uint8_t)0x23U) | (uint8_t)0x50U);

/* PMC_LVDSC2: LVWACK=1,LVWIE=0,LVWV=0 */

PMC_LVDSC2 = (uint8_t)((PMC_LVDSC2 & (uint8_t)~(uint8_t)0x23U) | (uint8_t)0x40U);

/* PMC_REGSC: TRAMPO=0,??=0,BGBE=0 */

PMC_REGSC &= (uint8_t)~(uint8_t)0x13U;

/* MC_PMPROT: ??=0,??=0,AVLP=0,ALLS=0,??=0,AVLLS3=0,AVLLS2=0,AVLLS1=0 */

MC_PMPROT = (uint8_t)0x00U; /* Setup Power mode protection register */

/* Common initialization of the CPU registers */

/* NVICIP20: PRI20=0 */

NVICIP20 = (uint8_t)0x00U;

/* ### GPIO_LDD "GPIO_PTA" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)GPIO_PTA_Init(NULL);

/* ### GPIO_LDD "GPIO_PTC" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)GPIO_PTC_Init(NULL);

/* ### GPIO_LDD "GPIO_PTD" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)GPIO_PTD_Init(NULL);

/* ### GPIO_LDD "GPIO_PTE" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)GPIO_PTE_Init(NULL);

/* ### TimerUnit_LDD "TU1" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)TU1_Init(NULL);

/* ### TimerUnit_LDD "TU2" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)TU2_Init(NULL);

/* ### Serial_LDD "U0_GPRS" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)U0_GPRS_Init(NULL);

/* ### Serial_LDD "U3_console" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)U3_console_Init(NULL);

/* ### Serial_LDD "U4_SLAVE" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)U4_SLAVE_Init(NULL);

/* ### SPIMaster_LDD "SM1" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)SM1_Init(NULL);

/* ### SPIMaster_LDD "SM2" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)SM2_Init(NULL);

/* ### SPIMaster_LDD "SM3" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)SM3_Init(NULL);

/* ### RTC_LDD "RTC" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)RTC_Init(NULL, TRUE);

/* ### I2C_LDD "I2C" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)I2C_Init(NULL);

/* ### TimerUnit_LDD "TU3" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)TU3_Init(NULL);

/* ### WatchDog_LDD "WDog2" component auto initialization. Auto initialization feature can be disabled by component property "Auto initialization". */

(void)WDog2_Init(NULL);

/* Enable interrupts of the given priority level */

Cpu_SetBASEPRI(0U);

}

a StepByStep debug fault line is:

SIM_SCGC7 |= (uint32_t)0x04UL;

but I don't understand the reason of the fault.......

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mirko,

It seems you didn't enable the PORTE clock, please enable the PORTE clock before you do the PORTE operation.

Please add this code:

SIM_SCGC5|=SIM_SCGC5_PORTE_MASK;

Wish it helps you!

If you still have question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jingjing,

I have just add suggested code but anything change and sw still doesn't work:

void PE_low_level_init(void)

{

/* Initialization of the SIM module */

//#ifdef NO_INIT

SIM_SCGC5|=SIM_SCGC5_PORTE_MASK;

/* PORTA_PCR4: ISF=0,MUX=7 */

PORTA_PCR4 = (uint32_t)((PORTA_PCR4 & (uint32_t)~0x01000000UL) | (uint32_t)0x0700UL);

/* SIM_SOPT6: RSTFLTEN=0,RSTFLTSEL=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_SOPT6 = (uint32_t)0x00UL; /* Set reset pin filter */

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= (uint32_t)0x04UL;

/* Initialization of the MPU module */

/* MPU_CESR: SPERR=0,VLD=0 */

MPU_CESR &= (uint32_t)~0xF8000001UL;

.........

Steb by step debugging fails at:

SIM_SCGC7 |= (uint32_t)0x04UL;

So this instruction o the previews one are suspected.....

anyway if I skip:

| SIM_SOPT6 = (uint32_t)0x00UL; | /* Set reset pin filter */ |

It seems work properly.....

it seems me very strange!

Mirko

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mirko Manetti,

I have found the problem, your hardfault happens on MK20DN512VLL10 (mask: 5N22D), is that right?

It is caused by the different silicon reversion:

PK20N512VLL100 (mask: 2N30D): rev1, the reference manual is K20P100M100SF2RM.pdf

MK20DN512VLL10 (mask: 5N22D): rev 2, the reference manaul is K20P100M100SF2V2RM.pdf

You can find the reason from this shortscreen:

MK20DN512VLL10 (mask: 5N22D) don't have the SIM_SOPT6, so when you operate it, it will enter in hardfault.

About the difference of 100M rev1 and rev2, you can refer to our application AN4445.pdf.

http://cache.nxp.com/files/32bit/doc/app_note/AN4445.pdf?fsrch=1&sr=1&pageNum=1

So you can't use the PK20N512VLL100 (mask: 2N30D) code in MK20DN512VLL10 (mask: 5N22D) directly, there has a lot of difference.

Wish it helps you!

If you still have question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Now it's work! thank you!