- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis K65 interrupt nesting

Kinetis K65 interrupt nesting

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Kinetis K65 interrupt nesting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using one of the PIT channel as a base timer interrupt for my scheduler. Is there a way or workaround to allow the same interrupt to come again when the interrupt is getting executed? I want to implement a task overrun based on this feature. Otherwise please suggest a better way of doing it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

When you are running in the interrupt context the interrupt mask level will be set to the interrupt's priority. If you thus clear the original interrupt in the peripheral and allow it to fire again it won't be able to pre-empt the original interrupt routine unless it has a higher priority.

You could thus increase the interrupt priority of the peripheral in the first interrupt handler to make it able to interrupt again.

Regards

Mark

Complete Solutions and technical support for professional Kinetis developments: http://www.utasker.com/kinetis.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thanks for the response. My configurations are as per below:

1. During Initialization

1.1 Configure PIT channel 2 interrupt (5 milliseconds periodicity)

1.2 Set Priority group in (SCB AIRCR register) to 3

1.3 Set NVIC priority register to have a value of 0x40

1.4 Start the PIT channel

2. In interrupt processing

2.1 Clear PIT Channel 2 status

2.2 Set NVIC priority register to have a value of 0x20 to increase the interrupt priority to allow the same interrupt to come again

2.3 Interrupt or task processing

2.4 Set NVIC priority register to have a value of 0x40 to bring back the priority to initial set value

2.5 exit from the interrupt

In the step 2.3, i create a delay of 10 milliseconds and expect the processor control to hit the entry point of the interrupt while it is within step 2.3. Please let me know if the expected behavior is possible with this microcontroller?

Regards,

Kishore

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

That sounds right. Simplest thing to do is try it and then you can be sure.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have already tested the sequence, but I did not succeed in getting a overrun of the interrupt.

Regards,

Kishore

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kishore

Unfortunately I was probably wrong about the interrupt vector priority being able to interrupt itself.

When the PIT channel fires and its vector is taken the processor sets its "active interrupt vector" to its reference and although it is possible to get the second (higher priority) vector as a "pending vector" (see System Control Block's ICSR register where both are shown) the Cortex M4 doesn't look to allow a pending vector to be taken that is the same as the presently active vector.

As long as the pending vector is not equal to the active vector and the pending source's priority is higher than the active vector it is then indeed taken.

The only way that I can see the second being taken is to exit from its interrupt context, which sets the active vector back to zero and then it immediately re-enters.

Therefore it looks like you need to leave the initial interrupt context eg. using BX LR, which means that it is more complicated and requires a more traditional context switch where you swap the stacks beforehand.

As Kerry pointed out, the PIT has 4 channels, each with its own interrupt vector and so if you run multiple PITS in parallel you can then allow a second one to interrupt a first one's interrupt context by controlling the interrupt priorities of each channel.

The question is whether this is a good base for a scheduler or not?

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark & Kerry – Definitely this behavior is not so friendly to be used for preemptive based schedulers which use single interrupt. I have used similar feature successfully on power-pc cores.

But thanks for all your guidance and support on this topic. I will try to figure out a way to handle overrun.

Regards,

Kishore

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kishore Bolisetti,

What do you mean? Do you still want to use another PIT channel timer interrupt?

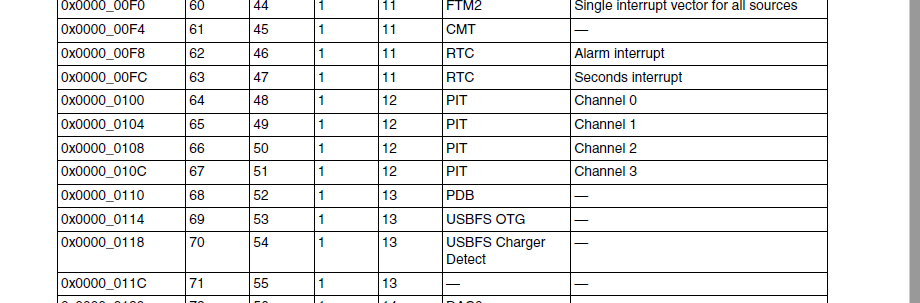

From the K65 interrupt vector assignments table, you can know that different PIT channel have different vector

So, you can use other PIT channel interrupt.

But the same interrupt when happens, and didn't exit the ongoing interrupt handler, it can't generate another same interrupt.

So, I think you can try another channel PIT interrupt.

Wish it helps you!

If you still have question about it, please kindly let me know.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------