- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- KV4x : CADC Triggering with External GPIO Input

KV4x : CADC Triggering with External GPIO Input

KV4x : CADC Triggering with External GPIO Input

Hi ,

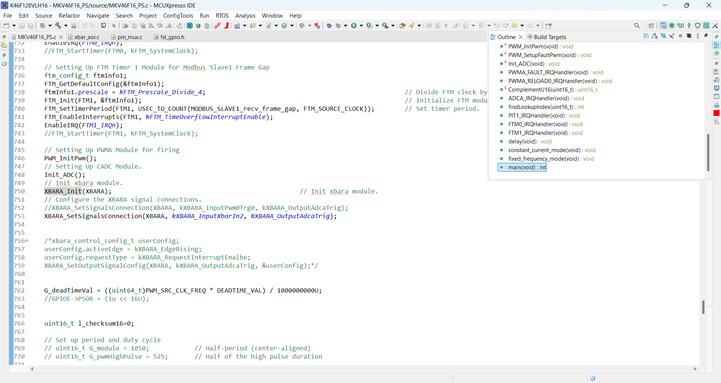

i want to bind CADC Trigger with rising edge of external input using X-bara Module.

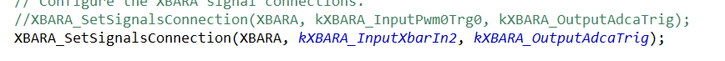

i have bind xbarIN2 with ADC trigger....

to give input trigger on XBARIN2 pin i m generating PWM pulse and connect that pin with external jumper to XBARIN2 ..

so when PWM goes high it trigger ADC and when ADC reading are ready in ADC IRQ i m toggling one GPIO to measure time...and it almost shows 900 ns...

why its taking this much time...

earlier i tested ADC triggering with PWM (commented line)

it has given around 400 ns time to get the result in ADC IRQ..

why its taking some extra time in case of GPIO...and also there is no setting of rising edge...so is it getting triggered on level change..??

Hi,

If you use PWM signal to trigger ADC via crossbar, the delay you measured via GPIO toggling in ADC ISR is about 400nS. If you use XBARIN2 pin to trigger ADC which is connected to the same PWM signal, the delay is about 900nS.

I suppose that the the XBARIN2 pin is connected a SCHMITT TRIGGERS, which can guarantee that the ADC triggering signal is a digital signal. The SCHMITT TRIGGERS leads to the delay.

Hope it can help you

BR

XiangJun Rong

I want to bind the Cyclic-ADC with an external input (GPIO). The ADC should be triggered on the rising edge of the external input signal.

Expectation:

The total time duration from the rising edge of the external input to the ADC interrupt (ADC IRQ) should be approximately 400 ns.

Issue:

In my case, this duration is around 900 ns. To verify this, I have used an oscilloscope:

- Yellow: Represents the external input signal.

- Green: Represents a pulse (GPIO toggle) that I generate in the ADC IRQ after receiving the ADC result.

Based on this observation, I suspect that the Cyclic-ADC is not being triggered correctly on the rising edge of the external input.

Could you please help me verify if the Cyclic-ADC is configured correctly for triggering on the rising edge? Are there any additional steps or settings required to achieve the expected 400 ns duration?

Hi,

I do not see the I/O cell structure for KV4x, this is the normal I/O cell structure for KE1x, I suppose that the I/O cell for KV4x has the similar structure.

There is a Schmitt-Trigger module in the input path which I marked as red circle, which can guarantee that the output of Schmitt-Trigger module is a digital signal to protect the digital input circuit. The Schmitt-Trigger module can lead to large delay.

If you use PWM trigger via cross-bar, it does not pass the I/O cell, so it does not have the delay.

Hope it can help you

BR

XiangJun Rong

Thank you for the clarification regarding the Schmitt-Trigger delay in the KV4x I/O cell structure. I have a few additional questions:

Are there any recommended practices or alternate configurations to reduce the Schmitt-Trigger delay while still using an external input GPIO as the ADC trigger?

Are there other trigger sources or alternate methods in the KV4x family that can achieve ADC triggering from an external GPIO without incurring significant delays?

If the delay cannot be eliminated or minimized effectively, could you recommend a different NXP microcontroller family that allows ADC triggering from an external GPIO with either no delay or minimal latency (e.g., within 400 ns)? I am open to switching to a controller that better suits this requirement."

Hi,

As far as I know that each I/O cell for every MCU has the Schmitt-Trigger circuit to protect the I/O cell.

BR

XiangJun Rong