- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KEA128 WDOG

KEA128 WDOG

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am trying to Configure the WDOG for KEA128 TRK-KEA Board but it is not working. Here is my configuration code for WDOG (10msec Reset time)

System clock is 20Mhz

| WDOG_CNT = 0x20C5; | // write the 1st unlock word | ||

| WDOG_CNT = 0x28D9; | // write the 2nd unlock word |

__asm("nop");

__asm("nop");

| WDOG_TOVAL = 10; |

| WDOG_CS2 | = 0x01; | // 1Khz Clock | ||

| WDOG_CS1 | = 0x80; | // enable WDT |

in Debugging i can't see any changes in WDT_CNT register :smileysad:

the controller is never resetting.

Thanks in advance

MFG

Robin

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

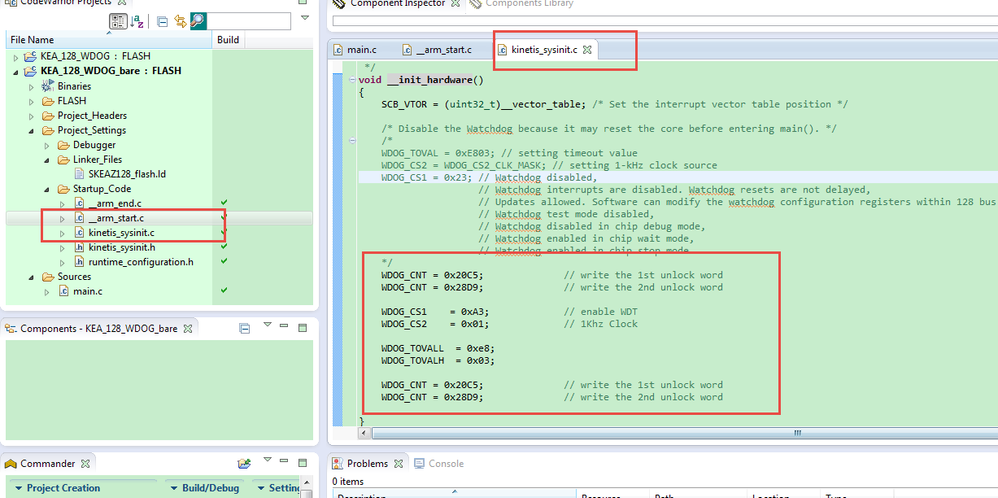

Hi Robin S,

Did you create the CW barebone project?

If yes, did you modifiy the _arm_start.c file?

Because in the __init_hardware() function, it disable the Watchdog, and register WDOG_CS1[EN] is the write-once bit after reset.

You can add your SWD configuration code in the __init_hardware() function, then your watchdog will works ok, I already test it.

__init_hardware() is in file kinetis_sysinit.c.

Attached project is my barebone WDOG project, just for your reference.

Wish it helps you!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using KEA128 . I need to disable wdog before going to sleepmode. please help me

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Not knowing the details of the implementation in the KEA128, but:

Disabling the watchdog would defeat the sense of a watchdog: if you could disable it after it has been enabled, that would be pretty bad. See http://www.ganssle.com/watchdogs.htm

If you go into sleep mode, the hardware will care about it and will suspend it for that time, so you don't need to disable it.

I hope this helps,

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin S,

From the datasheet:

"

By default, the watchdog is not functional in Debug mode, Wait mode, or Stop mode.

Setting WDOG_CS1[DBG], WDOG_CS1[WAIT] or WDOG_CS1[STOP] can activate

the watchdog in Debug, Wait or Stop modes.

"

So, if you want to monitor the watchdog in debug mode, you should enable WDOG_CS1[DBG] bit, then try agian.

Wish it helps you!

If you still have question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingjing,

I set WDOG_CS1(DBG) register bit in debugging mode but it doesn't change the end result.please refer the above post.

Thanks and Kind Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

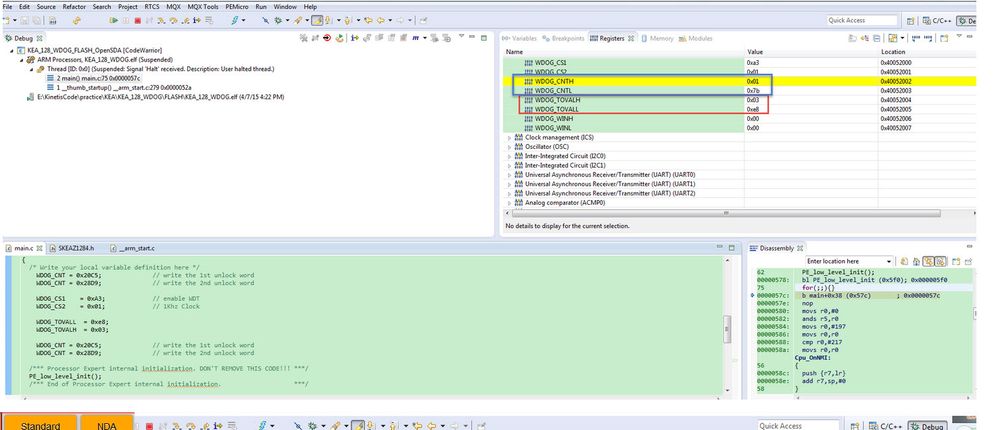

Hi Robin S,

I create a project, it can see the WDOG_CNT increasing.

The time out value is 1S, use 1KHZ internal low-power oscillator as the watchdog clock.

The test project is in the attachment, just for your reference.

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingjing,

May be you created this in processor expert that's why it's working , Here is my code , please can you Debugg it and see r u getting the same result and please don't configure it for it's default value.

Output is on PTC0 and PTC1

int main(void)

{

asm("CPSID i"); // Disable Interrupt

ICS_C1|=ICS_C1_IRCLKEN_MASK; /* Enable the internal reference clock*/

ICS_C3= 0x90; /* Reference clock frequency = 39.0625 KHz*/

while(!(ICS_S & ICS_S_LOCK_MASK)); /* Wait for PLL lock, now running at 40 MHz (1024 * 39.0625Khz) */

ICS_C2|=ICS_C2_BDIV(1) ; /*BDIV=2, Bus clock = 20 MHz*/

ICS_S |= ICS_S_LOCK_MASK ; /* Clear Loss of lock sticky bit */

WDOG_CNT = 0x20C5; // write the 1st unlock word

WDOG_CNT = 0x28D9; // write the 2nd unlock word

WDOG_TOVALL = 10; // 10 x (1 / 1000) = 10 msec but cause of tolerance it's 16msec (Appx. +25 /-35 %)

WDOG_TOVALH = 0; // Always Write the Value for Cortex Controller in LOW & HIGH Byte

WDOG_CS2 = 0x01; // Select clock 1Khz ;

WDOG_CS1 = 0x80; // Enable WDT : Feed the Dog : Activate the Dog

GPIOA_PDDR = 0xF0000;

GPIOA_PDOR = 0x00000;

//Before Configuring PTA0 and PTB3 as Input , must clear them as per Datasheet Table 33-21

GPIOA_PIDR &= ~1 ; // PORT INPUT DATA REGISTER: configure PORTA0 pin as GPIO input, must clear PIDR bit

GPIOA_PIDR &= ~2048 ; // PORT INPUT DATA REGISTER: configure PORTB3 pin as GPIO input, must clear PIDR bit

//Configure PTA0 and PTB3 as Input

GPIOA_PDDR |= 0 << 0 ; // PORT DATA DIRECTION REGISTER: direction is INPUT , PORTA0

GPIOA_PDDR |= 0 << 11; // PORT DATA DIRECTION REGISTER: direction is Input , PORTB3

GPIOA_PDOR = 0x30000;

for(;;){}

}

Thanks & MFG,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin S,

Did you create the CW barebone project?

If yes, did you modifiy the _arm_start.c file?

Because in the __init_hardware() function, it disable the Watchdog, and register WDOG_CS1[EN] is the write-once bit after reset.

You can add your SWD configuration code in the __init_hardware() function, then your watchdog will works ok, I already test it.

__init_hardware() is in file kinetis_sysinit.c.

Attached project is my barebone WDOG project, just for your reference.

Wish it helps you!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingjing,

Thank you very much and Thank you Mark Butcher,

Yes i am creating bareborad project.

The code is working fine as you mentioned in your reply, it was Start up code file Configuration problem.one more thing i would like to ask you , in your kinetis_sysinit.c file you have unlock the WDOG at the start and at the end inside __init_hardware() function, why do we need to unlock it two times(specially at the end of the function)?

one more question I am using in my project the following Modules:

FTM,

internal oscillator and

GPIO'S ,

do i need to do any kind of modification in my Start up configuration file?

Thanks and Kind Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin S,

About the unlock twice, please refer to our reference manual, this actually one sequence :

Write to the WDOG_CNTH:L registers of 0xC520 followed by 0xD928 within 16 bus clocks start the unlock sequence.

Just the reference manual definition.

About other module, you don't need to do modification in your start up code.

Wish it helps you!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingjing,

I think u understand me wrong,I am not talking about the first and second unlock sequence but unlocking the WDOG at the start and end of void __init_hardware() function.as we can see in the following code we are unlocking WDOG first , doing configuration as per our Requirement and at the end again we are unlocking it.my question is why we are unlocking it again at the end?

| WDOG_CNT = 0x20C5; | |

| WDOG_CNT = 0x28D9; |

| WDOG_CS2 = 0x01; | |

| WDOG_CS1 = 0xA3; |

| WDOG_TOVALL = 0xE8; | |

| WDOG_TOVALH = 0x03; |

| WDOG_CNT = 0x20C5; | |

| WDOG_CNT = 0x28D9; |

Thanks and Kind Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin S,

Both unlock sequence is just reset the watchdog counter to 0x0000, I just want the counter reset to 0, and count again.

The first one is to reset the counter, then it won't reach the timeout counter immediately, because if reach the timeout counter, the cpu will reset, maybe the time isn't longer enough for the WDOG configuration.

The second one is my usage, I just want the counter run from 0 after my new WDOG configuration.

Of course, you can have your own usage.

Wish it helps you!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingjing,

Thanks , now i got it.

MFG,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin

When debugging, the watchdog counter may not be counting - let it runs for a short time and then pause to check the new count value rather than just single-stepping.

For 10ms period you need

WDOG_TOVAL = (10 << 8);

or

WDOG_TOVALL = 10;

Your present setting is for 2.56s timeout.

Regards

Mark

Kinetis: µTasker Kinetis support

KE: µTasker FRDM-KE02Z support / µTasker FRDM-KE02Z40M support / µTasker FRDM-KE06Z support

For the complete "out-of-the-box" Kinetis experience and faster time to market

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mark,

I have one question , you mentioned in your previous comment that WDOG Reset timing is 2.56 sec, As per my Calculation if the clock is 1Khz and i am not using Prescaler than it should be 1 X 10 (WDOG_TOVAL) / 1Khz= 10 msec. or am i doing some mistake in setting WDOG control registers?

Should i have to define WDOG_TOVALL= 10 and WDOG_TOVALH=0; is that mandatory, if i am defining WDOG_TOVAL=10 , Doesn't it write automatically in lower byte of WDOG_TOVAL register?.

I think this is what i forget in my case

16.3.2.1 Reconfiguring the Watchdog

In some cases (such as when supporting a bootloader function), users may want to reconfigure or disable the watchdog without forcing a reset first. By setting CS1[UPDATE] to a 1 on the initial configuration of the watchdog after a reset, users can reconfigure the watchdog at any time by executing an unlock sequence. (Conversely, if CS1[UPDATE] remains 0, the only way to reconfigure the watchdog is by initiating a reset.) The unlock sequence is similar to the refresh sequence but uses different values.

MFG,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin

The watchdog registers are big-endian and the ARM core is little endian so you need to either write as bytes to the low and high registers or else convert the endianness when writing half-words - see Peripheral usage endianness observation

The example in the user manuals is incorrect so ignore it as reference to writing the timeout value (it was probably copied from an earlier manual for a processor with big-endian core and not modified to be accurate).

That is wy you see

WDOG_TOVAL = BIG_SHORT_WORD(2000); // 2000ms

in the examples that I posted since this automatically ensures that it matches.

Regards

Mark

Kinetis: µTasker Kinetis support

KE: µTasker FRDM-KE02Z support / µTasker FRDM-KE02Z40M support / µTasker FRDM-KE06Z support

For the complete "out-of-the-box" Kinetis experience and faster time to market

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mark,

Thanks for your unconditional support on every topic.

As you mentioned in your comment in debugging mode i have to wait for sometime and then pause the code to see the changes in WDOG counter i did but their is not any changes in WDOG counter , it always remains at 0x00(Both higher n lower bytes).

is that mandatory to define WDOG_TOVALL or TOVALH , can't it automatically take the value in Lower eight bit if the value is define in decimal,because before this i was using 8 bit controller S9S08RN8 n for that it has worked, I also tried as you mentioned by writing Higher and lower byte of WDOG_TOVAL register but it doesn't work.One thing i would like to add here , in Debug mode i have seen that it configured the WDOG_TOVAL register correctly.(WDOG_TOVAL=10)

As jingjing mentioned in his comment that for debugging i need to activate debug mode in WDOG control register i also did that but it doesn't work.

I also tried with System clock Frequency at 20Mhz by changing the WDOG clock but i didn't get any changes.WDOG is never resetting the controller.

One strange thing which i noticed is that when i am Flashing the controller, in my console window i can see that the code is Flashed Successfully and it's also showing me the WDDOG configuration Register values which are Default values like

WDOG_CS1=0X23;

WDOG_CS2=0X03;

WDOG_CNTH=0x00;

WDOG_CNTL=0x00;

WDOG_TOVALH=0x0e;

WDOG_TOVLL=0xe8;

but in Debugging mode it is showing me the correct configuration of all WDOG Registers.I Read in someone's post it has something to do with NMI (Non-Maskable Interrupt) pin but not able to understand whats exactly it does.

Note : I am not using any interrupt so at the start of code i disabled all the interrupts

Here some related post to WDOG configuration problem , may be helpful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin

I don't see what is happening on your board or whether the debugger is influencing the behavior negatively or not.

The only thing that I can do is show you the WDOG code for the KE devices used in the uTasker project which operates as expected (2s timeout, clocked from LPO)

UNLOCK_WDOG();

WDOG_CS2 = (WDOG_CS2_CLK_1kHz | WDOG_CS2_FLG);

WDOG_TOVAL = BIG_SHORT_WORD(2000); // 2000ms

WDOG_WIN = 0;

WDOG_CS1 = (WDOG_CS1_EN); // enable watchdog with 2s timeout

where:

#define UNLOCK_WDOG() WDOG_UNLOCK = WDOG_UNLOCK_SEQUENCE_1; \

WDOG_UNLOCK = WDOG_UNLOCK_SEQUENCE_2

// this sequence must be performed within 20 bus cycles and the writes are possible for the WCT period (16 bus clocks for KE)

Warning: Do not try to step the unlock and configuration code because the debugger will cause it fail since it will be much to slow - alway set a breakpoint "after" the complete operation!

and

| #define BIG_SHORT_WORD(x) | (unsigned short)((x << 8) | (x >> 8)) |

Regards

Mark

Kinetis: µTasker Kinetis support

KE: µTasker FRDM-KE02Z support / µTasker FRDM-KE02Z40M support / µTasker FRDM-KE06Z support

For the complete "out-of-the-box" Kinetis experience and faster time to market

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Mark,

I will try it on Tuesday on my TRK KEA 128 board and will let you know.

MFG

Robin