- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: K82 SDK example for TRNG

K82 SDK example for TRNG

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K82 SDK example for TRNG

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello !

I have K82 BusClock 48 Mhz and with this clock I try to use TRNG in way like in SDK example.

Initialization is OK but GetRandomData is always return error.

TRNG_GetDefaultConfig(&trngConfig);

/* Set sample mode of the TRNG ring oscillator to Von Neumann, for better random data.

* It is optional.*/

trngConfig.sampleMode = kTRNG_SampleModeVonNeumann;

/* Initialize TRNG */

status = TRNG_Init(TRNG0, &trngConfig);

I have reduced clock divider from default to 2,4,or kTRNG_RingOscDiv8

trngConfig.ringOscDiv = TRNG_USER_CONFIG_DEFAULT_OSC_DIV; // 0 -> 2,4,8

and GetRandomData start to return OK status and some random data.

I have taken data by 4 byte chunks and always last 3 bytes are equal,

like 0x68 0x35 0x35 0x35

So I think I need better configuration for TRNG block.

Could you suggest configuration values what make TRNG faster and more random ?

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

When I recover from LLS3 mode :

/* Wait for PLL lock. MCG in PEE mode in RUN. */

while (!(kMCG_Pll0LockFlag & CLOCK_GetStatusFlags()))

{

}

CLOCK_SetPeeMode();

/* Power mode change. */

SMC_SetPowerModeRun(SMC); // No need ?

while (kSMC_PowerStateRun != SMC_GetPowerModeState(SMC))

{

}

/* Show/check current power mode. DEBUG. */

...SMC_GetPowerModeState(SMC));

I think Wait PLL lock is mandatory operation, but setting to RUN mode is not.

It returns to RUN mode automatically. And I think TRNG can be used immideatelly after PLL is locked.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

When exit LLS3 low power mode, MCG mode will be same with when LLS was entered.

The exception to this if LLS is entered when in PEE mode, in this case the MCG will be in PBE mode when LLS is exited.

You can check the PLL lock status before call CLOCK_SetPeeMode() function.

If you enter into LLS3 from VLPR mode, when exit LLS3 low power mode, it will enter to VLPR mode, not Run mode.

If you enter into LLS3 low power mode from RUN mode, it will exit to RUN mode.

We had tested that TRNG can work in VLPR (system clock = bus clock = 4MHz) with TRNG OSC_DIV value to 0x3 (divide by 8).

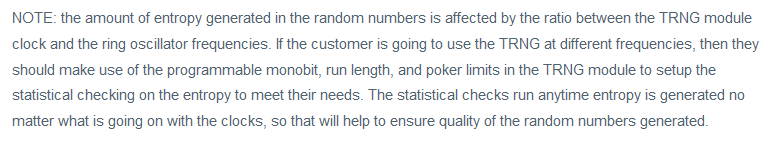

Our Kinetis product team provide below note for your reference:

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

So you recommend do not use System/Bus clock less than 60Mhz.

And we can assume if TRNG give good result at normal condition, it will not fail later on with other temperature and transistition to/from low power mode ? I mean RUN to VLLS3/LLS3 and back.

Is this so ?

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

There with quite few info about TRNG run at low power mode(VLPR).

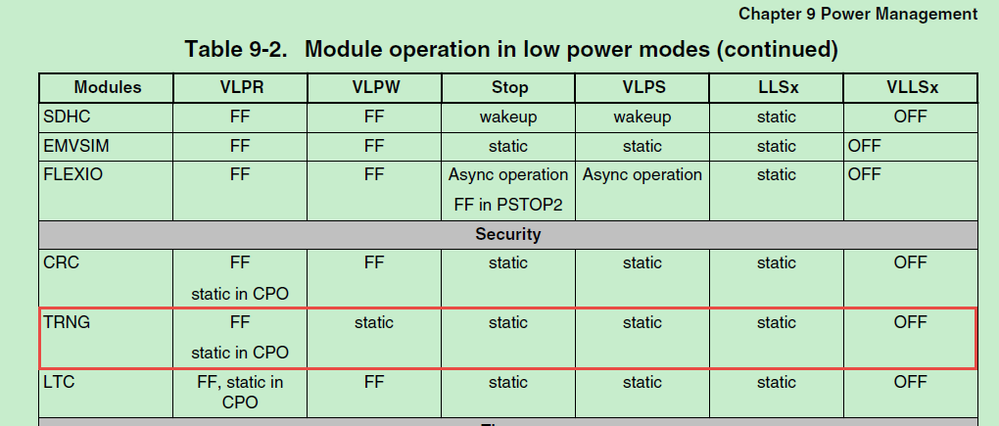

From below module operation in low power modes shows TRNG only works in VLPR mode.

I still need to check with product team about how to config TRNG working in VLPR mode.

About you mentioned RUN to VLLS3/LLS3 and back, there with issue at TRNG.

I would suggest to check the MCG working status before and after exit VLLS3/LLS3 low power mode.

Thank you for the attention.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

But what it means for our case ? If we select right divider and TRNG work in normal condition,

can we be sure if power mode transpositions, temperature and etc. will not have any effect for entropy of TRNG ?

Please, give advice.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

Please check Kinetis product team below feedback:

The problem is that as you slow down the peripheral clock for the TRNG module, the TRNG oscillator is running too fast to clock the downstream logic. Changing the OSC_DIV setting allows for slowing down the TRNG oscillator. In general the design team recommends using OSC_DIV=01 and SAMP_MODE=01 on K81.

On a properly working TRNG, setting SAMP_MODE=00 does not improve the results, and make the TRNG take 4x as long to generate entropy (of no better quality).

I'm not sure how you got some of the lower frequency tests to work. It might be that with some configurations there was some aliasing taking place that allowed the test to pass. Even with the max frequency using OSC_DIV=01 is recommended, and with that setting you should be able to cover reasonable RUN frequencies.

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

There with less info at reference manual about TRNG working conditions (bus clock frequency and TRNG clock frequency).

I need to check with Kinetis product team about it.

I will let you know when there with any feedback.

Thank you for the patience.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

But you execute test at original system clock 120 Mhz ?

For have shared example, I have taken mbedtls_selftest and drop system/bus clock to 40 Mhz by using embedded ConfigTools. And result is fully reproducable, if divisor 0 it returns 1 and ENTROPY test is not pass.

So it some how depends from value of clocks and I haven't modify clock tree.

I have attached modified example from SDK.

In my code I have the next clocks :

kCLOCK_CoreSysClk - 48000000 Hz

kCLOCK_BusClk - 48000000 Hz

kCLOCK_FlexBusClk - 6000000 Hz

kCLOCK_FlashClk - 24000000 Hz

kCLOCK_PllFllSelClk - 12000000 Hz

and at list divider 2 is need.

It would be nice to know from what clocks have so nice dependence.

It help to rearrange clock/tree for avoid this nonstability of TRNG.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

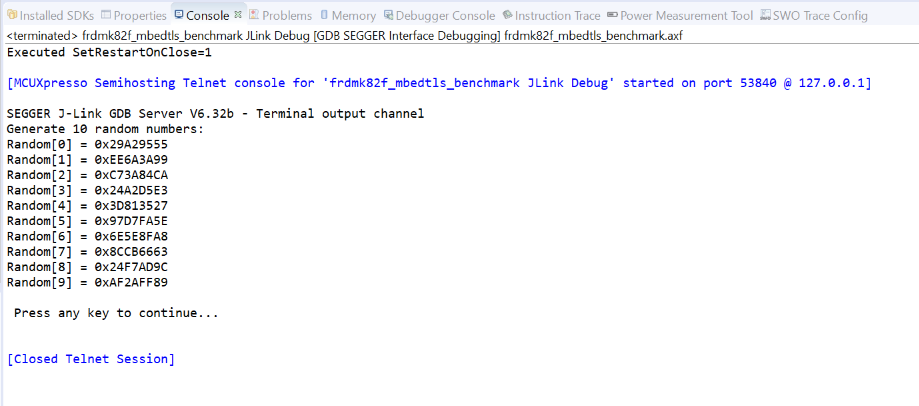

I use your attached code and could generate your mentioned issue.

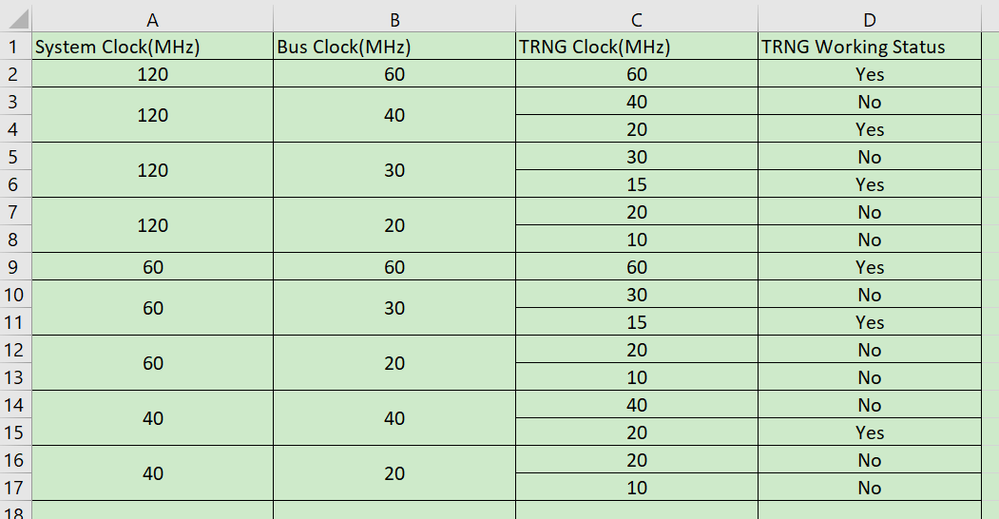

Then, I do a test with different clock frequency and check TRNG working status.

Please check below test result:

There with below description about TRNG working scheme:

TRNG is based on collecting bits from a random noise source. This random noise source is a ring oscillator that is sensitive to random noise (temperature variations, voltage variations, cross-talk and other random noise) within the device in which the TRNG is used.

The ring oscillator clock frequency doesn't mentioned in reference manual.

From the test, the TRNG working status quite related with bus clock and itself clock frequency.

Thank you for the attention.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

I'm using all latest versions.

- MCUXpresso IDE v10.2.1 [Build 795] [2018-07-25]

- MCUXpresso SDK v2.4.1 [2018-06-18]

and TRNG is initialized by using mbedTLS library call CRYPTO_InitHardware();

divider value 2 and up and everything is work.

May be I should return to some examples from SDK. I also use direct JTAG flashing and J19 connector in use.

All other components work fine. This is only one line what is problem.

I have started to divide clock becouse find some mentioned about it in nxp community blogs but I can't find link any more.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

I did a test with MCUXpresso SDK provided <frdmk82f_mbedtls_benchmark> project and didn't find your mentioned issue.

My hardware test environment is below:

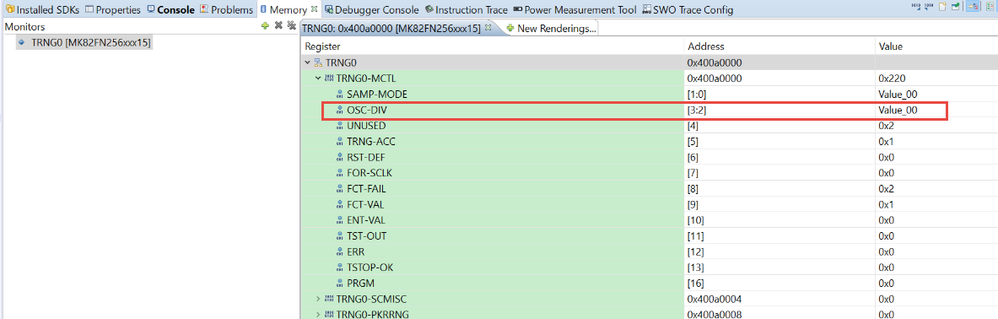

I checked the TRNG0_MCTL register value, the [OSC_DIV] value is 0x0.

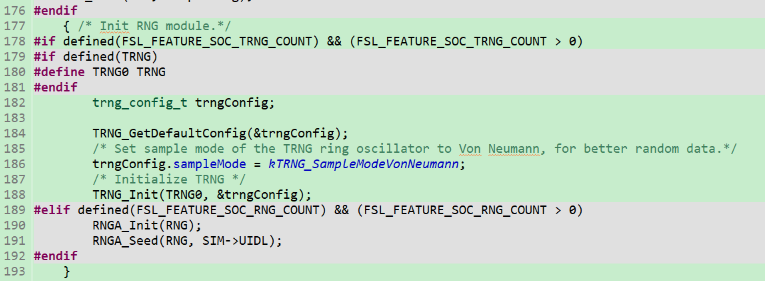

I didn't modify the [ksdk_mbedtls.c] file, which with below code to initialize TRNG module:

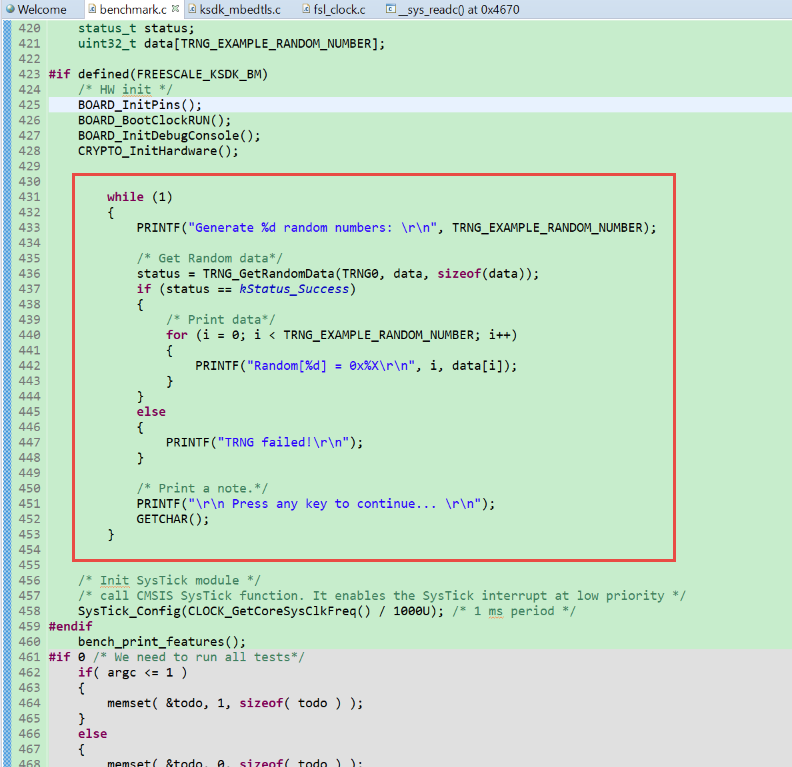

I copy <trng_random> project code to [benchmark.c] file to generate random numbers:

I also attached my modified [benchmark.c] file for your reference.

I didn't meet any issue with above code.

Thank you for the attention.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi !

I have got second board and result is the same.

With default configuration , TRNG is not able to generate random data.

Bus clock is 48 Mhz.

TRNG_GetDefaultConfig(&trngConfig);

/* Set sample mode of the TRNG ring oscillator to Von Neumann, for better random data.*/

trngConfig.sampleMode = kTRNG_SampleModeVonNeumann;

//trngConfig.ringOscDiv = kTRNG_RingOscDiv0; // Default, error

trngConfig.ringOscDiv = kTRNG_RingOscDiv2; // OK

...

So if oscillator clock is not divided, GetRandomData() always return error 1.

Could you suggest exact check list for all other dependencies what might have effect for TRNG functionality ?

Current issue is reproducible on 2 boards and it is start to be interesting what can be problem.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

Thank you for the info.

Could you please provide your used MCUXpresso SDK software package info and IDE software & version info?

I think there should not with hardware issue, for you are using the same FRDM-K82F board.

I would check if there with software issue. Thanks.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike !

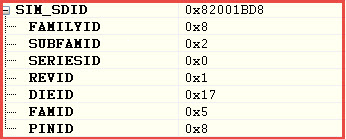

I have the same value in SIM-SDIO register.

I will try more boards. But on current one it is clear reproducible.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

Please let us know the result. Thank you.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi !

I have exactly the same lchip info on MCU.

Also I have read DIE_ID and REV_ID by using (SIM_SDID_DIEID(SIM->SDID)), (SIM_SDID_REVID(SIM->SDID))

- MCU DIE_ID 0xC00, REV_ID 0x8000

Issue is reproducible very well. Can it depends from someting else ?

I have only one board, but if you think this is board specific, I will try to find other one.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eugene,

Please check my FRDM-K82F board SIM-SDIO register info:

I tried two FRDM-K82F board with same results (could not regenerate your mentioned issue).

Thank you for the attention.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi !

I have tried multiple times :

1. If TRNG init done like this, GetRandomData() is always failed:

TRNG_GetDefaultConfig(&trngConfig);

/* Set sample mode of the TRNG ring oscillator to Von Neumann, for better random data.*/

trngConfig.sampleMode = kTRNG_SampleModeVonNeumann;

TRNG_Init(TRNG0, &trngConfig);

2. If Like this , always OK :

TRNG_GetDefaultConfig(&trngConfig);

/* Set sample mode of the TRNG ring oscillator to Von Neumann, for better random data.*/

trngConfig.sampleMode = kTRNG_SampleModeVonNeumann;

trngConfig.ringOscDiv = kTRNG_RingOscDiv2; // +++

TRNG_Init(TRNG0, &trngConfig);

Reason is unknown for me.

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Sorry for the delay reply.

I use the similar init code (1) and couldn't generate your mentioned issue with FRDM-K82F board.

Chip info:

MK82FN256VLL15

mask set: 1N03P

QAC1531C

What's your chip info?

How many chips on your site with this behavior?

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi !

Example is the same as in previous version of SDK.

Divider is set to 0 and TRNG dosn't work even BusClock = 48Mhz.

trngConfig.ringOscDiv = TRNG_USER_CONFIG_DEFAULT_OSC_DIV;

divider is need to be set.

Regards,

Eugene