- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K66F + 16-bit SDRAM

K66F + 16-bit SDRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am going to use MT48LC4M16A2 for 16-bit SDRAM mode with F66F MCU.

1. Could you tell what the address line connection between MCU and SDRAM?

2. Should I use DQM0, DQM1 to access it? Or I need to use DQM2 and DQM3?

3. Can I use 2 16-bit SDRAM to form one 32-bit by using DQM0~~3? Or I can only use 2 16-bit SDRAM by using SDRAM_CS0 and SDRAM_CS1? If so, any 128Mbit SDRAM to recommend?

Thanks,

Christie

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

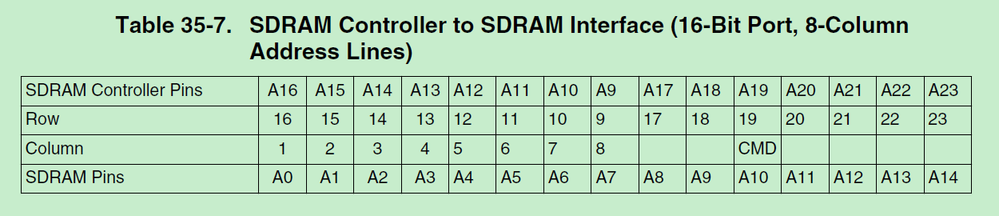

1) Based on the SDRAM table, MT48LC4M16A2 only has A0~~A11, BA0:BA1, so I can't connect the required pin(A0~~A14) in table. Is it right?

TS: The reference manual mentioned: Most SDRAMs likely have fewer address lines than are shown in the tables, so follow only the connections shown until all SDRAM address lines are connected.

Customer can refer table 35-7, the MT48LC4M16A2's BA0 connects with K66 SDRAM controller's A21, MT48LC4M16A2's BA1 connects with K66 SDRAM controller's A22.

2) If I want to use MT48LC8M16A2P(128MB, 9 column), table 35-8 is right?

TS: Yes, that's right.

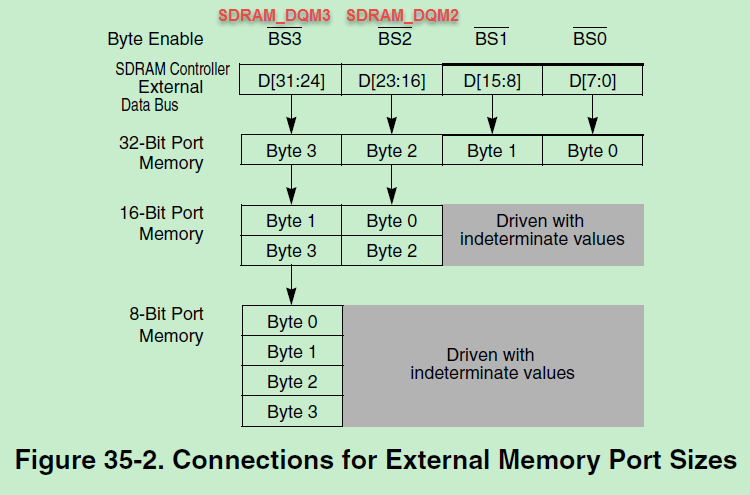

3) Looks like that I can't form 32-bit by using 2 16-bit SDRAM because there is only SDRAM Data 16~~31, right?

TS: For K66 SDRAM controller doesn't provide SDRAM_D[15:0] pins, please check my updated comments below.

Customer need to use two SDRAM_CS[0:1] connect with two 16-bit SDRAM chip.

You could use MT48LC8M16A2P(128Mb) as a replacement.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1. Could you tell what the address line connection between MCU and SDRAM?

TS: Please refer K66 reference manual Table 35-7. SDRAM Controller to SDRAM Interface (16-Bit Port, 8-Column Address Lines) about K66 SDRAM Controller to SDRAM memory address line connection.

The SDRAM controller data line using below connection (K66 SDRAM controller doesn't provide SDRAM_D[15:0] pins):

SDRAM controller to SDRAM

SDRAM_D16 -------------- DQ0

... ...

SDRAM_D31 -------------- DQ15

SDRAM Control line connection:

SDRAM controller to SDRAM

SDRAM_WE -------------- /WE

SDRAM_CAS -------------- /CAS

SDRAM_RAS -------------- /RAS

SDRAM_CS0 -------------- /CS

SDRAM_DQM2 -------------- DQML

SDRAM_DQM3 -------------- DQMH

CLKOUT(PTA6) ------------- CLK

SDRAM_CKE -------------- CKE

2. Should I use DQM0, DQM1 to access it? Or I need to use DQM2 and DQM3?

TS: Please use DQM2 and DQM3

3. Can I use 2 16-bit SDRAM to form one 32-bit by using DQM0~~3? Or I can only use 2 16-bit SDRAM by using SDRAM_CS0 and SDRAM_CS1? If so, any 128Mbit SDRAM to recommend?

TS: K66 SDRAM controller doesn't provide SDRAM_D[15:0] pins.

Customer need to use two SDRAM_CS[0:1] connect with two 16-bit SDRAM chips.

You could use MT48LC8M16A2P(128Mb) as a replacement.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ma Hui,

For the answer to the 3rd question, I disagree with you. There is only 16bit data bus on K66 for its 144pin package. 32bit data bus is only possible with K65.

Also you cannot use DQM0 and DQM1 when data bus available is SDRAM_D31-SDRAM_D16. DQM1 and DQM0 correspond to BS1 and BS0 in Table 35-2 in K66 RM.

Hao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Cutworth,

Thank you for the reminder.

The K66 without SDRAM_D[15:0] pins.

I will update the answer to customer.

best regards,

Ma Hui

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Finally, I got the customized board on my hand. When I am testing SDRAM, I can't see any data read from SDRAM.

So, there are something wrong there.

1) MCU: MK66FN2M0VLQ18

2) SDRAM:MT48LC8M16A2(2 chips). See attached.

3) Here is pin_mux:

void BOARD_InitPins(void)

{

CLOCK_EnableClock(kCLOCK_PortA); /* Port A Clock Gate Control: Clock enabled */

CLOCK_EnableClock(kCLOCK_PortB); /* Port B Clock Gate Control: Clock enabled */

CLOCK_EnableClock(kCLOCK_PortC); /* Port C Clock Gate Control: Clock enabled */

CLOCK_EnableClock(kCLOCK_PortD); /* Port D Clock Gate Control: Clock enabled */

CLOCK_EnableClock(kCLOCK_PortE); /* Port E Clock Gate Control: Clock enabled */

//-----*****Just doing re-arrangement from pin_mux.c that is generated by pin tool*****-----

//-----*****UART0 used as DEBUG interface on Demo Board*****-----

// PORT_SetPinMux(PORTB, PIN16_IDX, kPORT_MuxAlt3); /* PORTB16 (pin E10) is configured as UART0_RX(Demo Board) */

// PORT_SetPinMux(PORTB, PIN17_IDX, kPORT_MuxAlt3); /* PORTB17 (pin E9) is configured as UART0_TX(Demo Board) */

//----Configured on iNetVu 7710 Version 5.0

//-----*****UART1 used as DEBUG interface*****-----

PORT_SetPinMux(PORTE, PIN0_IDX, kPORT_MuxAlt3); /* PORTE0 (pin 1) is configured as UART1_TX */

PORT_SetPinMux(PORTE, PIN1_IDX, kPORT_MuxAlt3); /* PORTE1 (pin 2) is configured as UART1_RX */

//-----*****Configure UART3*****-----

PORT_SetPinMux(PORTE, PIN4_IDX, kPORT_MuxAlt3); /* PORTE4 (pin 7) is configured as UART3_TX */

PORT_SetPinMux(PORTE, PIN5_IDX, kPORT_MuxAlt3); /* PORTE5 (pin 8) is configured as UART3_RX */

//-----*****Configure LPUART0*****-----

PORT_SetPinMux(PORTE, PIN8_IDX, kPORT_MuxAlt5); /* PORTE8 (pin 11) is configured as LPUART0_TX */

PORT_SetPinMux(PORTE, PIN9_IDX, kPORT_MuxAlt5); /* PORTE9 (pin 12) is configured as LPUART0_RX */

//-----*****ENET Configuration*****-----

PORT_SetPinMux(PORTA, PIN12_IDX, kPORT_MuxAlt4); /* PORTA12 (pin 64) is configured as RMII0_RXD1 */

PORT_SetPinMux(PORTA, PIN13_IDX, kPORT_MuxAlt4); /* PORTA13 (pin 65) is configured as RMII0_RXD0 */

PORT_SetPinMux(PORTA, PIN14_IDX, kPORT_MuxAlt4); /* PORTA14 (pin 66) is configured as RMII0_CRS_DV */

PORT_SetPinMux(PORTA, PIN15_IDX, kPORT_MuxAlt4); /* PORTA15 (pin 67) is configured as RMII0_TXEN */

PORT_SetPinMux(PORTA, PIN16_IDX, kPORT_MuxAlt4); /* PORTA16 (pin 68) is configured as RMII0_TXD0 */

PORT_SetPinMux(PORTA, PIN17_IDX, kPORT_MuxAlt4); /* PORTA17 (pin 69) is configured as RMII0_TXD1 */

PORT_SetPinMux(PORTA, PIN5_IDX, kPORT_MuxAlt4); /* PORTA5 (pin 55) is configured as RMII0_RXER */

// On Demo Board

// PORT_SetPinMux(PORTB, PIN0_IDX, kPORT_MuxAlt4); /* PORTB0 (pin H10) is configured as RMII0_MDIO */

// PORTB->PCR[0] = ((PORTB->PCR[0] &

// (~(PORT_PCR_ODE_MASK | PORT_PCR_ISF_MASK))) /* Mask bits to zero which are setting */

// | PORT_PCR_ODE(PCR_ODE_ENABLED) /* Open Drain Enable: Open drain output is enabled on the corresponding pin, if the pin is configured as a digital output. */

// );

// PORT_SetPinMux(PORTB, PIN1_IDX, kPORT_MuxAlt4); /* PORTB1 (pin H9) is configured as RMII0_MDC */

//----Configured on iNetVu 7710 Version 5.0

PORT_SetPinMux(PORTA, PIN7_IDX, kPORT_MuxAlt5); /* PORTA7 (pin 59) is configured as RMII0_MDIO */

PORTA->PCR[7] = ((PORTB->PCR[7] &

(~(PORT_PCR_ODE_MASK | PORT_PCR_ISF_MASK))) /* Mask bits to zero which are setting */

| PORT_PCR_ODE(PCR_ODE_ENABLED) /* Open Drain Enable: Open drain output is enabled on the corresponding pin, if the pin is configured as a digital output. */

);

PORT_SetPinMux(PORTA, PIN8_IDX, kPORT_MuxAlt5); /* PORTA8 (pin 60) is configured as RMII0_MDC */

PORT_SetPinMux(PORTE, PIN26_IDX, kPORT_MuxAlt2); /* PORTE26 (pin 47) is configured as ENET_1588_CLKIN */

//-----*****Initialize the SDRAMC pins*****-----

PORT_SetPinMux(PORTA, PIN6_IDX, kPORT_MuxAlt5); /* PORTA6 (pin 58) is configured as CLKOUT */

// Configured for RMII Network on Demo Board

PORT_SetPinMux(PORTB, PIN0_IDX, kPORT_MuxAlt5); /* PORTB0 (pin 81) is configured as SDRAM_CAS_b---Configured for RMII Network on Demo Board */

PORT_SetPinMux(PORTB, PIN1_IDX, kPORT_MuxAlt5); /* PORTB1 (pin 82) is configured as SDRAM_RAS_b---Configured for RMII Network on Demo Board */

PORT_SetPinMux(PORTB, PIN2_IDX, kPORT_MuxAlt5); /* PORTB2 (pin 83) is configured as SDRAM_WE */

PORT_SetPinMux(PORTB, PIN3_IDX, kPORT_MuxAlt5); /* PORTB3 (pin 84) is configured as SDRAM_CS0_b */

PORT_SetPinMux(PORTB, PIN4_IDX, kPORT_MuxAlt5); /* PORTB4 (pin 85) is configured as SDRAM_CS1_b */

// Configure SDRAM Data Pins

PORT_SetPinMux(PORTB, PIN20_IDX, kPORT_MuxAlt5); /* PORTB20 (pin 99) is configured as SDRAM_D31, FB_AD31 */

PORT_SetPinMux(PORTB, PIN21_IDX, kPORT_MuxAlt5); /* PORTB21 (pin 100) is configured as FB_AD30, SDRAM_D30 */

PORT_SetPinMux(PORTB, PIN22_IDX, kPORT_MuxAlt5); /* PORTB22 (pin 101) is configured as FB_AD29, SDRAM_D29 */

PORT_SetPinMux(PORTB, PIN23_IDX, kPORT_MuxAlt5); /* PORTB23 (pin 102) is configured as SDRAM_D28, FB_AD28 */

PORT_SetPinMux(PORTC, PIN12_IDX, kPORT_MuxAlt5); /* PORTC12 (pin 117) is configured as FB_AD27, SDRAM_D27 */

PORT_SetPinMux(PORTC, PIN13_IDX, kPORT_MuxAlt5); /* PORTC13 (pin 118) is configured as SDRAM_D26, FB_AD26 */

PORT_SetPinMux(PORTC, PIN14_IDX, kPORT_MuxAlt5); /* PORTC14 (pin 119) is configured as SDRAM_D25, FB_AD25 */

PORT_SetPinMux(PORTC, PIN15_IDX, kPORT_MuxAlt5); /* PORTC15 (pin 120) is configured as FB_AD24, SDRAM_D24 */

PORT_SetPinMux(PORTB, PIN5_IDX, kPORT_MuxAsGpio); /* PORTB5 (pin 86) is configured as PTB5 */

PORT_SetPinMux(PORTB, PIN6_IDX, kPORT_MuxAlt5); /* PORTB6 (pin 87) is configured as FB_AD23, SDRAM_D23 */

PORT_SetPinMux(PORTB, PIN7_IDX, kPORT_MuxAlt5); /* PORTB7 (pin 88) is configured as SDRAM_D22, FB_AD22 */

PORT_SetPinMux(PORTB, PIN8_IDX, kPORT_MuxAlt5); /* PORTB8 (pin 89) is configured as FB_AD21, SDRAM_D21 */

PORT_SetPinMux(PORTB, PIN9_IDX, kPORT_MuxAlt5); /* PORTB9 (pin 90) is configured as FB_AD20, SDRAM_D20 */

PORT_SetPinMux(PORTB, PIN10_IDX, kPORT_MuxAlt5); /* PORTB10 (pin 91) is configured as FB_AD19, SDRAM_D19 */

PORT_SetPinMux(PORTB, PIN11_IDX, kPORT_MuxAlt5); /* PORTB11 (pin 92) is configured as SDRAM_D18, FB_AD18 */

//-----*****UART0 used as DEBUG interface on Demo Board*****-----

PORT_SetPinMux(PORTB, PIN16_IDX, kPORT_MuxAlt5); /* PORTB16 (pin 95) is configured as FB_AD17, SDRAM_D17---Used as DEBUG interface on Demo Board */

PORT_SetPinMux(PORTB, PIN17_IDX, kPORT_MuxAlt5); /* PORTB17 (pin 96) is configured as FB_AD16, SDRAM_D16---Used as DEBUG interface on Demo Board */

// Configure SDRAM Address

PORT_SetPinMux(PORTB, PIN18_IDX, kPORT_MuxAlt5); /* PORTB18 (pin 97) is configured as SDRAM_A23, FB_AD15 */

PORT_SetPinMux(PORTC, PIN0_IDX, kPORT_MuxAlt5); /* PORTC0 (pin 103) is configured as FB_AD14, SDRAM_A22 */

PORT_SetPinMux(PORTC, PIN1_IDX, kPORT_MuxAlt5); /* PORTC1 (pin 104) is configured as SDRAM_A21, FB_AD13 */

PORT_SetPinMux(PORTC, PIN2_IDX, kPORT_MuxAlt5); /* PORTC2 (pin 105) is configured as SDRAM_A20, FB_AD12 */

PORT_SetPinMux(PORTC, PIN4_IDX, kPORT_MuxAlt5); /* PORTC4 (pin 109) is configured as FB_AD11, SDRAM_A19 */

PORT_SetPinMux(PORTC, PIN5_IDX, kPORT_MuxAlt5); /* PORTC5 (pin 110) is configured as FB_AD10, SDRAM_A18 */

PORT_SetPinMux(PORTC, PIN6_IDX, kPORT_MuxAlt5); /* PORTC6 (pin 111) is configured as SDRAM_A17, FB_AD9 */

PORT_SetPinMux(PORTC, PIN7_IDX, kPORT_MuxAlt5); /* PORTC7 (pin 112) is configured as SDRAM_A16, FB_AD8 */

PORT_SetPinMux(PORTC, PIN8_IDX, kPORT_MuxAlt5); /* PORTC8 (pin 113) is configured as SDRAM_A15, FB_AD7 */

PORT_SetPinMux(PORTC, PIN9_IDX, kPORT_MuxAlt5); /* PORTC9 (pin 114) is configured as SDRAM_A14, FB_AD6 */

PORT_SetPinMux(PORTC, PIN10_IDX, kPORT_MuxAlt5); /* PORTC10 (pin 115) is configured as SDRAM_A13, FB_AD5 */

PORT_SetPinMux(PORTD, PIN2_IDX, kPORT_MuxAlt5); /* PORTD2 (pin 129) is configured as SDRAM_A12, FB_AD4 */

PORT_SetPinMux(PORTD, PIN3_IDX, kPORT_MuxAlt5); /* PORTD3 (pin 130) is configured as SDRAM_A11, FB_AD3 */

PORT_SetPinMux(PORTD, PIN4_IDX, kPORT_MuxAlt5); /* PORTD4 (pin 131) is configured as SDRAM_A10, FB_AD2 */

PORT_SetPinMux(PORTD, PIN5_IDX, kPORT_MuxAlt5); /* PORTD5 (pin 132) is configured as FB_AD1, SDRAM_A9 */

// Configure SDRAM Control signal

PORT_SetPinMux(PORTD, PIN7_IDX, kPORT_MuxAlt5); /* PORTD7 (pin 136) is configured as SDRAM_CKE */

PORT_SetPinMux(PORTC, PIN17_IDX, kPORT_MuxAlt5); /* PORTC17 (pin 124) is configured as SDRAM_DQM3 */

PORT_SetPinMux(PORTC, PIN16_IDX, kPORT_MuxAlt5); /* PORTC16 (pin 123) is configured as SDRAM_DQM2 */

PORT_SetPinMux(PORTC, PIN18_IDX, kPORT_MuxAlt5); /* PORTC18 (pin 125) is configured as SDRAM_DQM1 */

PORT_SetPinMux(PORTC, PIN19_IDX, kPORT_MuxAlt5); /* PORTC19 (pin 126) is configured as SDRAM_DQM0 */

//-----*****Configure Flexbus high address*****-----

PORT_SetPinMux(PORTA, PIN28_IDX, kPORT_MuxAlt6); /* PORTA28 (pin 79) is configured as FB_A25 */

PORT_SetPinMux(PORTA, PIN29_IDX, kPORT_MuxAlt6); /* PORTA29 (pin 80) is configured as FB_A24 */

PORT_SetPinMux(PORTD, PIN15_IDX, kPORT_MuxAlt6); /* PORTD15 (pin 144) is configured as FB_A23 */

PORT_SetPinMux(PORTD, PIN14_IDX, kPORT_MuxAlt6); /* PORTD14 (pin 143) is configured as FB_A22 */

PORT_SetPinMux(PORTD, PIN13_IDX, kPORT_MuxAlt6); /* PORTD13 (pin 142) is configured as FB_A21 */

PORT_SetPinMux(PORTD, PIN12_IDX, kPORT_MuxAlt6); /* PORTD12 (pin 141) is configured as FB_A20 */

PORT_SetPinMux(PORTD, PIN11_IDX, kPORT_MuxAlt6); /* PORTD11 (pin 140) is configured as FB_A19 */

PORT_SetPinMux(PORTD, PIN10_IDX, kPORT_MuxAlt6); /* PORTD10 (pin 139) is configured as FB_A18 */

PORT_SetPinMux(PORTD, PIN9_IDX, kPORT_MuxAlt6); /* PORTD9 (pin 138) is configured as FB_A17 */

PORT_SetPinMux(PORTD, PIN8_IDX, kPORT_MuxAlt6); /* PORTD8 (pin 137) is configured as FB_A16 */

// Configure Flexbus RW, OE, chip select and etc Control signal

PORT_SetPinMux(PORTB, PIN19_IDX, kPORT_MuxAlt5); /* PORTB19 (pin 98) is configured as FB_OE_b */

PORT_SetPinMux(PORTC, PIN11_IDX, kPORT_MuxAlt5); /* PORTC11 (pin 116) is configured as FB_RW_b */

PORT_SetPinMux(PORTD, PIN0_IDX, kPORT_MuxAlt5); /* PORTD0 (pin 127) is configured as FB_CS1_b */

PORT_SetPinMux(PORTD, PIN1_IDX, kPORT_MuxAlt5); /* PORTD1 (pin 128) is configured as FB_CS0_b */

//----*****Configure I2C0*****-----

PORT_SetPinMux(PORTE, PIN10_IDX, kPORT_MuxAlt2); /* PORTE10 (pin 13) is configured as I2C3_SDA */

PORT_SetPinMux(PORTE, PIN11_IDX, kPORT_MuxAlt2); /* PORTE11 (pin 14) is configured as I2C3_SCL */

//----*****Configure CANBUS*****-----

PORT_SetPinMux(PORTE, PIN24_IDX, kPORT_MuxAlt2); /* PORTE24 (pin 45) is configured as CAN1_TX */

PORT_SetPinMux(PORTE, PIN25_IDX, kPORT_MuxAlt2); /* PORTE25 (pin 46) is configured as CAN1_RX */

//----*****Configure as GPIO*****-----

// Configured on Demo Board

PORT_SetPinMux(PORTA, PIN10_IDX, kPORT_MuxAsGpio); /* PORTA10 (pin M9) is configured as PTA10 */

PORTA->PCR[10] = ((PORTA->PCR[10] &

(~(PORT_PCR_PS_MASK | PORT_PCR_PE_MASK | PORT_PCR_ISF_MASK))) /* Mask bits to zero which are setting */

| PORT_PCR_PS(PCR_PS_UP) /* Pull Select: Internal pullup resistor is enabled on the corresponding pin, if the corresponding PE field is set. */

| PORT_PCR_PE(PCR_PE_ENABLED) /* Pull Enable: Internal pullup or pulldown resistor is enabled on the corresponding pin, if the pin is configured as a digital input. */

);

// PORT_SetPinMux(PORTA, PIN10_IDX, kPORT_MuxAsGpio); /* PORTA10 (pin 62) is configured as PTA10 */

PORT_SetPinMux(PORTA, PIN11_IDX, kPORT_MuxAsGpio); /* PORTA11 (pin 63) is configured as PTA11 */

PORT_SetPinMux(PORTC, PIN3_IDX, kPORT_MuxAsGpio); /* PORTC3 (pin 106) is configured as PTC3 */

PORT_SetPinMux(PORTC, PIN9_IDX, kPORT_MuxAsGpio); /* PORTC9 (pin D7) is configured as PTC9 */

PORT_SetPinMux(PORTD, PIN6_IDX, kPORT_MuxAsGpio); /* PORTD6 (pin 133) is configured as PTD6 */

PORT_SetPinMux(PORTE, PIN2_IDX, kPORT_MuxAsGpio); /* PORTE2 (pin 3) is configured as PTE2 */

PORT_SetPinMux(PORTE, PIN3_IDX, kPORT_MuxAsGpio); /* PORTE3 (pin 4) is configured as PTE3 */

PORT_SetPinMux(PORTE, PIN6_IDX, kPORT_MuxAsGpio); /* PORTE6 (pin 9) is configured as PTE6 */

PORT_SetPinMux(PORTE, PIN7_IDX, kPORT_MuxAsGpio); /* PORTE7 (pin 10) is configured as PTE7 */

PORT_SetPinMux(PORTE, PIN12_IDX, kPORT_MuxAsGpio); /* PORTE12 (pin 15) is configured as PTE12 */

PORT_SetPinMux(PORTE, PIN27_IDX, kPORT_MuxAsGpio); /* PORTE27 (pin 48) is configured as PTE27 */

PORT_SetPinMux(PORTE, PIN28_IDX, kPORT_MuxAsGpio); /* PORTE28 (pin 49) is configured as PTE28 */

//----*****Configure JTAG*****-----

PORT_SetPinMux(PORTA, PIN0_IDX, kPORT_MuxAlt7); /* PORTA0 (pin 50) is configured as JTAG_TCLK */

PORT_SetPinMux(PORTA, PIN1_IDX, kPORT_MuxAlt7); /* PORTA1 (pin 51) is configured as JTAG_TDI */

PORT_SetPinMux(PORTA, PIN2_IDX, kPORT_MuxAlt7); /* PORTA2 (pin 52) is configured as JTAG_TDO */

PORT_SetPinMux(PORTA, PIN3_IDX, kPORT_MuxAlt7); /* PORTA3 (pin 53) is configured as JTAG_TMS */

PORT_SetPinMux(PORTA, PIN4_IDX, kPORT_MuxAlt7); /* PORTA4 (pin 54) is configured as NMI_b */

//-----The initialization done by tool generation

// Select RMII clock src.

SIM->SOPT2 = ((SIM->SOPT2 & (~(SIM_SOPT2_RMIISRC_MASK))) | SIM_SOPT2_RMIISRC(SOPT2_RMIISRC_ENET)); // Bit19==1---RMII clock source select: External bypass clock (ENET_1588_CLKIN).

SIM->SOPT5 = ((SIM->SOPT5 &

(~(SIM_SOPT5_UART1TXSRC_MASK | SIM_SOPT5_LPUART0TXSRC_MASK))) /* Mask bits to zero which are setting */

| SIM_SOPT5_UART1TXSRC(SOPT5_UART1TXSRC_UART_TX) /* UART 1 transmit data source select: UART1_TX pin */

| SIM_SOPT5_LPUART0TXSRC(SOPT5_LPUART0TXSRC_LPUART_TX) /* LPUART0 transmit data source select: LPUART0_TX pin */

);

SIM->USBPHYCTL = ((SIM->USBPHYCTL &

(~(SIM_USBPHYCTL_USBVREGSEL_MASK))) /* Mask bits to zero which are setting */

| SIM_USBPHYCTL_USBVREGSEL(USBPHYCTL_USBVREGSEL_VREG_IN0) /* Selects the default input voltage source to the USB Regulator in case both VREG_IN0 and VREG_IN1 are powered. If only one of the regulator inputs is powered, it will automatically be selected by the regulator's power mux circuitry.: VREG_IN0 will be selected if both regulator inputs are powered */

);

}

4) Here is initialization and write, read that I copied from TWR-K65F demo.

status_t SDRAM_Init(SDRAM_Type *base, uint32_t busClock_Hz)

{

sdramc_config_t config;

sdramc_refresh_config_t refConfig;

sdramc_blockctl_config_t ctlConfig;

/* SDRAM refresh timing configuration. */

refConfig.refreshTime = kSDRAMC_RefreshThreeClocks;

/* Refresh time 4096 rows/ 64ms. */

refConfig.sdramRefreshRow = 15625;

refConfig.busClock_Hz = busClock_Hz;

/* SDRAM controller configuration. */

// /*SDRAM Port size: 32 bit, command bit 20. */

// ctlConfig.portSize = kSDRAMC_PortSize32Bit;

/*SDRAM Port size: 16 bit, command bit 20.---Modified by SU */

ctlConfig.portSize = kSDRAMC_PortSize16Bit;

ctlConfig.location = kSDRAMC_Commandbit20;

ctlConfig.block = kSDRAMC_Block0;

/* SDRAM with trcd-15ns(min), trp-15ns(min), tras-37ns (min). */

ctlConfig.latency = kSDRAMC_LatencyOne;

ctlConfig.address = SDRAM_START_ADDRESS;

ctlConfig.addressMask = 0x7c0000;

config.refreshConfig = &refConfig;

config.blockConfig = &ctlConfig;

config.numBlockConfig = 1;

/* Initializes the SDRAM controller. */

SDRAMC_Init(base, &config);

/* The external SDRAM initialization sequence. */

return SDRAM_InitSequence(base, kSDRAMC_Block0, kSDRAM_MrsBurstLenOne, kSDRAM_MrsSequential, kSDRAM_MrsLatencyTwo,

kSDRAM_MrsStandOperation, kSDRAM_MrsWriteBurst);

}

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD_InitDebugConsole();

// BOARD_InitPins();

// BOARD_BootClockRUN();

// BOARD_InitDebugConsole();

//-----*****Copied from Httpsrv demo*****-----

// Disable MPU.

base->CESR &= ~MPU_CESR_VLD_MASK;

// // Set RMII clock src.

// SIM->SOPT2 |= SIM_SOPT2_RMIISRC_MASK; // Done in BOARD_InitPins(void)

//-----Copied from Flexbus driver demo on TWR-K65F180M-----

/* Set clock out to flexbus CLKOUT. */

CLOCK_SetClkOutClock(0); // Select clock on CLKOUT pin(0---Flexbus CLOCK)

// //-----*****Set RMII clock src.*****----- //-----Copied from http server demo application-----

// // Select RMII clock source(Bit19==1---External bypass clock(ENET_1588_CLKIN), ==0---EXTAL clock)

// SIM->SOPT2 |= SIM_SOPT2_RMIISRC_MASK; // Done in BOARD_InitPins(void)-----

//-----*****Sets the Flexbus security level*****-----

soptReg = SIM->SOPT2 & ~SIM_SOPT2_FBSL_MASK;

SIM->SOPT2 = soptReg | SIM_SOPT2_FBSL(3); //Bit9:8==11---Off-chip instruction accesses and data accesses are allowed

/* Enable the FB_BE_xx_yy signal in Flexbus */

// SIM_base==0x4004_7000+0x1040==0x4004_8040(SIM_SCGC7, Bit0---Flexbus clock enable/disable)

// CLOCK_EnableClock(kCLOCK_Flexbus0); // Done in FLEXBUS_Init()--- kCLOCK_Flexbus0 == 0x1040_0000

// /* Set clock out to flexbus CLKOUT. */

// CLOCK_SetClkOutClock(0);

//

// /* Sets the Flexbus security level*/

// soptReg = SIM->SOPT2 & ~SIM_SOPT2_FBSL_MASK;

// SIM->SOPT2 = soptReg | SIM_SOPT2_FBSL(3);

//

// /* Enable the FB_BE_xx_yy signal in Flexbus */

CLOCK_EnableClock(kCLOCK_Flexbus0);

fbReg = FB->CSPMCR & ~FB_CSPMCR_GROUP2_MASK;

FB->CSPMCR = fbReg | FB_CSPMCR_GROUP2(2);

fbReg = FB->CSPMCR & ~FB_CSPMCR_GROUP3_MASK;

FB->CSPMCR = fbReg | FB_CSPMCR_GROUP3(2);

fbReg = FB->CSPMCR & ~FB_CSPMCR_GROUP4_MASK;

FB->CSPMCR = fbReg | FB_CSPMCR_GROUP4(2);

fbReg = FB->CSPMCR & ~FB_CSPMCR_GROUP5_MASK;

FB->CSPMCR = fbReg | FB_CSPMCR_GROUP5(2);

/* SDRAM initialize. */

clockSrc = CLOCK_GetFreq(kCLOCK_BusClk);

PRINTF("\r\n SDRAM Example Start!\r\n");

if (SDRAM_Init(EXAMPLE_SDRAMC, clockSrc) != kStatus_Success)

{

PRINTF("\r\n SDRAM Init Failed\r\n");

}

PRINTF("\r\n SDRAM Memory Write Start, Start Address 0x%x, Data Length %d !\r\n", sdram, datalen);

//-----*****Prepare data and write to SDRAM.*****-----

for (index = 0; index < datalen; index++)

{

sdram_writeBuffer[index] = index;

*(uint32_t *)(sdram + index) = sdram_writeBuffer[index];

}

PRINTF("\r\n SDRAM Write finished!\r\n");

PRINTF("\r\n SDRAM Read Start, Start Address 0x%x, Data Length %d !\r\n", sdram, datalen);

//-----*****Read data from the SDRAM.*****-----

for (index = 0; index < datalen; index++)

{

sdram_readBuffer[index] = *(uint32_t *)(sdram + index);

// sdram_readBuffer[index] >>= 16;

}

PRINTF("\r\n SDRAM Read finished!\r\n");

PRINTF("\r\n SDRAM Write Data and Read Data Compare Start!\r\n");

//-----*****Compare the two buffers.*****-----

while (datalen--)

{

if (sdram_writeBuffer[datalen] != sdram_readBuffer[datalen])

{

result = false;

PRINTF("\r\n SDRAM Write Data and Read Data Check Error=0x%x_0x%x_0x%x!\r\n", datalen, sdram_writeBuffer[datalen], sdram_readBuffer[datalen]);

// break;

}

else

{

if ((datalen % 1024) == 0)

{

PRINTF("\r\n SDRAM Write Data and Read Data_%d=%d_%d!\r\n", datalen, sdram_writeBuffer[datalen], sdram_readBuffer[datalen]);

}

PRINTF("\r\n SDRAM Write Data and Read Data Check_00=0x%x_0x%x_0x%x!\r\n", datalen, sdram_writeBuffer[datalen], sdram_readBuffer[datalen]);

}

}

if (result)

{

PRINTF("\r\n SDRAM Write Data and Read Data Succeed.\r\n");

}

else

{

PRINTF("\r\n SDRAM Write Data and Read Data Failed.\r\n");

}

PRINTF("\r\n SDRAM Example End.\r\n");

Could you tell me where the possible problems are? The SDRAM configuration is right?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I did more testing today and found the following:

1) When I change the latency to 0(1 before), I can write and read, but there is 20% error.

2) If I write 16 bit, I found the error only on lob byte. High byte always right.

There is eh same result on block0 and block1.

Is it possible to be related on SDRAM timing setting?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked SDRAM chip spec. and should set the latency to 3(3-3-3). I tried 3,2,1 and always read 0.

If I set to 0, it reads back the right data, but not reliable.

Can anyone help me to find out where the problem is and how to configure SDRAM timing?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is there anyone who can suggest to do any testing because I need to fix it and move forward?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ma Hui,

Thank you for your answers...

1) Based on the SDRAM table, MT48LC4M16A2 only has A0~~A11, BA0:BA1, so I can't connect the required pin(A0~~A14) in table. Is it right?

2) If I want to use MT48LC8M16A2P(128MB, 9 column), table 35-8 is right?

3) Looks like that I can't form 32-bit by using 2 16-bit SDRAM because there is only SDRAM Data 16~~31, right?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1) Based on the SDRAM table, MT48LC4M16A2 only has A0~~A11, BA0:BA1, so I can't connect the required pin(A0~~A14) in table. Is it right?

TS: The reference manual mentioned: Most SDRAMs likely have fewer address lines than are shown in the tables, so follow only the connections shown until all SDRAM address lines are connected.

Customer can refer table 35-7, the MT48LC4M16A2's BA0 connects with K66 SDRAM controller's A21, MT48LC4M16A2's BA1 connects with K66 SDRAM controller's A22.

2) If I want to use MT48LC8M16A2P(128MB, 9 column), table 35-8 is right?

TS: Yes, that's right.

3) Looks like that I can't form 32-bit by using 2 16-bit SDRAM because there is only SDRAM Data 16~~31, right?

TS: For K66 SDRAM controller doesn't provide SDRAM_D[15:0] pins, please check my updated comments below.

Customer need to use two SDRAM_CS[0:1] connect with two 16-bit SDRAM chip.

You could use MT48LC8M16A2P(128Mb) as a replacement.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------