- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K60 flexbus problems

K60 flexbus problems

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm trying to access a 16 bit fully multiplexed 64k CPLD which is hooked up to the external bus interface on chip select 0. I am using the TWR-K60F120M and MQX 4.1. The following code runs in a standard task.

#define A2D_CPLD_START_ADDRESS (*(volatile unsigned char*)(0xA0000000))

void flexbus_init(void) {

SIM_SCGC7 |= SIM_SCGC7_FLEXBUS_MASK; // Enable the clock to the FlexBus

SIM_CLKDIV1 |= SIM_CLKDIV1_OUTDIV3(0); // no divisor

// Set the GPIO ports clocks

SIM_SCGC5 = SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTD_MASK;

// 16 bit multiplexing - so set 16 bit address, latch, then those 16 bits become data lines

PORTB_PCR18 = PORT_PCR_MUX(5); // fb_ad[15]

PORTC_PCR0 = PORT_PCR_MUX(5); // fb_ad[14]

PORTC_PCR1 = PORT_PCR_MUX(5); // fb_ad[13]

PORTC_PCR2 = PORT_PCR_MUX(5); // fb_ad[12]

PORTC_PCR4 = PORT_PCR_MUX(5); // fb_ad[11]

PORTC_PCR5 = PORT_PCR_MUX(5); // fb_ad[10]

PORTC_PCR6 = PORT_PCR_MUX(5); // fb_ad[9]

PORTC_PCR7 = PORT_PCR_MUX(5); // fb_ad[8]

PORTC_PCR8 = PORT_PCR_MUX(5); // fb_ad[7]

PORTC_PCR9 = PORT_PCR_MUX(5); // fb_ad[6]

PORTC_PCR10 = PORT_PCR_MUX(5); // fb_ad[5]

PORTD_PCR2 = PORT_PCR_MUX(5); // fb_ad[4]

PORTD_PCR3 = PORT_PCR_MUX(5); // fb_ad[3]

PORTD_PCR4 = PORT_PCR_MUX(5); // fb_ad[2]

PORTD_PCR5 = PORT_PCR_MUX(5); // fb_ad[1]

PORTD_PCR6 = PORT_PCR_MUX(5); // fb_ad[0]

// Other lines - Output Enable, Read/Write, ChipSelect0, Address Latch Enable

PORTB_PCR19 = PORT_PCR_MUX(5); // fb_oe_b [nEBI_OE]

PORTC_PCR11 = PORT_PCR_MUX(5); // fb_rw_b [EBI_R/W]

PORTD_PCR1 = PORT_PCR_MUX(5); // fb_cs0_b [nEBI_CSO]

PORTD_PCR0 = PORT_PCR_MUX(5); // fb_ale [EBI_ALE/nEBI_CSI]

// Setup the chip select 1 control register (see K60P144M150SF3RM.pdf, section 33.3.3)

FB_CSCR0 = FB_CSCR_PS(0x2) // 16-bit port

//| FB_CSCR_BLS_MASK // data is right shifted, i.e. appears on bits 0-15

| FB_CSCR_EXTS_MASK

| FB_CSCR_AA_MASK // auto-acknowledge...

| FB_CSCR_WS(0x2) // ...after 2 wait states

| FB_CSCR_ASET(2) // assert chip select on 2nd clock edge after address

;

// Chip select mask register

FB_CSMR0 = FB_CSMR_BAM(0x0) //Set base address mask for 64K address space

| FB_CSMR_V_MASK

;

// Chip select address register

FB_CSAR0 = (unsigned int)&A2D_CPLD_START_ADDRESS; //Set Base address

}

void flexbus_read_card_info() {

volatile uint16_t raw_ID;

_dcache_disable(); // see https://community.freescale.com/thread/306380

raw_ID = (*(uint16_t*)(&A2D_CPLD_START_ADDRESS));

printf("Raw ID: %d\n", raw_ID);

}

The task runs flexbus_init, then flexbus_read_card_info. Whatever I do, raw_ID seems to come out as 40960, i.e. 0xa000. The value should actually be 0x81 (which is stored in the CPLD).

Can anyone help me understand why this might be?

I also noticed in the bsp_twrk60f120m code, in init_hw.c it calls a function _bsp_flexbus_mram_setup which also sets up chip select 0; I have tried commenting out this function call but it makes no difference.

Many thanks!

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We spent the whole day with the logic analyzer and figured out the problem. I'll put the solution here incase someone else has the same problem.

Firstly it was OK to connect addr[15:0] directly to FB_AD[15:0], because our 16-bit CPLD does not use word addressing.

The problem was that in the ChipSelect Multiplexing Control Register (FB_CSPMCR), the group1 multiplex control was set to 1 (FB_CS1) rather than 0 (FB_ALE). This occurs in the MQX init code - hw_init.c, _bsp_flexbus_setup(). Because of this, the address latch enable was not working at all.

Thanks anyway for your help, you pushed us in the right direction.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Andrew,

You are using Flexbus in multiplexed mode.

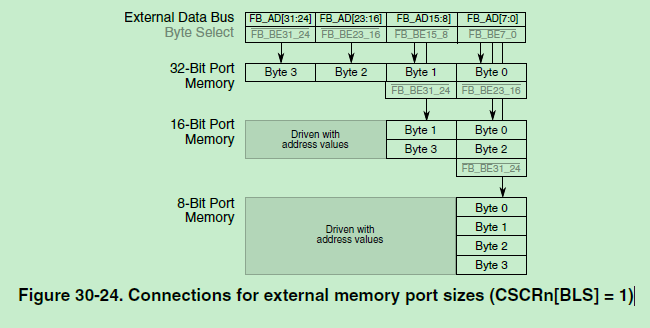

For the Flexbus 16bits data lines at FB_AD[15:0] pins, it need to set CSCRn[BLS] = 1, more detailed info, please check below picture:

And it need to check the hardware connection, for it using 16-bit data port, the CPLD address A0 pin should connect with Flexbus_AD[1] pin.

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thankyou very much for your quick reply. I forgot that I had commented out the BLS=1, thanks.

We currently have the CPLD Address[15:0] pins connected directly to AD[15:0] through an address latch. Looking in the reference manual K60P144M150SF3RM.pdf, section 33.4.1.2 says that the address and data lines should be connected from FB_AD0 upwards, however on the next paragraph it says that a 16 bit device connects to FB_AD[16:1]. Do you have any more information or an example schematic on why it starts from FB_AD1 and not FB_AD0? Should the FB_AD0 line be connected to anything?

Many thanks again

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We spent the whole day with the logic analyzer and figured out the problem. I'll put the solution here incase someone else has the same problem.

Firstly it was OK to connect addr[15:0] directly to FB_AD[15:0], because our 16-bit CPLD does not use word addressing.

The problem was that in the ChipSelect Multiplexing Control Register (FB_CSPMCR), the group1 multiplex control was set to 1 (FB_CS1) rather than 0 (FB_ALE). This occurs in the MQX init code - hw_init.c, _bsp_flexbus_setup(). Because of this, the address latch enable was not working at all.

Thanks anyway for your help, you pushed us in the right direction.