- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: K20 with external SRAM

K20 with external SRAM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

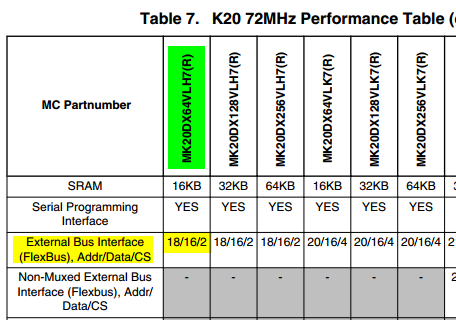

I am designing a new device, and plan to use the MK20DX64VLH7 Kinetis MUC. This system need 256kB external SRAM.

I have read the thread K20 external memory interface description wanted. But still not absolute sure. From the datasheet of the MK20DX64VLH7, there are FB_AD[17:0], FB_RW, FB_ALE/CS1/TS, FB_CS0#.

The SRAM Chip have A[17:0], D[15:0], WE#, OE#, CS1# and CS2.

Can i use that SRAM in multiplexed mode, by

latching the FB_AD[17:0] to SRAM_A[17:0],

FB_AD[15:0] to SRAM_D[15:0],

FB_RW to SRAM_WE#,

FB_ALE to the latched_FB_AD[17:0]

FB_CS0 to SRAM_CS0#?

Or do i any more glue logic? In the link above, the FB_AD[31:16] are used for data bus, but those pins are not available on the 64pin MK20DX64VLH7.

For this K20 device, the Fsys frequency is 36MHz. What could i expect as burst read/write rate? Considered the SRAM fast enough, are additional wait states required?

Any help or shared experiences with a multiplexed SRAM on the Kinetis would be helpful.

MS

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

According to K20 product brief (page 25):

http://www.freescale.com/files/32bit/doc/prod_brief/K20PB.pdf

You can refer to AN4393 "Using FlexBus Interface for Kinetis Microcontrollers" Applicaction Note

http://cache.freescale.com/files/microcontrollers/doc/app_note/AN4393.pdf

It looks that latching in multiplexed mode as you wrote can work.

Hope this helps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I am wondering the same thing.

The application note surely helps but does not show explicitly how to connect a 16bit(data bus) SRAM. I would REALLY appreciate to know exactly how to connect SRAM for maximum performance, preferably with a specific suggested SRAM device.

Thanks a ton!!

//bjoern

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Michael,

how is it going? Was it helpful?

We'd like to know! :smileywink:

Regards!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Monica,

thanks. First of all, i was impressed about the fast answer. And happy, that the answer was positive for my problem.

Actually, I have not implemented the details, so i dont know if the resulting hardware will work as expected. But i am positive for that.

best regards,

MS

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Excellent Michael, we'll be around! :smileywink:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

According to K20 product brief (page 25):

http://www.freescale.com/files/32bit/doc/prod_brief/K20PB.pdf

You can refer to AN4393 "Using FlexBus Interface for Kinetis Microcontrollers" Applicaction Note

http://cache.freescale.com/files/microcontrollers/doc/app_note/AN4393.pdf

It looks that latching in multiplexed mode as you wrote can work.

Hope this helps.