- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Input Reflected issues with the kw36

Input Reflected issues with the kw36

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Input Reflected issues with the kw36

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm using the kw36 build in CRC hardware feature and i'm having some problem with it.

I must use a predefined crc (Init / Poly / XorOut) to match the decoder we already got.

To match the decoder, I must enable the CRC_CFG->CRC_REF_IN register but I'm having an error every 2 frames (ish)

With a 16 bit CRC, it is always the first bit of the second byte whose at fault.

Example :

D3 91 D3 91 10 01 00 11 22 33 00 00 01 02 0B A4 00 00 05 7F C3 > My frame transmitted

D3 91 D3 91 -> Sync (4 Bytes)

10 -> Length (on 8 bits) = payload (14) + CRC (2)

01 00 11 22 33 00 00 01 02 0B A4 00 00 05 -> Payload

7F C3 -> CRC sent

Or the correct one is 7F 43

CRC configuration :

// Enable the CRC as it is disabled by default after reset

XCVR_MISC->CRCW_CFG |= XCVR_CTRL_CRCW_CFG_CRCW_EN(1);

GENFSK->CRC_CFG &= (uint32_t) ~(uint32_t) (GENFSK_CRC_CFG_CRC_SZ_MASK

| GENFSK_CRC_CFG_CRC_START_BYTE_MASK

| GENFSK_CRC_CFG_CRC_REF_IN_MASK

| GENFSK_CRC_CFG_CRC_REF_OUT_MASK

| GENFSK_CRC_CFG_CRC_BYTE_ORD_MASK);

GENFSK->CRC_CFG |= (uint32_t) (GENFSK_CRC_CFG_CRC_SZ(2) // CRC16

| GENFSK_CRC_CFG_CRC_START_BYTE(4) // Start after the sync

| GENFSK_CRC_CFG_CRC_REF_IN(1) // Input reflected

| GENFSK_CRC_CFG_CRC_REF_OUT(1) // Output reflected

| GENFSK_CRC_CFG_CRC_BYTE_ORD(0)); // LSB first

// Left align CRC seed and Poly.

GENFSK->CRC_INIT = 0x00001D0F<< (2 << 3);

GENFSK->CRC_POLY = 0x00001021 << (2 << 3);

GENFSK->CRC_XOR_OUT = 0x00000000 << (2 << 3);

GENFSK->XCVR_CFG &= ~GENFSK_XCVR_CFG_SW_CRC_EN_MASK;

CRC Value :

INIT = 0x1D0F<< (2 << 3);

POLY = 0x1021 << (2 << 3);

XOR_OUT = 0x0000 << (2 << 3);

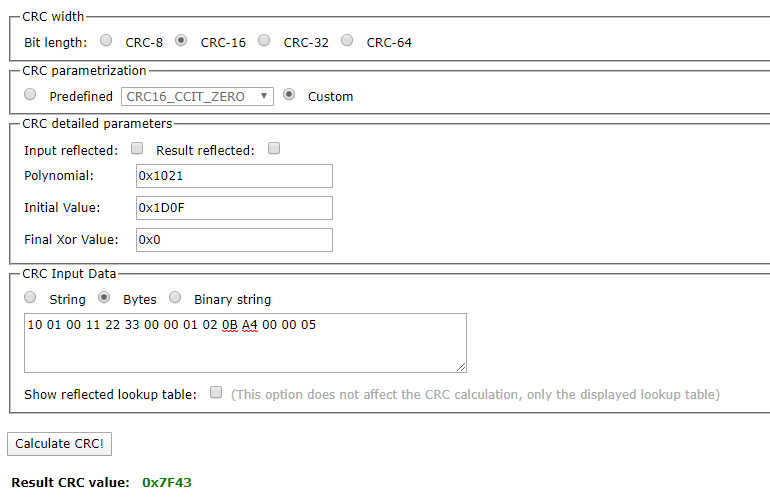

My online checker (the reference) : Sunshine's Homepage - Online CRC Calculator Javascript

Config :

If you have an idea of how to fix this, i will be grateful.

Regards,

Loïc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

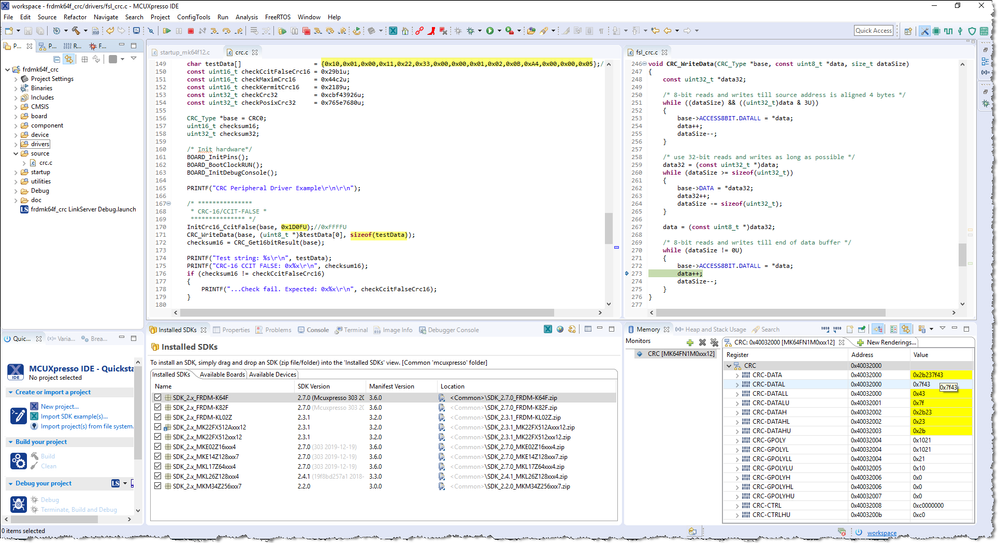

Please download the MCUXpresso SDK of KW36, then refer the CRC example.

You will get the 7F 43 after modify show below:

If you don't want to use APIs of MCUXpresso SDK, then you can configure CRC registers according to the image.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Robin,

Thanks for the reply,

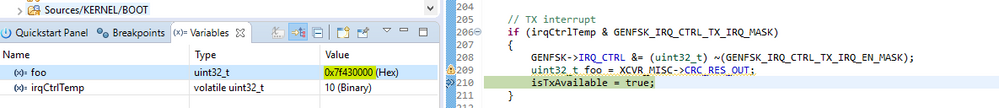

The thing is, when I check the calculated crc, it is the correct one (0x7F43) :

But the one sent is not (0x7FC3).

And I'm sure it comes from the "sender" and not my receiver because if I set the crc manually (crc software), i always get the correct one.

So I don't know how to explain that.

I would like to know, where the alteration happen.

Also, as I said, the problem dissapear if I disable the Ref input.

Regards,

Loïc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for my last reply! I didn't have KW36 on my hands. The CRC module seems different between K64 and KW36.

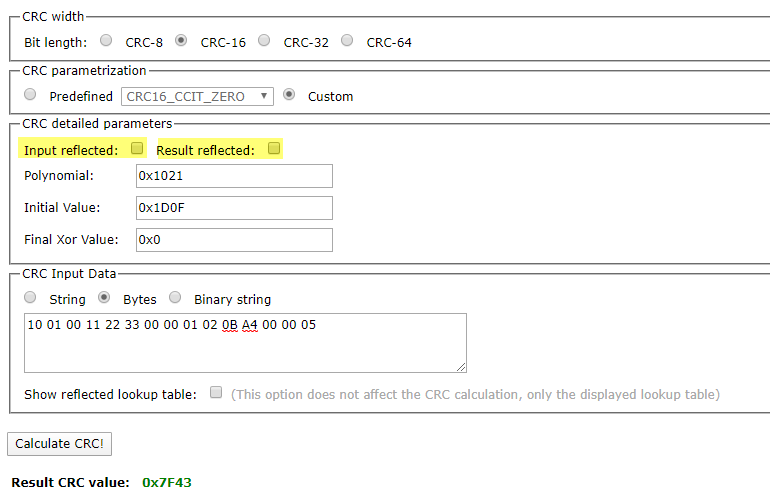

But I don't know why you configure Input reflected and Output reflected.

For your predefined crc (Init / Poly / XorOut) and online checker, it seems you don't need to reflect input and output.(I didn't reflect in my example too.)

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The thing is, to send 7F43 as the crc I need to reflect the input and the output on the sender side.

In my previous reply, both are enabled. If you don't, the Online Crc and the one sent is different.

Best Regards,

Loïc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I need to consult this with AE team and will update this thread as soon as I have their feedback.

Best Regards,

Robin