- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: How to order to NXP to check my MCU?

How to order to NXP to check my MCU?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We made customs board with K64 for our product.

At some boards, I couldn't connect to the MCU by the Multilink Universal. (some boards were OK)

I have asked this issue already, please see following post.

Finally, I replaced the MCU on my custom board to new one, then I could connect to the MCU.

I think I have to know why this issue happened.

So I would like NXP to check and verify my removed MCU.

MCU is broken or not,

MCU is in the specific mode,

etc...

How can I order this?

If someone has information, please let me know.

Regards,

Kiyoshi Matsuzaki

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kiyoshi Matsuzaki,

Thank you for your more details.

If you solder the chip on the board by your hand, and you didn't care about the solder temperature, I think your chip maybe damaged to a large degree.

A lot of people may damage the chip when they solder the chip and never care about the temperature.

When you solder the chip by hand, take care of 2 points:

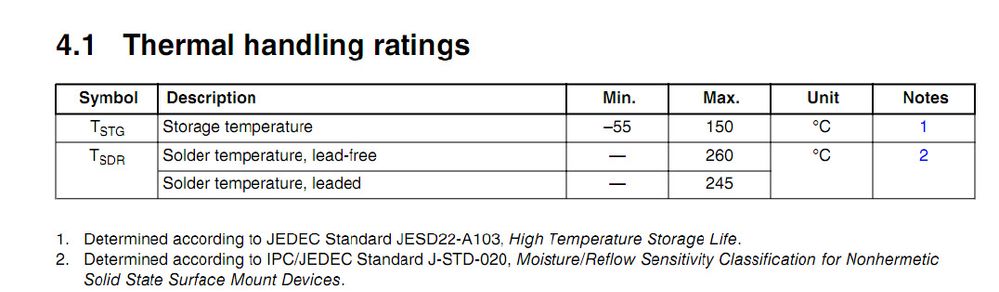

1. solder temperature below 260°C

2. solder time should as short as possible, long chip solder time may also damage the chip.

If you can't mass erase the chip and can't find the core, I suggest to solder an new chip and try again.

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kiyoshi Matsuzaki,

From your description, your chip may be locked or broken, there has a lot of factors may caused this phenomena.

1. solid problem

The solid temperature should not higher than 260°C, you can find this from the kinetis datasheet.

the solid time should as short as possible, both the higher temperature and the long solid time may damage the chip.

2. power on sequence

If you power on the reset pin before the VDD, this will cause the chip be locked. You should make sure the VDD is power on at first, then the reset pin can be power on again.

3. the debug interface wire is too long.

The debug wire between the board and the debugger should not longer than 15cm.

4, power and debug signal is not stable

Normally, if you find the chip can't be connect, please use the JLINK associate with the JLINK COMMANDER to unlock the chip at first, if the chip is locked, then it can be unlocked through the mass erase, but if the chip is damaged, it won't be connect with the debugger or programmer again.

Besides, we also recommend you add an 4.7K to 10K pullup resistor in the SWD_DIO and the NMI pin.

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jingjing

Thank you for your advice!

>1. solid problem

I use the board in my office. (Maybe 10°C-20°C)

>2. power on sequence

I've checked but it works right.

>3. the debug interface wire is too long.

I use the Multilink Universal with the proper cable.

>4, power and debug signal is not stable

I've checked by the oscilloscope. I think power and debug signal are good.

>please use the JLINK associate with the JLINK COMMANDER to unlock the chip at first, if the chip is locked, then it can be unlocked through the mass erase,

>but if the chip is damaged, it won't be connect with the debugger or programmer again.

I've tried this usng the Multilink Universal (I don't have the JLINK), but I couldn't connect to the MCU.

So I think this MCU is damaged.

>Besides, we also recommend you add an 4.7K to 10K pullup resistor in the SWD_DIO and the NMI pin.

Thank you, I'll try this.

I have a question.

I have the Multilink Universal only. I don't have the JLINK.

If the MCU was locked, can I unlock it using the Multilink Universal like JLINK?

Best regards,

Kiyoshi Matsuzaki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kiyoshi Matsuzaki,

>1. solider problem

I use the board in my office. (Maybe 10°C-20°C)

Take care, not the working temperature, it is the solider temperature, the chip solider to the board temperature!

A lot of people damaged the chip by the higher solider temperature.

What's your chip solider temperature?

>Multilink Universal mass erase

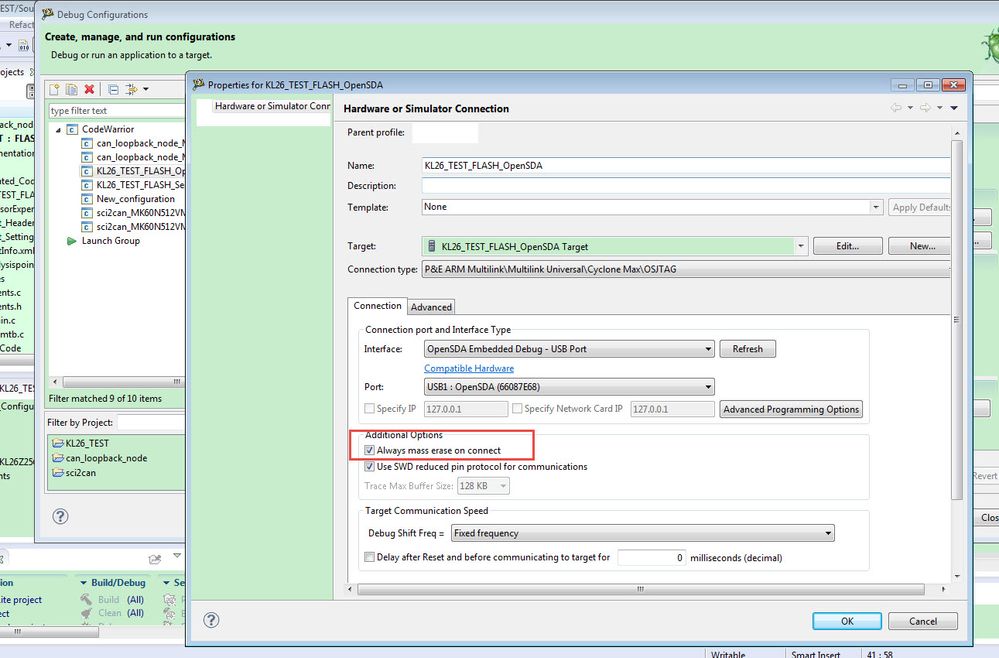

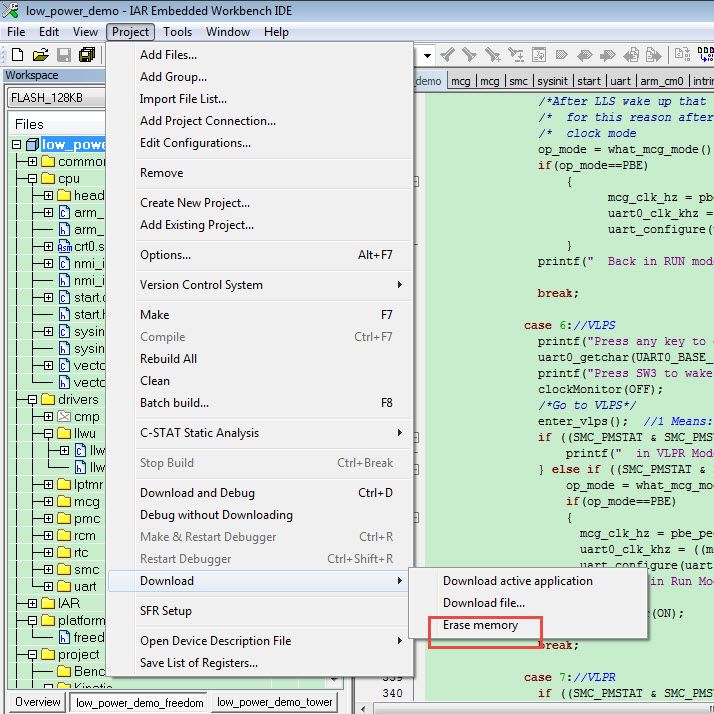

Which IDE you are using? Some IDE have the mass erase button for Multilink universal tool.

Eg, CW and KDS:

IAR:

You can try it!

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jingjing

>Take care, not the working temperature, it is the solider temperature, the chip solider to the board temperature!

I misunderstood your advice, thank you.

I customed my board by hand, so I think the MCU might get high temperature.

>Multilink Universal mass erase

I use Kinetis Design Studio(KDS.

I tried mass erase by KDS, but I coudln't connect to the MCU.

I also tried mass erase by PROGACOMP(P&E's software), but I coudln't connect to the MCU too.

I think this MCU was broken...

Regards,

Kiyoshi Matsuzaki

Re: How to order to NXP to check my MCU?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kiyoshi Matsuzaki,

Thank you for your more details.

If you solder the chip on the board by your hand, and you didn't care about the solder temperature, I think your chip maybe damaged to a large degree.

A lot of people may damage the chip when they solder the chip and never care about the temperature.

When you solder the chip by hand, take care of 2 points:

1. solder temperature below 260°C

2. solder time should as short as possible, long chip solder time may also damage the chip.

If you can't mass erase the chip and can't find the core, I suggest to solder an new chip and try again.

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------