- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- How to generate PWM using FTM with RTC Oscillator in K20 USB MCU ?

How to generate PWM using FTM with RTC Oscillator in K20 USB MCU ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello I am new to Freescale , I am using TWR-K20D50 Development Board. I want to generate a PWM Frequency of 50 Hz Through FTM. I tried using Internal reference clock but within 1-2 minutes the frequency changed to 42 Khz once or twice but I want Exact 50 Hz continuously so I am trying to use XTAL32 i.e RTC crystal attached. The code which I wrote didn't worked. Can anybody figure out what the problem is. Thanks in advance

/*****************************************************************************

* PROJECT : PWM Generation

* BOARD : TWR-K20D50M (Freescale)

* AUTHOR : Amit Kumar

* DATE : 26/08/2013

*****************************************************************************/

#include <MK20D5.H> // Header file

/*****************************************************************************

* Function to initialize RTC Oscillator

*****************************************************************************/

void PWM_RTC_Init(void)

{

SIM->SOPT1 |= SIM_SOPT1_OSC32KSEL(2); // Selecting RTC clock

SIM->SOPT2 &= ~SIM_SOPT2_PLLFLLSEL_SHIFT; // Selecting FLL Clock for various peripheral

SIM->SOPT2 |= SIM_SOPT2_CLKOUTSEL(5); // Selecting 32.768 kHz

MCG->C1 |= MCG_C1_CLKS(0) | MCG_C1_FRDIV(0); // Output of FLL Selected, FLL External Reference Divider

MCG->C1 &= ~MCG_C1_IREFS_SHIFT; // External reference clock is selected.

MCG->C4 |= MCG_C4_DMX32_MASK | MCG_C4_DRST_DRS(0); // 32.768 clock, Fll factor 640, DCO range 20-25 MHz

MCG->C6 &= ~MCG_C6_PLLS_SHIFT; // FLL is selected

MCG->C7 |= MCG_C7_OSCSEL_MASK; // Selects 32 kHz RTC Oscillator.

SIM->SCGC5 |= SIM_SCGC5_PORTC_MASK; // Creating a gating clock for PORT C

SIM->SCGC6 |= SIM_SCGC6_FTM0_MASK; // Controls the clock gate to the FTM0 module

SIM->SOPT4 |= SIM_SOPT4_FTM0TRG0SRC_MASK; // Selects the source of FTM0 hardware trigger 0

PORTC->PCR[1] |= PORT_PCR_MUX(4); // Selecting the alternative 4 of port C i.e FTM0_CH0

FTM0->SC |= FTM_SC_CLKS(3); // Selecting External Clock for Source clock

FTM0->SC |= FTM_SC_PS(4); // Selecting presaler as 0

FTM0->MOD = 52560; // Setting Modulo value

FTM0->CONTROLS[0].CnSC |= ( FTM_CnSC_MSB_MASK | FTM_CnSC_ELSA_MASK); // Rising edge counter

FTM0->CONTROLS[0].CnV = 0; // Starting PWM with initial 0 duty cycle

FTM0->CNTIN = 0; // Initial Counter value to 0

}

int main(void)

{

PWM_RTC_Init(); // Calling the function

while(1)

{

FTM0->CONTROLS[0].CnV = 2600; // Setting the PWM value

}

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Per RM, the FTM has 3 clock sources to select:

FTM source clock is selectable

• Source clock can be the system clock, the fixed frequency clock, or an external

clock

• Fixed frequency clock is an additional clock input to allow the selection of an on

chip clock source other than the system clock

• Selecting external clock connects FTM clock to a chip level input pin therefore

allowing to synchronize the FTM counter with an off chip clock source

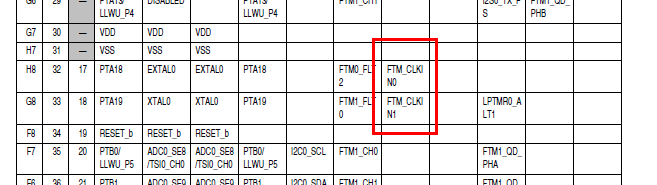

When you select the ext clock source, the clock is from the pin of FTM_CLKINx. Please kindly refer to the following for details.

You may find these pins are not from EXTAL32 pin. so I am afraid you can not use it in that way.

Sorry for the inconvenience that might cause.

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Per RM, the FTM has 3 clock sources to select:

FTM source clock is selectable

• Source clock can be the system clock, the fixed frequency clock, or an external

clock

• Fixed frequency clock is an additional clock input to allow the selection of an on

chip clock source other than the system clock

• Selecting external clock connects FTM clock to a chip level input pin therefore

allowing to synchronize the FTM counter with an off chip clock source

When you select the ext clock source, the clock is from the pin of FTM_CLKINx. Please kindly refer to the following for details.

You may find these pins are not from EXTAL32 pin. so I am afraid you can not use it in that way.

Sorry for the inconvenience that might cause.

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply. :smileyhappy:

I was wondering that can we select the RTC clock as system clock (Without putting the RTC crystal to XTAL0, just leaving it in XTAL32 )? and then we can configure the FTM clock as system clock. Is this possible ? I was trying this also but it didn't worked.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, it is possible. If you want to use RTC clock as system clock reference, then FLL should be used, MCG should be put into FEE mode, but first of all, you have to configure the RTC Oscillator with the register of RTC_CR, which is belonged to RTC module, but in the above code, I didn't find any code related with this register, so I think that might be the cause for your issue.

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey Kan_Li

Now I am trying to use external XTAL0 as a clock source for FTM0 so for that following things I have done the rest is same as the above code. I have commented up to the MCG section entirely in the function and addaed

SIM->SCGC5 |= SIM_SCGC5_PORTA_MASK; // Creating a gating clock for PORT A

PORTA->PCR[18] |= PORT_PCR_MUX(4); // assigning to FTM_CLKN0

PORTA->PCR[19] |= PORT_PCR_MUX(4); // assigning to FTM_CLKN1

OSC0->CR |= OSC_CR_ERCLKEN_MASK | OSC_CR_EREFSTEN_MASK | OSC_CR_SC8P_MASK; // External reference clock is enabled, Add 8 pF capacitor to the oscillator load.

MCG->C2 |= MCG_C2_RANGE0(1)| MCG_C2_HGO0_MASK; // High frequency range selected for the crystal oscillator, Configure crystal oscillator for high-gain operation

MCG->C6 |= MCG_C6_CME0_MASK; // External clock monitor is enabled for OSC0

and rest are the same but still it didn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

PTA18 and PTA19 are EXTAL and XTAL at default, if you use them for FTM_CLKNx function, the system OSC can not work properly as the connection between external crystal and OSC is not available , so in my opinion , you may use the EXTAL32 and XTAL32 to connect the 32,768KHz crystal , which can be used as the reference clock for MCG, and MCG can be put into FEE mode then, and on PTA 18 / 19, you may input a external clock(not crtstal) on one of them, then configure the FTM clock source from the FTM_CLKINx pin.

Hope that makes sense,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir

I want to use internal clock in run mode for 50 MHz frequency.

Please provide me the needed code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manish,

The internal ref clock is factory trimmed as 32,768KHz, so the output of FLL is 48MHz, not 50MHz, if you want to achieve 50MHz, you should manually trim the internal ref clock to 39.0625KHz, the trim needs an external crystal/ref clock as the reference, and the trim value for different part is different as well, so in factory phase, you have to calculate the trim value and store it in the internal flash, it would make the mass production a little bit complicated. so if the 50MHz is not a must option, I would suggest you let it run at 48MHz, or using an external crystal to let it run under PEE mode to get the 50MHz system clock.

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

Kindly provide me the code to get 48 Mhz internal clock in run mode.

How come it is mentioned in the datasheet that the frequency in the run mode is 50MHz ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manish,

Just as I mentioned before, 50MHz can be reached but you have to trim the internal ref clock firstly.

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kan_Li

I have written a code for configuring UART1.https://community.freescale.com/thread/312172 in this according to the datasheet UART1 works on system clock that in this case is 50 MHz so practically is it giving 50 MHz or again it is 48Mhz ?? I have tried 48M instead of 50 Mhz but still the problem is there. Kindly look into the matter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kan_Li

It is like finding needle in a haystack.

Can you please give specific few lines of code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manish,

If you refer to mcg.c, you will find two functions, int fbi_fei(int slow_irc_freq) and int fei_fbi(int irc_freq, unsigned char irc_select), you may use them in the following way to get the 48MHz core clock.

fei_fbi(32768,1);

fbi_fei(32768);

Hope that helps,

B.R

Kan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Thanks for replying. That means we have to use any one external crystal as MCG refrence clock.