- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: How can I set the MKL02Z to 48MHZ using FEI.

How can I set the MKL02Z to 48MHZ using FEI.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How can I set the MKL02Z to 48MHZ using FEI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to set my MKL02Z16 to run at 48MHZ using the internal clock (FEI mode). I had written the code manually and had set MCG_C4 to have DRST_DRS to MID range (01) and DMX32 to 1. Looking a the register description it suggested that this would give a FLL factor of 1464 and using the slow refrerence clock of 32.768KHZ I would get a DCO of approx. 48MHZ, and hence a MCGFLLCLK of 48MHZ.

I have just run through an exercise on processor expert to check my settings and although it will allow me to set a FLL factor of 1464 and does shows the correct 48MHZ frequency. It tells me it is not possible to set the requested value in the Problems Eclipse warning panel. This puzzles me. What have I overlooked or done wrong? How do I get 48MHz or is this not possible on the KL02 part?

I need to resolve this as all my peripheral clock have been set based upon a MCGFLLCLK of 48MHZ.

Thanks.

Clive

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you both for taking the time to reply. I had written the code from the RM, but then installed Processor Expert 10_4. I am using GNU tools and Eclipse.

I'm relived to know it is possible but now confused as to why it will not allow me to set it in PE. If it wont set it correctly in PE then I cant set the clocks correct for my peripheral.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Clive,

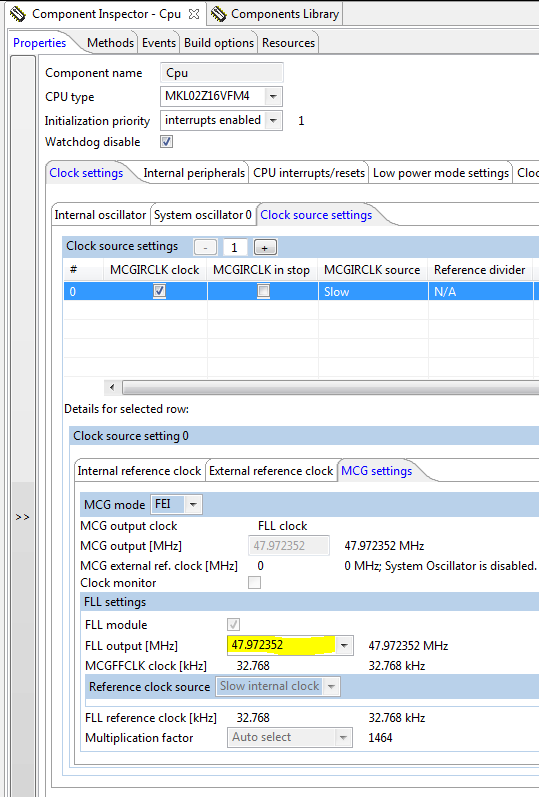

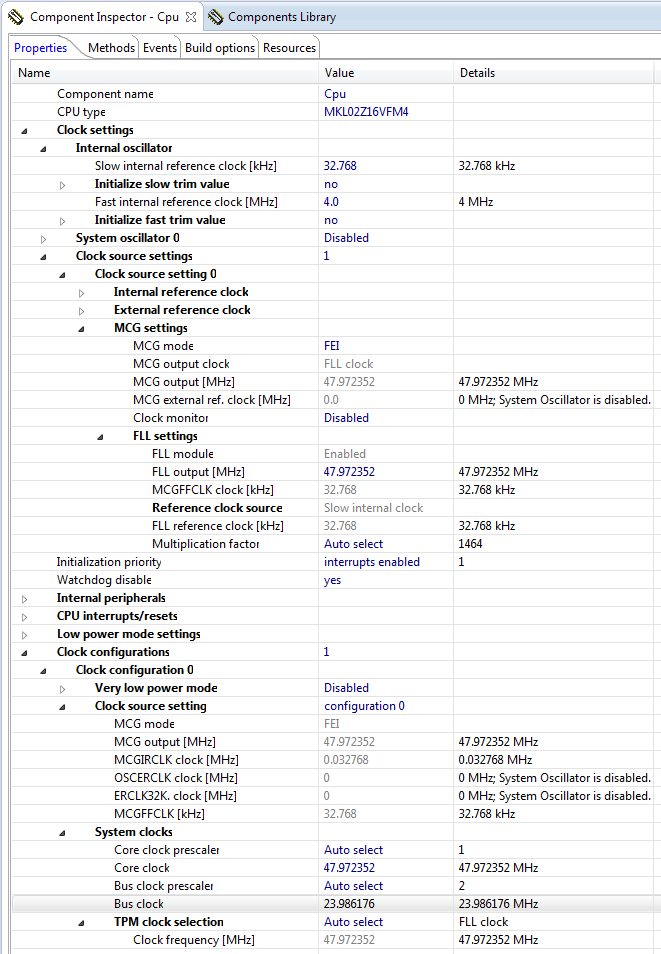

I suggest comparing your Processor Expert screen to mine (from CodeWarrior v10.6). There may be something slightly different. As I state, I don't get an error.

The only changes that I made from the default configuration were:

1) change Clock settings > Clock source settings > Clock source setting 0 > MCG settings > FLL settings > FLL output (MHz) to "48" - which gets translated to "47.972352"

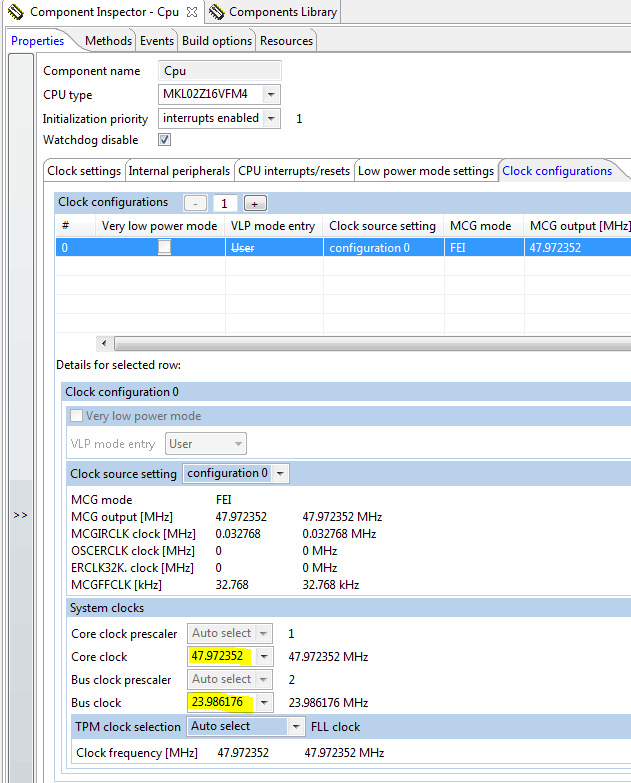

2) change Clock configurations > Clock configuration 0 > System clocks > Core clock to "48" - which gets translated to "47.972352"

3) change Clock configurations > Clock configuration 0 > System clocks > Bus clock to "24" - which gets translated to "23.986176"

When using the stand alone Processor Expert Software Microcontroller Driver Suite v10.4, these frequency changes are made via drop down menus. Here are the corresponding screen shots, with the changes highlighted, first under the "Properties" tab:

Then under the "Clock configurations" tab:

Selecting the frequencies from the menus shouldn't generate any sort of error.

Best Regards,

Derrick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Clive,

Are you using Processor Expert from within CodeWarrior or the separate tool? Current versions are:

- CodeWarrior for Microcontrollers v10.6 (with Processor Expert integrated within)

- Processor Expert Software, Microcontroller Driver Suite v10.4 (stand alone tool version)

I checked both of these and I do not see the error which you mention. Both generate the same code:

/* System clock initialization */

/* SIM_CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(0x00) | SIM_CLKDIV1_OUTDIV4(0x03)); /* Set the system prescalers to safe value */

/* SIM_SCGC5: PORTB=1,PORTA=1 */

SIM_SCGC5 |= (SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTA_MASK); /* Enable clock gate for ports to enable pin routing */

if ((PMC_REGSC & PMC_REGSC_ACKISO_MASK) != 0x0U) {

/* PMC_REGSC: ACKISO=1 */

PMC_REGSC |= PMC_REGSC_ACKISO_MASK; /* Release IO pads after wakeup from VLLS mode. */

}

/* SIM_CLKDIV1: OUTDIV1=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(0x00) | SIM_CLKDIV1_OUTDIV4(0x01)); /* Update system prescalers */

/* SIM_SOPT2: TPMSRC=1 */

SIM_SOPT2 = (uint32_t)((SIM_SOPT2 & (uint32_t)~(uint32_t)(

SIM_SOPT2_TPMSRC(0x02)

)) | (uint32_t)(

SIM_SOPT2_TPMSRC(0x01)

)); /* Set the TPM clock */

/* Switch to FEI Mode */

/* MCG_C1: CLKS=0,FRDIV=0,IREFS=1,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = MCG_C1_CLKS(0x00) |

MCG_C1_FRDIV(0x00) |

MCG_C1_IREFS_MASK |

MCG_C1_IRCLKEN_MASK;

/* MCG_C2: LOCRE0=0,RANGE0=0,HGO0=0,EREFS0=0,LP=0,IRCS=0 */

MCG_C2 &= (uint8_t)~(uint8_t)(

MCG_C2_LOCRE0_MASK |

MCG_C2_RANGE0(0x03) |

MCG_C2_HGO0_MASK |

MCG_C2_EREFS0_MASK |

MCG_C2_LP_MASK |

MCG_C2_IRCS_MASK

);

/* MCG_C4: DMX32=1,DRST_DRS=1 */

MCG_C4 = (uint8_t)((MCG_C4 & (uint8_t)~(uint8_t)(

MCG_C4_DRST_DRS(0x02)

)) | (uint8_t)(

MCG_C4_DMX32_MASK |

MCG_C4_DRST_DRS(0x01)

));

/* OSC0_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0_CR = OSC_CR_ERCLKEN_MASK;

while((MCG_S & MCG_S_IREFST_MASK) == 0x00U) { /* Check that the source of the FLL reference clock is the internal reference clock. */

}

while((MCG_S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */

}

Keep in mind that the maximum bus frequency is 24MHz. Here is how I configured this in CodeWarrior:

Best Regards,

Derrick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Clive

To set the KL02 clock to 48MHz the uTasker project does this:

OSC_CR = 0xa0

MCG_CR = 0x84

- wait for crystal source to be selected

SIM_CLKDIV1 = 0x00010000

MCG_C4 = 0xa0 // FLL factor 1464

MCG_C1 = 0

- wait until FLL source becomes valid

- wait until FLL cource is no longer the internal clock

When the external 32kHz ocillator is not used the same FLL settings are valid - but the range of the frequency tolerance is quite large.

This works reliably and the uTasker simulator checks that no values are out of range, so 1464 should not be an issue.

Regards

Mark