- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- GPIO protection

GPIO protection

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to datasheet K10P144M100SF2V2 GPIO only have clamp diode to VSS. I need EOS protection up to +24V.

I can experiment and find what works but I will like to understand GPIO characteristics.

Can I use a series 10K resistor for protection?

Will it cause latchup because 24V > Max 5~5.5V even though it can't drive latch up current of 100ma?

What will be the voltage at pin?

What is the reverse break down voltage of clamp diode?

Will I I definitely need another clamp diode to VDD as well ? Why?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Only using a series 10K resistor for EOS protection is not permitted.

For Digital inputs only have a diode to VSS, allowing negative injection but not positive injection

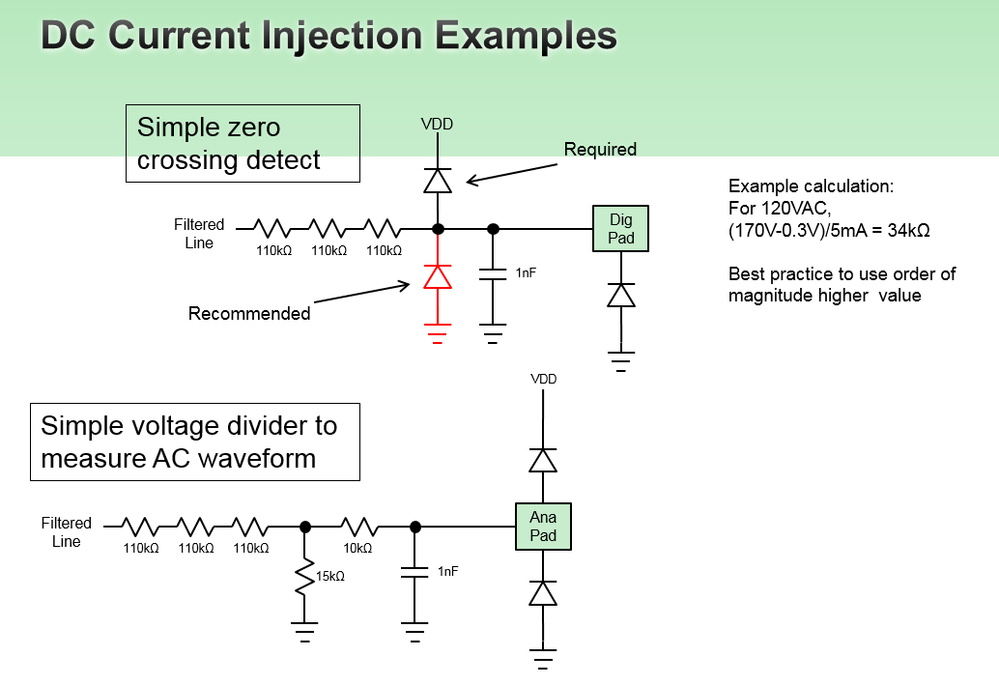

Please check below picture about K10 GPIO pin protection circuit:

Dig Pad for digital function pin, such GPIO pin; Ana Pad for analog function pin, such as ADC channel.

The other recommend way is using a TVS diode between 10K serial resistor with K10 GPIO pin.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

K10 100MHz product all GPIO pins have 5 V tolerance.

All 5 V tolerant digital I/O pins are internally clamped to VSS through an ESD protection diode. There is no diode connection to VDD.

Circuit design and PCB layout are fundamental in preventing EOS conditions from reaching the device.

There are several publications that offer great advice on properly designing circuits to prevent overstress conditions.

The recommendations in the publications concentrate on the following:

• Clean VCC and VSS Supplies:

- Avoid excessive ringing and power-up overshoot/undershoot

• Controlled VCC Ramp at Power-up and Power-Down:

- Too fast power-up or power-down could cause excessive inrush currents through the circuit

• Proper Power/Ground:

- Avoid ground loops and ground differentials

• Correct Decoupling Capacitor Values:

- Essential for filtering high-frequency spikes

• Data Bus Contentions

• Connecting External Cable to an Unprotected I/O Port

• Proper Component Placement

• Short Trace Lengths

K10 most GPIO pin are in high impedance status during power up.

Using a current-limiting resistor and a ferrite bead with a capacitor to ground will limit the energy transferred to a pin during an EOS event.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ma Hui,

I will like to thank you for replying and also thanks for a polite and long reply with known generic information.

BTW I have read some of your replies here and I have experience in interacting with many semi vendor support sites. So I am aware what kind I support I expect.

I don't know what is your official association with NXP and if this reply is on behalf of NXP.

If this is official response from NXP support staff then it is pathetic and useless generic response.

If you are replying as a community gesture. I have a suggestion for you. Please only reply if you have specific answers.

But NXP is not exception response at most vendor community sites is poor and sometimes I have to get answers by approaching official customer support.

Regards,

Tejpal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Only using a series 10K resistor for EOS protection is not permitted.

For Digital inputs only have a diode to VSS, allowing negative injection but not positive injection

Please check below picture about K10 GPIO pin protection circuit:

Dig Pad for digital function pin, such GPIO pin; Ana Pad for analog function pin, such as ADC channel.

The other recommend way is using a TVS diode between 10K serial resistor with K10 GPIO pin.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------