- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- GPCLR_WR does not work???

GPCLR_WR does not work???

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Good morning.

I am trying to use the HW_PORT_GPCLR_WR without success.

In this stub of code the kGpioEncMux2 kGpioEncMux1 kGpioEncMux0 are the bit 9 8 7 of the PORTC.

The GPIO_HAL_WritePinOutput works, but if I try to use the HW_PORT_GPCLR_WR it does not...

The bit of the register appear to be correct, but the output is different.

Suggestions???

typedef union _mux_bits_t

{

struct

{

uint32_t sp : 7;

uint32_t mux : 3;

uint32_t sp2 : 22;

};

struct

{

uint32_t sp3 : 23;

uint32_t muxact : 3;

uint32_t sp4 : 6;

};

uint32_t val;

} avago_mux_bits_t;

avago_mux_bits_t mux_bits = { 0 };

void inline static avago_mux_out( uint8_t muxval )

{

muxval ^= 0xFF; // just negate for the ULN open collector

mux_bits.mux = muxval;

mux_bits.muxact = 7;

HW_PORT_GPCLR_WR( g_portBaseAddr[ GPIO_EXTRACT_PORT(kGpioEncMux2) ], mux_bits.val );

GPIO_HAL_WritePinOutput( g_gpioBaseAddr[ GPIO_EXTRACT_PORT( kGpioEncMux2 ) ], GPIO_EXTRACT_PIN( kGpioEncMux2 ), muxval & 4 );

GPIO_HAL_WritePinOutput( g_gpioBaseAddr[ GPIO_EXTRACT_PORT( kGpioEncMux1 ) ], GPIO_EXTRACT_PIN( kGpioEncMux1 ), muxval & 2 );

GPIO_HAL_WritePinOutput( g_gpioBaseAddr[ GPIO_EXTRACT_PORT( kGpioEncMux0 ) ], GPIO_EXTRACT_PIN( kGpioEncMux0 ), muxval & 1 );

}

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

I check your code which you past,

HW_PORT_GPCLR_WR( g_portBaseAddr[ GPIO_EXTRACT_PORT(kGpioEncMux2) ], mux_bits.val );

This is not correct, because HW_PORT_GPCLR_WR definition is like following in our KSDK:

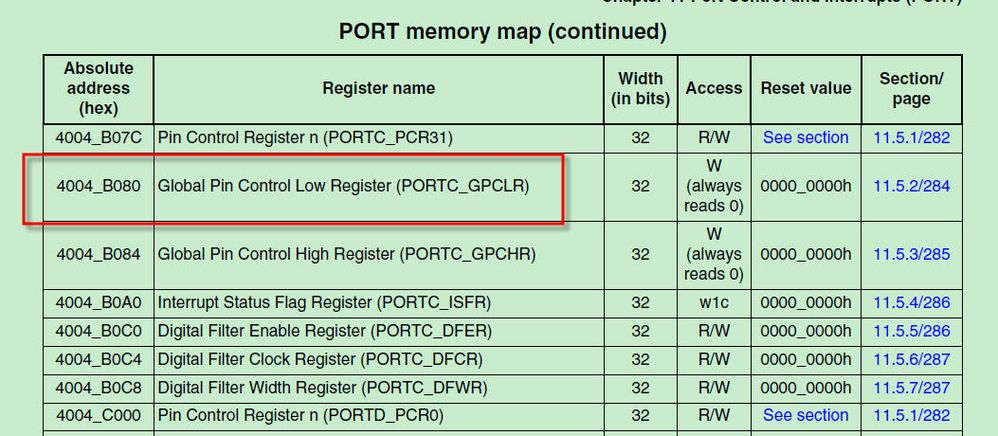

| #define HW_PORT_GPCLR_ADDR(x) | ((uint32_t)(x) + 0x80U) |

| #define HW_PORT_GPCLR(x) | (*(__O hw_port_gpclr_t *) HW_PORT_GPCLR_ADDR(x)) |

| #define HW_PORT_GPCLR_RD(x) | (HW_PORT_GPCLR(x).U) |

#define HW_PORT_GPCLR_WR(x, v) (HW_PORT_GPCLR(x).U = (v))

x: is the base address of PORTC, it is 0x4004_B000. then x+0x80 =0x4004_B080

So, you should configure it like this :

HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

This will configure the PORTC_PCR7, PORTC_PCR8 and PORTC_PCR9.

I test it, it can works ok on my side with HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

Following are my test result:

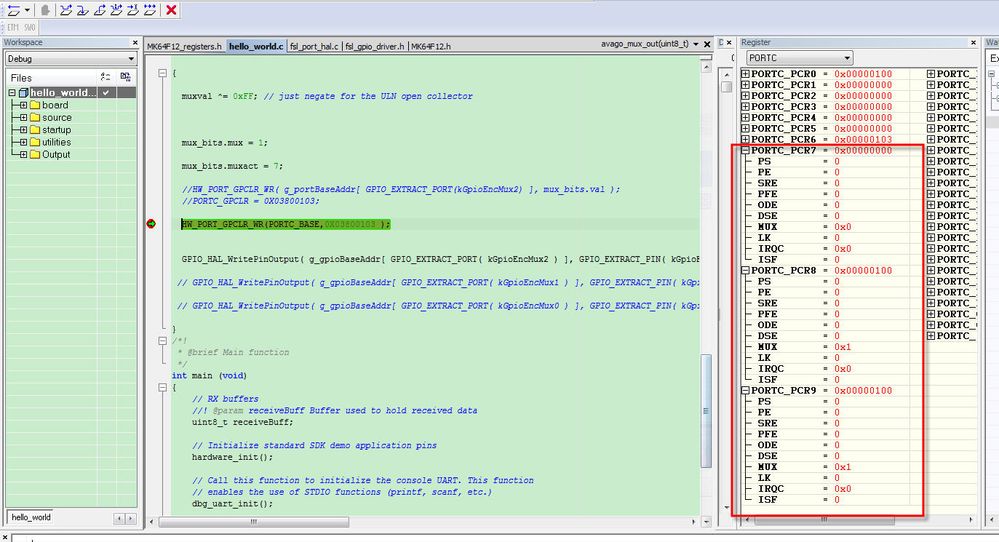

(1)Before run :HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

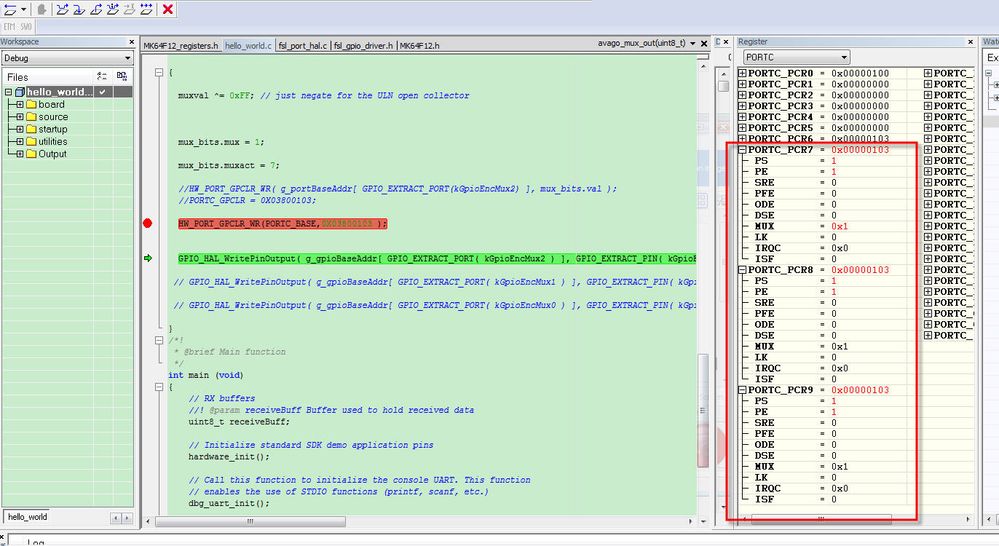

(2) After run ::HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

So, please modify your code and test again.

Any question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I appreciate the effort. I am not able to make it work. I need to give up for now I can live with normal writing.

Thank You

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

I check your code which you past,

HW_PORT_GPCLR_WR( g_portBaseAddr[ GPIO_EXTRACT_PORT(kGpioEncMux2) ], mux_bits.val );

This is not correct, because HW_PORT_GPCLR_WR definition is like following in our KSDK:

| #define HW_PORT_GPCLR_ADDR(x) | ((uint32_t)(x) + 0x80U) |

| #define HW_PORT_GPCLR(x) | (*(__O hw_port_gpclr_t *) HW_PORT_GPCLR_ADDR(x)) |

| #define HW_PORT_GPCLR_RD(x) | (HW_PORT_GPCLR(x).U) |

#define HW_PORT_GPCLR_WR(x, v) (HW_PORT_GPCLR(x).U = (v))

x: is the base address of PORTC, it is 0x4004_B000. then x+0x80 =0x4004_B080

So, you should configure it like this :

HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

This will configure the PORTC_PCR7, PORTC_PCR8 and PORTC_PCR9.

I test it, it can works ok on my side with HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

Following are my test result:

(1)Before run :HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

(2) After run ::HW_PORT_GPCLR_WR(PORTC_BASE,0X03800103 );

So, please modify your code and test again.

Any question, please contact me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

Could you tell me the full name of your chp and where you get the code.

You can control the PORTx_GPCLR and PORTx_GPCHR register directly, this will work fine.

Waiting for your reply!

Jingjing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hei Jingjing

Thank You for follow up.

I am using the FRDM K64.

I hope You can solve the arcan.

Thank You

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

GPCLR is define the bits[15:0] of PORTx_PCRn, it includes pin mux control , pull select, pull enable,etc.

Did you configure your PTC7,PTC8,PTC9 as GPIO(MUX = 1), please check the according register:PORTC_PCR7,PORTC_PCR8,PORTC_PCT9.

Besides, check your GPIOC_PDDR, GPIOC_PDOR, whether you configure it as the output, and the pin out voltage is correct or not.

please give me your register debug picture, and your testing project.

Regards.

Jingjing