- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- External oscillator on MKL27

External oscillator on MKL27

Hello!

I am currently trying to enable/use a 12 MHz external oscillator on a design with a MKL27Z256. The software was previously running with the internal clock. I cannot remember exactly where the original files came from, but they are copyright Freescale, with a build identification b140923 for rev 1.3, so presumably the Kinetis SDK 1.3 (?) Now, we have added an external crystal.

These files include (edited version attached) some defins like CPU_XTAL_CLK_HZ and some predefined settings for the MCGLite registers according to CLOCK_SETUP with some pre-defined example settings.

By adjusting option 5 somewhat, I got the device to boot; however, it did require both misconfiguration of the macros, adjustment of the values (which to me seemed incorrect compared to the data sheet, and definitely wrong when compared to reality.) Currently I'm rather confused as to whether my setting is correct.

#define CPU_XTAL_CLK_HZ 24000000u /* strange? Value of the exter

nal crystal or oscillator clock frequency in Hz is 12 MHz really */

#define CPU_INT_FAST_CLK_HZ 48000000u /* Value of the fast

internal oscillator clock frequency in Hz */

#define CPU_INT_IRC_CLK_HZ 48000000u /* Value of the 48M i

nternal oscillator clock frequency in Hz */

#elif (CLOCK_SETUP == 5)

#define DEFAULT_SYSTEM_CLOCK 48000000u /* Default System clock value */

#define CPU_INT_SLOW_CLK_HZ 8000000u /* Value of the slow internal oscillator clock frequency in Hz */

#define MCG_MODE MCG_MODE_EXT /* Clock generator mode */

/* MCG_C1: CLKS=2,IRCLKEN=0,IREFSTEN=0 */

#define MCG_C1_VALUE 0x82u /* MCG_C1 */

/* MCG_C2: RANGE0=3,HGO0=0,EREFS0=1,IRCS=1 */

#define MCG_C2_VALUE 0x25u /* MCG_C2; should be 0x25, not 0x2d */

/* MCG_SC: FCRDIV=0 */

#define MCG_SC_VALUE 0x00u /* MCG_SC */

/* MCG_MC: HIRCEN=0 LIRC_DIV2=0 */

#define MCG_MC_VALUE 0x00u /* MCG_MC */

/* OSC0_CR: ERCLKEN=1,EREFSTEN=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

#define OSC0_CR_VALUE 0x80u /* OSC0_CR */

/* SMC_PMCTRL: RUNM=0,STOPA=0,STOPM=0 */

#define SMC_PMCTRL_VALUE 0x00u /* SMC_PMCTRL */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV4=1 */

#define SYSTEM_SIM_CLKDIV1_VALUE 0x10000u /* SIM_CLKDIV1 */

/* SIM_SOPT1: OSC32KSEL=0,OSC32KOUT=0 */

#define SYSTEM_SIM_SOPT1_VALUE 0x00000000u /* SIM_SOPT1 */

/* SIM_SOPT2: LPUART1SRC=0,LPUART0SRC=0,TPMSRC=3,FLEXIOSRC=0,USBSRC=0,CLKOUTSEL=0,RTCCLKOUTSEL=0 */

#define SYSTEM_SIM_SOPT2_VALUE 0x03000000u /* SIM_SOPT2 */

#else

#error The selected clock setup is not supported.

#endif /* (CLOCK_SETUP == 5) */

Also, the SystemInit() routine seemed to hang forever, if the HCG0 bit is set direcly in MCG_S2, -- only when setting the HCG0 bit after having the previous check on the status check finish, was I able to set the clock (however, if not in high gani mode, it seemed that I at least failed to get correct timings as well.)

The wrong setting in the CPU_XTAL_CLK_HZ was needed, or SystemCoreClockUpdate() returned a wrong reading?

Now, system_MKL17Z644.h/.c hint at a different CPU version as well?

Does anybody have a concise example of how to set the MKL27Z256 to use an external crystal oscillator at 12 MHz and a matching SystemCoreClockUpdate() to subsequently update SystemCoreClock, and get a correct 1 ms tick (i.e. get SysTick_Config() result in correct settings.) Right now I'm confused and slightly unsure if my programming of the clock is correctly, and even what the resulting CPU clock ends up at!

Original Attachment has been moved to: system_MKL17Z644.c.zip

Original Attachment has been moved to: system_MKL17Z644.h.zip

已解决! 转到解答。

Hi Jaakko,

Please refer to the attachment.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Jaakko,

Please refer to the attachment.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Jaakko,

Please use the modified code below to configure the Core clock and Bus clock run at the 12 MHz and MCG_Lite works in the EXT mode.

#elif (CLOCK_SETUP == 5)

| #define DEFAULT_SYSTEM_CLOCK | 12000000u | /* Default System clock value */ |

| #define CPU_INT_SLOW_CLK_HZ | 8000000u | /* Value of the slow internal oscillator clock frequency in Hz */ |

| #define MCG_MODE | MCG_MODE_EXT | /* Clock generator mode */ |

/* MCG_C1: CLKS=2,IRCLKEN=1,IREFSTEN=0 */

| #define MCG_C1_VALUE | 0x82U | /* MCG_C1 */ |

/* MCG_C2: RANGE0=1,HGO0=1,EREFS0=1,IRCS=1 */

| #define MCG_C2_VALUE | 0x1DU | /* MCG_C2 */ |

/* MCG_SC: FCRDIV=1 */

| #define MCG_SC_VALUE | 0x02U | /* MCG_SC */ |

/* MCG_MC: HIRCEN=1,HIRCLPEN=0,LIRC_DIV2=0 */

| #define MCG_MC_VALUE | 0x80U | /* MCG_MC */ |

/* OSC0_CR: ERCLKEN=1,EREFSTEN=0,SC2P=0,SC4P=1,SC8P=1,SC16P=0 */

| #define OSC0_CR_VALUE | 0x86U | /* OSC0_CR */ |

/* SMC_PMCTRL: RUNM=0,STOPA=0,STOPM=0 */

| #define SMC_PMCTRL_VALUE | 0x00U | /* SMC_PMCTRL */ |

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV4=0 */

| #define SYSTEM_SIM_CLKDIV1_VALUE | 0x00U | /* SIM_CLKDIV1 */ |

/* SIM_SOPT1: OSC32KSEL=3,OSC32KOUT=0 */

| #define SYSTEM_SIM_SOPT1_VALUE | 0x000C0000U | /* SIM_SOPT1 */ |

/* SIM_SOPT2: LPUART1SRC=0,LPUART0SRC=0,TPMSRC=0,FLEXIOSRC=0,USBSRC=0,CLKOUTSEL=0,RTCCLKOUTSEL=0 */

| #define SYSTEM_SIM_SOPT2_VALUE | 0x00U | /* SIM_SOPT2 */ |

#else

#error The selected clock setup is not supported.

#endif /* (CLOCK_SETUP == 5) */

Hope it helps.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thanks! -- this makes the reported systicks match the external clock define. However: still no luck in the startup; I get stuck in system_MKL17Z644.c in the following

if (((MCG_C2_VALUE) & MCG_C2_EREFS0_MASK) != 0U) { while((MCG->S & MCG_S_OSCINIT0_MASK) == 0x00U) { /* Check that the oscillator is running */ }

}This is basically the other problem I have with my "seemingly working" solution I do not understand: why do I get stuck in this instruction with the the settings I have (specifically it's the HCG0 bit?!) I can get past this instruction by setting HCO0 to 0 in the debugger and continuing. If I leave HCO0=0, the result is that the software will seemingly linger on, -- even keep time correctly, -- however, the software, which acts as a SPI slave device, will fail to communicate. I can toggle the HCG0 bit and it seems to directly affects the external communication; if HCG0=0, transactions fail, while if HCGO=1, I get stuck in the line above?!

I am not really happy with setting the HCG0=1 after passing the line above, as I do not understand the logic at play. (I have not reviewed the rest of the bits in the configuration yet, but at least the reported clock frequency seems to match now!)

Hi Jaakko,

I'm sorry to hear that the issue still exists.

So I'd like to suggest that you can use the KDS which can integrate the KSDK and Processor Expert tool.

And the Processor Expert provides an efficient development environment for rapid application development of the embedded applications, so it's easy to create the SystemInit() function to configure the MCU works in the EXT Mode.

And about the HCG0 bit, I don't find the it in the RM, can you tell me which page it locates on?

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

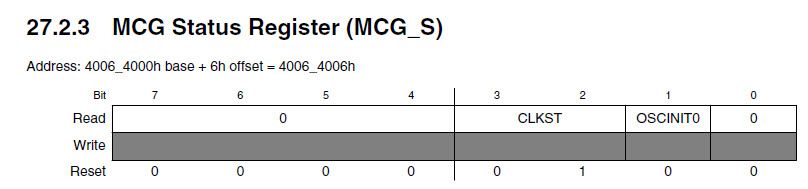

The HCG0 bit is in the MCG_C2 register, which is visible on page 454, §27.1.2 block diagram on the lower left and described in §27.2.2 (MCG_S2) on page 436 of KL27 Sub-family reference manual , Rev. 5, 01/2016 (for the 128/256 KiB flash variants.)

(Sorry for the late reply.) The issue still persists, and actually seems even more critical than original reported. Noticed, that after having used the ROM bootloader for a software update and reseting back, the startup code will actually once again sit in the busy loop waiting for the clock status bit (now forever.) Practically the same sequence was used before twice (there's a separate bootloader which jumps to the actual application, both use the same startup code (separate copy.) I.e. the clock entry routine should work when entered again. -- this seemingly works, but I cannot really tell due to what causes this to fail here (more time has elapsed?)

Any help greatly appreciated! What to verify in this (I do not really understand the meaning of the HCG bit?) Can crystal or supply voltage changes cause effects like this? Is there a fire-proof way to get the external clock running (from any previous setting?)