- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: DMA and CACHE

DMA and CACHE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a KE18F MCU.

I am using DMA to transfer received UART data into a circular queue. I use the DADDR of the DMA channel that handles these actions and a pointer of "read" data to determine if new data has been put into the queue.

I am concerned that when I read my data queue, I will read what is in cache, instead of the what's actually in my queue. Since there is no DMA coherency with cache.

I am wondering if I would need to search the cache and invalidate any data that is from my data queue when it comes time to process the received data, since the data was moved into the queue by DMA?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sean,

In this case, you are right, you do not need to worry about the cache, because you are using the FlexRAM and it is not cacheable.

2. Non-cacheable — access to address spaces with this cache mode are not cacheable.

These accesses bypass the cache and access the output bus. In other words, it doesn't affect this process.

Regards,

Mario

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sean,

I hope you are doing great.

You are passing the UART received from UART to a circular buffer. What do you mean cache in this case?

You only have to be sure that you read out the data from the circular buffer before the DMA writes again to that section.

Regards,

Mario

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am referring to when I process what is in my queue. The data is moved into the queue by DMA, but there is no cache hardware coherency. So when my software comes to reading the queued data, I am concerned what I might read. Will I read what is in cache, or in RAM?

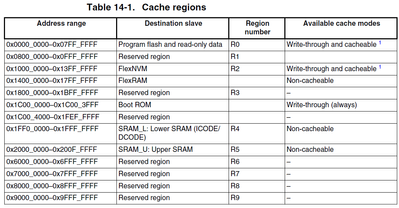

I did read though in table 14-1 in the KE18F manual that RAM is non-cacheable. Can you confirm if this means that I don't have worry about this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sean,

In this case, you are right, you do not need to worry about the cache, because you are using the FlexRAM and it is not cacheable.

2. Non-cacheable — access to address spaces with this cache mode are not cacheable.

These accesses bypass the cache and access the output bus. In other words, it doesn't affect this process.

Regards,

Mario