- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- DMA MUX Configuration source selection in AN4590

DMA MUX Configuration source selection in AN4590

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

DMA MUX Configuration source selection in AN4590

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Every one.

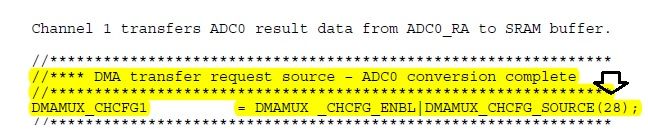

I am using the DMA to get the ADCs result to a buffer as stated in AN4590 application note.

In the note during DMAMUX channel request source selection I am confused how the source number is given. like for ADC0 they have given 0X28 and for other channel its 0X36. My question is where does these 0x28 and 0x36 comes from and in which section of configuration manual r they stated? i have seen ADC and DMA and DMAMUX chapters but I couldnt find that.

here are the lines from AN4590

Regards

Abdullah

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

See the "Chip Configuration" section chapter of the user's manual. Then the "DMA request multiplexer configuration" in it.

This gives a list of the DMA request sources for MUX 0 (and MUX 1 for bigger chips).

eg.

UART0 Rx is 2

UART0 Tx is 3

UART1 Rx is 4

UART1 Tx is 5

..

ADC0 is 40 (0x28)

>>for other channel its 0X36

Double-check this because it looks wrong: ADC1 is 0x29, ADC2 is 0x2a (on MUX 1 only) and ADC3 is 0x2b (on MUX 1 only).

Personally I don't like the code

DMAMUX_CHCFG = DMAMUX_CHCFG_ENBL | DMAMUX_CHCFG_SOURCE(28)

because it doesn't show whether the value 28 is hex or decimal, and also it is processor type dependent, in case a derivative were to have a different channel (which is not to necessarily to exclude is the future).

I prefer

DMAMUX_CHCFG = DMAMUX_CHCFG_ENBL | DMAMUX_CHCFG_SOURCE_ADC0

where

#define DMAMUX_CHCFG_SOURCE_ADC0 DMAMUX_CHCFG_SOURCE(28)

or simply

#define DMAMUX_CHCFG_SOURCE_ADC0 0x28

or to better match the user's manual, even

#define DMAMUX_CHCFG_SOURCE_ADC0 40

In this case the user doesn't even need to ask him-/herself where this strange number comes from (unless he/she really wants to understand all details). When the details are desired, the user can search for the define in question and immediately arrives at the complete list in a header file associated with the register and then still no further questions needed...

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark.

I have a code running that is using ADC to trigger DMA. and when destination buffer (configured in DMA settings) is full, An Interrupt is generated. In that ISR of DMA I am copying that buffer into SD card and then giving the DMA its next destination buffer (which is one of the buffer from the buffer pool i have created).

What i am doing is I am configuring the DMA again (with all its parameters same but destination buffer changed), i did it by just changing the destination buffer in DMA settings and pretending the rest remaining same as before but it didnt. So ihave to reconfigure DMA from zero again and again while in DMA ISR.

Do you suggest any better and optimal way of just changing the DMA destination buffer (keeping the old settings of transfer size and reset address same in DMA setings).

Regards

Abdullah

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I would recommend setting up a single buffer which automatically restarts after completion (circular) with interrupts at half-full and full. This way you don't need to modify the DMA confuguration during operation and also have no risk of losing samples when moving from one buffer to the other.

This is detailed in http://www.utasker.com/docs/uTasker/uTaskerADC.pdf

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark.

Thanks for a very nice and simplified explanation. That really helped me. I liked your opinion of defining the source as a macro.

Thumbs up for your stuff.

Regards

Abdullah