- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Continuous Overwrite of C(n)V register with FTM Input Capture

Continuous Overwrite of C(n)V register with FTM Input Capture

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I would like to continuously capture both rising and falling edges on two separate pins using dual edge capture on an FTM module on a K64. Is it possible to set up the capture registers C(n)V to be continuously overwritten, even if I am not reading the register and clearing the CH(n)F bit with each new edge?

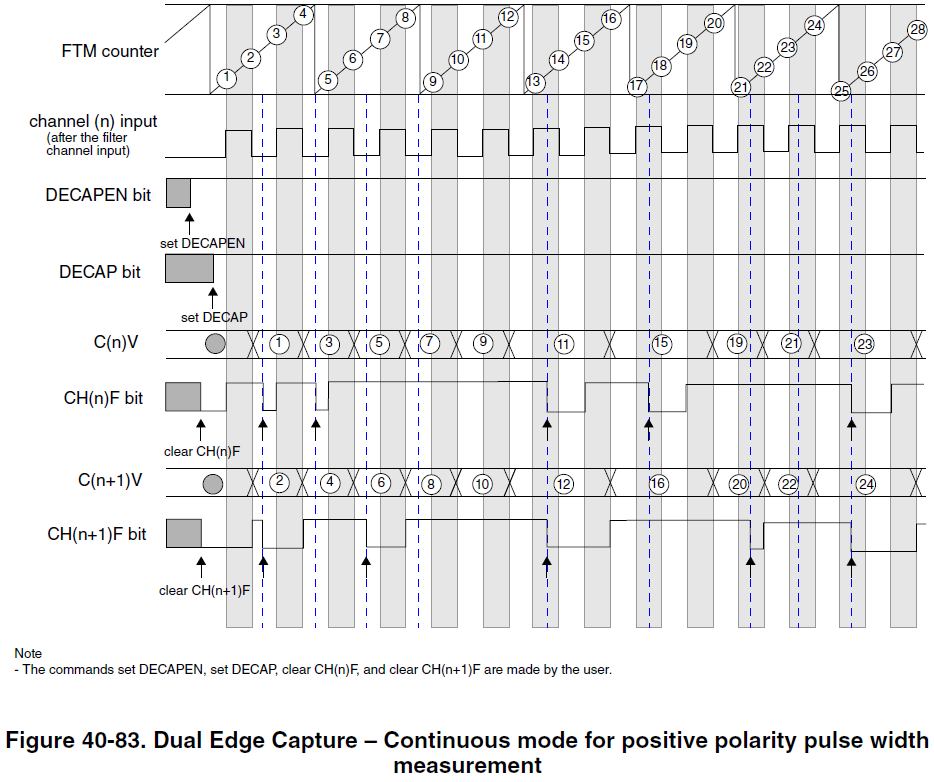

I can't afford to service each edge as it comes in, so my goal is to fire an ISR on the FTM overflow, and then read the input captured time of the most recently-received edge, which could be on any of the four registers (corresponding to rising or falling edges on each of my two pins). From Fig. 40-83 in the K64 Reference Manual, it is not clear whether I need to clear the CH(n)F and CH(n+1)F registers in order to capture the next edge.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured this out:

- if you never clear the CH(n)F bit, the C(n)V register will be constantly updated to the latest value (see e.g. the sequence of events from (7) - (10) in the above figure).

- if you do clear the CH(n)F bit after a rising edge but before a falling edge, you can prevent the next pair of events from being captured (see e.g. the sequence of events from (11) - (14) above). However, clearing the CH(n+1)F bit after a rising edge but before a falling edge does not have the same effect, since it will simply be re-set on the next falling edge, causing both the most recent rising edge and falling edge to be captured to the C(n)V and C(n+1)V registers, respectively.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured this out:

- if you never clear the CH(n)F bit, the C(n)V register will be constantly updated to the latest value (see e.g. the sequence of events from (7) - (10) in the above figure).

- if you do clear the CH(n)F bit after a rising edge but before a falling edge, you can prevent the next pair of events from being captured (see e.g. the sequence of events from (11) - (14) above). However, clearing the CH(n+1)F bit after a rising edge but before a falling edge does not have the same effect, since it will simply be re-set on the next falling edge, causing both the most recent rising edge and falling edge to be captured to the C(n)V and C(n+1)V registers, respectively.