- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Clocks Configuration problem

Clocks Configuration problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clocks Configuration problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

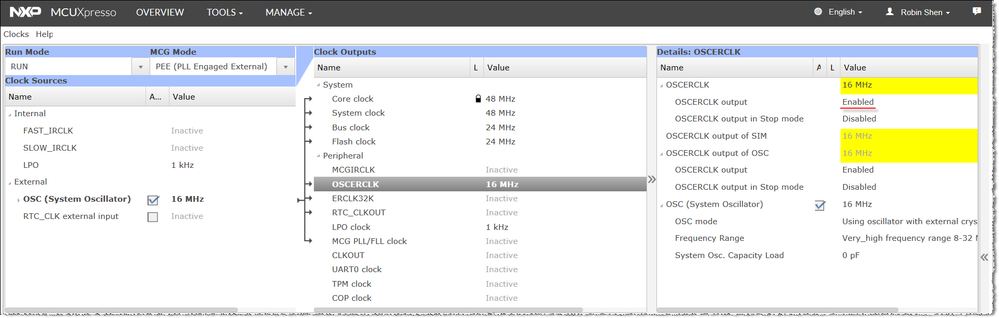

I want to SDK2.0 instead of Processor Expert. I have used „Clocks Configuration“ for clock configuration (export it attachment) and replaced directory in my project (made in KDS3.2) with this export. Program ends in „CLOCK_SetExternalRefClkConfig(oscsel);“ at „while (!(MCG->S & MCG_S_OSCINIT0_MASK))“. I have tried to enable pins for EXTAL0 and XTAL0. Is there anyone who knows, where is mistake? Is there any manual for web configurator?

I am using KL16Z128 with external crystal 16MHz and KDS3.2 with SDK2.0.

Thanks.

Original Attachment has been moved to: MKL16Z128xxx4_pins_sources_2017-01-23_14_06.zip

Original Attachment has been moved to: MKL16Z128xxx4_clocks_sources_2017-01-23_12_39.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry for the late reply!

Please try to enable the OSCERCLK.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have posted on a similar problem with the TWR-60DN. We are getting a hard fault in the clock module. I think the code generated is bad. It was noticed by an NXP moderator and he asked for more information last week, but have heard nothing since. So maybe you do not have a problem with your clock. What does work is the "Hello World" project from the Freertos site, at least for the TWR-60DN. As a suggestion you could try loading and running that project and see if you still have a clock problem. You don't need to bother with more than putting a break point in the first statement in Main.c. If you get that far your clock is ok.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for advice but I would rather use „Clocks Configuration“ instead. It allows me to set various clock modes in processor. Besides if NXP provides this tool, it should work. HW is fine and project with Processor expert works as well with external crystal. I want to use „Clocks Configuration“ for KL16Z128 with external crystal 16MHz in PEE mode. Does anybody knows how to make it work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

This code will configure the KL16 to run in PEE at 48Mz (24MHz bus/flash) for a 16MHz crystal.

I show the actual register value writes in brackets []:

MCG_C2 = (MCG_C2_RANGE_8M_32M | MCG_C2_GAIN_MODE | MCG_C2_EREFS | MCG_C2_LOCRE0); // [0xa4 for low gain mode or 0xac for high gain mode] select crystal oscillator and select a suitable range

MCG_C1 = (MCG_C1_CLKS_EXTERN_CLK | MCG_C1_FRDIV_512); // [0xa0] switch to external source (the FLL input clock is set to as close to its input range as possible, although this is not absolutely necessary if the FLL will not be used)

while ((MCG_S & MCG_S_OSCINIT) == 0) {} // loop until the crystal source has been selected

while ((MCG_S & MCG_S_IREFST) != 0) {} // loop until the FLL source is no longer the internal reference clock

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_EXTERN_CLK) {} // loop until the external reference clock source is valid

MCG_C5 = ((CLOCK_DIV - 1) | MCG_C5_PLLSTEN0); // [0x27] now move from state FEE to state PBE (or FBE) PLL remains enabled in normal stop modes

MCG_C6 = ((CLOCK_MUL - MCG_C6_VDIV0_LOWEST) | MCG_C6_PLLS); // [0x58] set the PLL multiplication factor

while ((MCG_S & MCG_S_PLLST) == 0) {} // loop until the PLLS clock source becomes valid

while ((MCG_S & MCG_S_LOCK) == 0) {} // loop until PLL locks

SIM_CLKDIV1 = (((SYSTEM_CLOCK_DIVIDE - 1) << 28) | ((BUS_CLOCK_DIVIDE - 1) << 16)); // [0x10010000] prepare bus clock divides

MCG_C1 = (MCG_C1_CLKS_PLL_FLL | MCG_C1_FRDIV_1024); // [0x28] finally move from PBE to PEE mode - switch to PLL clock

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_PLL) {} // loop until the PLL clock is selected

Note that the MCG_C2 value depends on whether the crystal circuit needs high or low gain (whether it has feedback resistor and loading capacitors).

If set incorrectly the crystal will not start oscillating and you will get stuck waiting for the crystal source to be selected.

Regards

Mark

KL16/KL26: http://www.utasker.com/kinetis/FRDM-KL26Z.html

MCG: http://www.utasker.com/kinetis/MCG.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Mark for advice and I will test it for sure. MCG description is very understandable and useful. But I still would like to learn how to use "Clocks Configuration" tool. If it is provided by NXP (Qualcom) then I would like to use it. It seems that work with it should be easy. That is why I do not understand why there is nobody who can say what I am doing wrong and give me some kind of manual how to use "Clocks Configuration".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

For Kinetis development the clock configuration represents a few lines of code and so probably 0.0001% of any project (it will already exist in a decent library). I have set this up for more than 250 Kinetis parts and configurations and never though of needing a tool to help since it is more flexible to understand the simple basics and just do it exactly as one wants.

I would invest energy in completing work accurately and well than getting annoyed with the manufacturer. These tools are basically PR gags to get people hooked on their chips, so shouldn't be an issue for professional developers.

Regards

Mark