- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Clarification needed for MK70 DDR control register 21 specification

Clarification needed for MK70 DDR control register 21 specification

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Clarification needed for MK70 DDR control register 21 specification

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello all,

I am running into an issue with a MK70FX512VMJ12 controlling the DDR on a legacy board.

We are using MQX. The issue comes from the following line in the bootloader:

ddr->CR21 = 0x00060232; I assume that line sets the DDR_CR21 register (as described on the section 34.4.22 of the K70 reference manual) to 0x00060236.

The reference manual states that the register field is split into 2 fields.

31–16 MR1DAT0 Data to program into memory mode register 1 for chip select .

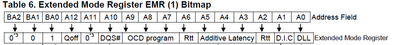

15–0 MR0DAT0 Data to program into memory mode register 0 for chip select .Most DDR manufacturers call those registers Mode Register (MR or MRS) and Extended Mode Register (EMR1, EMR2, EMR3). Should I assume that data from field 15-0 will be written by the state machine to the DDR's MR (Mode Register) and data from field 31-16 to EMR?

I suspect, and need confirmation from support engineers, that the state machine issues the necessary control signals irrespective of the values set in the DDR_CR21. That is because considering the data I write on bits 31-16 of the DDR_CR21 (0x0006) which assigns 000 to the 3 MSB bits, for proper operation those should be set to 001 as required by DDR specifications.

Note from DDR specs: "The extended mode register is written by asserting LOW on CS#, RAS#, CAS#, WE#, BA1 and HIGH on BA0, while controlling the states of address pins A0 ~ A12."

The settings needed for BA2, BA1, and BA0 are '001', while the values I write to DDR_CR21 is '000'.

Does the DDR SDRAM controller overwrites those values set in DDR_CR21 to the correct ones?

Thank you,

dodocolby

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @dodocolby ,

Hope you are great. I am sorry for the late reply. Please see the reply from our internal team:

"

Because the DDR controller can support many different memory sizes and configurations with different total numbers of address pins, the mode register data loaded into the MRnDATA fields should not include the bank address values. The controller will automatically drive the correct bank address value (along with the other control signals for the mode register write command). The register value only needs to include the address line portion.

"

Hope it helps. Please let me know if you have other questions.

BR

Celeste

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @dodocolby ,

Could you please let me know the mask set of your chip?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am using MQX 4.2 and 5N96B.

We implemented "K70 DDR2 read failure with increasing temperature - NXP Community

K70 DDR2 temperature affect read data - NXP Community", and it seems the device is not sensitive to temperature anymore.

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @dodocolby ,

ddr->CR21 = 0x00040232 instead of 60232. I just wanted to confirm that point, as I don’t have access to the MQX code on my side, it’s no longer supported. In addition, I’ve already reached out to the internal team to help address your question further. I’ll let you know as soon as I hear back from them. Thanks for your understanding.- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @dodocolby ,

Sorry for the long wait. I haven’t received any updates from our internal team yet, likely due to the Christmas holidays.

Please note that our response time may be longer than usual because of the holiday periods across the EMEA and AMEC time zones. I will also be on leave starting tomorrow until January 5th.

If this matter is urgent, you may consider creating a new case and mentioning this link. Other colleagues will be able to locate my internal contact through this case, and there’s a chance you might receive an update before January 5th.

If it’s not urgent, I will continue to follow up once I return. We truly appreciate your understanding and patience.

Have a pleasant day!

BR

Celeste

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @dodocolby ,

Thanks for using our community. I have noticed your question. I need some time to research before getting back to you. If there are any updates during this period, please feel free to share them anytime.

BR

Celeste