- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Changing CPU Speed While Keeping Bus & Peripheral Speed Constant

Changing CPU Speed While Keeping Bus & Peripheral Speed Constant

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Changing CPU Speed While Keeping Bus & Peripheral Speed Constant

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I think I know the answer but I want to ask just to make sure.

I have a KL15 MCU where I run the CPU and bus as 5.99 MHz, and the I2C at 200 KHz. Sometimes I require to speed up the CPU to 48 MHz, but keep the bus and I2C exactly the same. But during this change when going from 5.99MHz to 48 MHz, the FFL multiplier bumps up from 732x to1464x.

My question is...

Is it possible to change CPU speeds in the middle of I2C operations? I am not sure how good the clock gating is on these chips. Since the MCG clocks are 3 orders of magnitudes over the I2C clock, I was thinking it may be possible to do so.

If not, can we do it if the FFL,multiplier stays the same, and the speed is changes at the core clock prescalar?

Thanks,

-Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Peter twiss,

We don't recommend you change the clock mode when do I2C communication.

If you want to change the CPU speed or the clock mode, please disable the I2C communication at first, after the core clock is stable, then enable the I2C module and configure the baud rate again.

FLL will multiple the source frequent, and the core clock prescaler just cut down the frequent, if you want to use the prescaler, you need to have a large core frequent at first.

Now you just have 5.99Mhz bus clock, you can't use the prescaler get the 48Mhz, you must change the clock mode or the FLL multiplier at first.

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Jingjing,

How do you know when the clock is stable? I have not found a flag anywhere in the exported PE code that tells me when the close is stable again? this is the real problem we have run into so often.

Please point to a PE reference where this is located.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi peter twiss,

If you are using the PE code, you'd better mention it in the Floor 1.

The clock stable means you finish the clock module switching.

Which clock source you are using now? external crystal or the internal osc? What the clock mode you are using when you get 5.99Mhz? FEI? And switch to which clock mode to get the 48Mhz core?PEE?

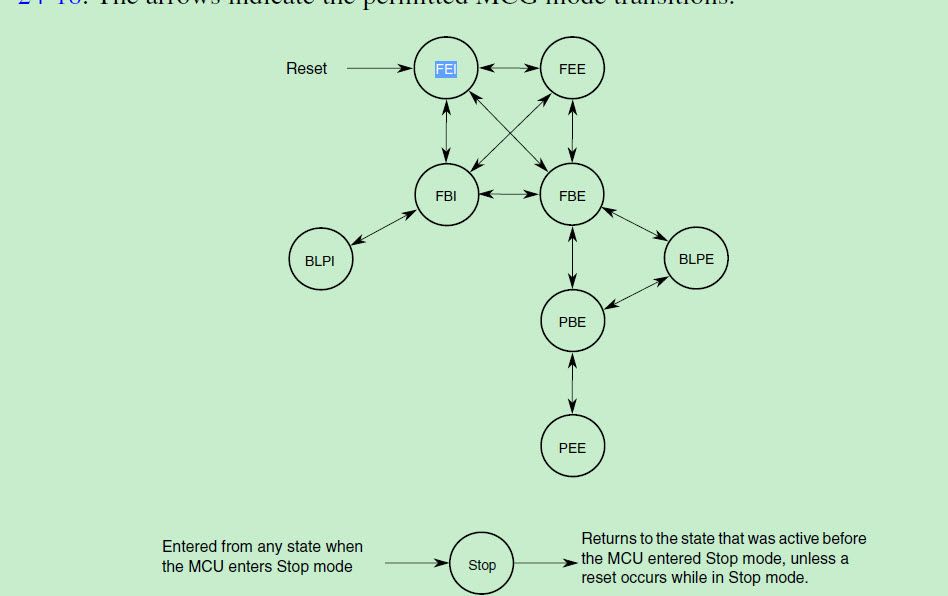

When do the MCG mode swithing ,you need to follow this diagram:

As you know, the source clock of I2C module is from system clock or the bus clock, if the system clock or bus clock is changed, the I2C baud must be changed.Then you'd better disable the I2C module when you want to change the MCG mode, after you finish the MCG mode changing ,then reconfigure your I2C mode again and enable it.

About the clock mode changing PE code, please find it from the attached code:cpu.zip

Wish it helps you!

If you still have question, please contact with me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------