- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- AN4503: Do I really need to enable a falling edge interrupt?

AN4503: Do I really need to enable a falling edge interrupt?

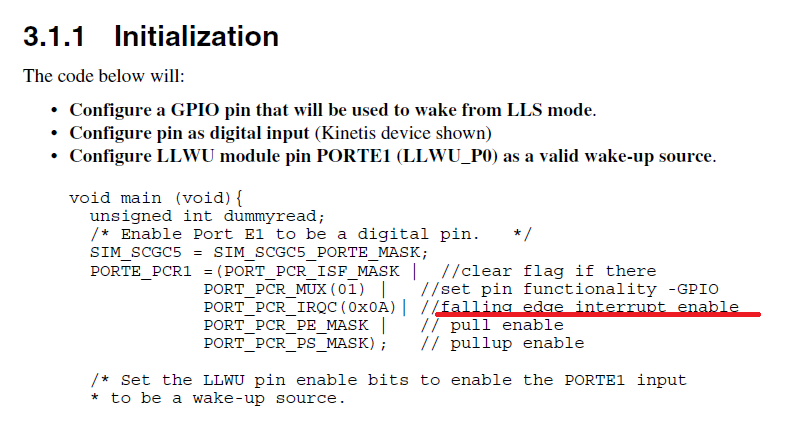

In the AN4503 they activate a falling edge interrupt on the E1 pin. Do I really need to do that to be able to wake up on a falling edge on that pin?

It is not enough to do the following:

LLWU_PE1 = LLWU_PE1_WUPE0(2); //falling edge detection

已解决! 转到解答。

Yes it works without the interrupt enabled :-)

But first it didn't wake up as expected, it got stuck. But then I found information on this forum that the ACKISO bit must be cleared before configuring the oscillators. This information should be better explained in some manual I think.

Yes it works without the interrupt enabled :-)

But first it didn't wake up as expected, it got stuck. But then I found information on this forum that the ACKISO bit must be cleared before configuring the oscillators. This information should be better explained in some manual I think.

Hello again,

I'm glad it is working. Sorry about the ACKISO issue.

So there really two different hold types 1) I/O hold that happens in STOP, VLPS, and LLS that release automatically and 2) I/O and OSC hold that only is released with the write to ACKISO.

Say you have the Oscillator and GPIO set up before going inteo VLLS1. Some of the GPIO are outputs driving low and the OSC is enabled to be running in the low power mode. After the wakeup event the MCU exits the low power mode through the reset flow if waking from VLLSx low power modes. The set up for the OSC and GPIO are lost with the reset, but until you write the ACKISO bit, the pins are held in state and the oscillator will continue to oscillate. The output will continue to be same output state at the pin while you are in the low power mode. Upon wakeup, in order not to glitch you I/O and stop your OSC for the short time between the ACKISO and re-initializing the I/O and OSC it is recommended to complete the I/O and module initialization and re-write the OSC registers in either the OSC block or MCG prior to writing the ACKISO bit. For the output driving low, you would re-run the setup code that initialized the GPIO, initialize the UART or timer output, or other peripherals that can control or be sensitive to pins prior to the write to ACKISO.

By the way, ACKISO, or the hold of pin state, is a feature that has been available for many years on Freescale MCU's including the S08 and CFV1 devices.

Best Regards,

Hello Mark,

If you are going into a low power mode like LLS or VLLS0,1,2,3 then you absolutely do not need the Port interrupt enabled to have the pin be an LLWU wakeup. If you did, however, the act of clearing the LLWU flag in the LLWU interrupt routine clears the port ICF flag. Plus if you enabled the interrupt and you were going into VLPS, STOP, VLPR or WAIT the port interrupt would be available to do something differently than the wakeup from LLS.

The only requiremnt for the LLWU wakeup event to occur is for the pin to be muxed as a digital pin as indicated in Wake-up sources in section 3 of the RM

"LLWU_P0-15 are external pin inputs. Any digital function multiplexed on the pin

can be selected as the wakeup source. See the chip's signal multiplexing table for the

digital signal options."

I hope this helps

Philip