- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- Occur Default handler when start Init Uart

Occur Default handler when start Init Uart

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Occur Default handler when start Init Uart

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

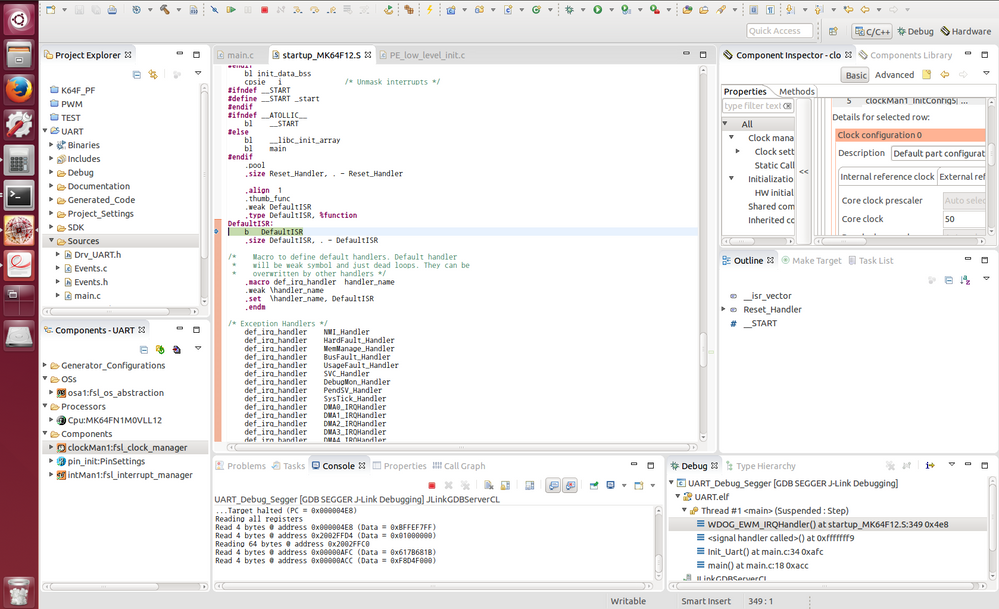

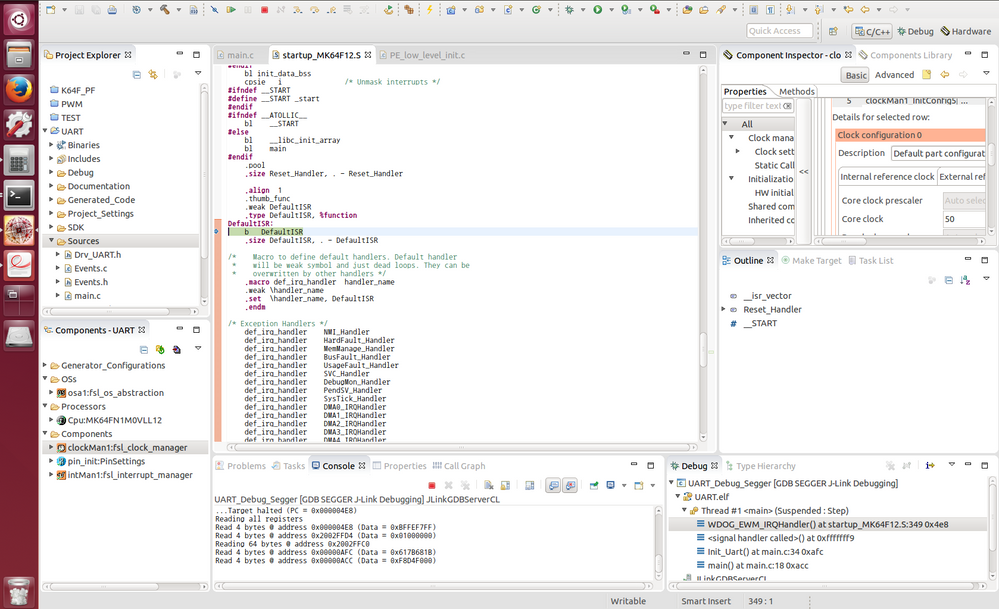

hi, guys. I'm begginer in freescale.

actually, I didn't even know that what the problem is in this code.

I think that is default handler.

when I was coding for uart driver I got a problem about default handler.

Maybe I know that picture of bottom is occured exception and next bottom is main code.

I already got many solutions for this issue on this community. but, I couldn't do that

I guess that issue is related Clock Gating.. whatever

this board is FRDM-K64F

nobody know that issue... TT so, if anybody know that problem.... help me...

thank you.

Noah.

------------------------------------------------------------------------------------------------------------------------------------------------

#include "Cpu.h"

#include "Events.h"

#include "clockMan1.h"

#include "pin_init.h"

#include "osa1.h"

#include "Drv_UART.h"

#if CPU_INIT_CONFIG

#include "Init_Config.h"

#endif

#define REG_RW(x) (volatile uint32_t *)(x)

int main(void)

{

PE_low_level_init();

Init_Uart(4,50000000,115200);

#ifdef PEX_RTOS_START

PEX_RTOS_START();

#endif

for(;;){}

}

void Init_Uart(char ch ,int SysClk, int Baud)

{

int mReg,ubd;

*REG_RW(SIM_SCGC1) |= 0x1 << 10; // Enable the clock to the selected UART

mReg = *REG_RW(UART4_C2); // Tx, Rx are disabled

mReg = (mReg & ~(0x1 << 2)) | (0x0 << 2);

mReg = (mReg & ~(0x1 << 3)) | (0x0 << 3);

*REG_RW(UART4_C2) = mReg;

*REG_RW(UART4_C1) = 0; // all default settings

ubd = (uint32_t)((SysClk)/(Baud*16)); // Calculate Baud Settings

mReg = *REG_RW(UART4_BDH);

*REG_RW(UART4_BDH) = (mReg & ~(0x1F << 0)) | (ubd >> 8); // BDH

*REG_RW(UART4_BDL) = (uint8_t)(ubd & 0xff); // BDL

mReg = *REG_RW(UART4_C4); // BRFA

mReg = (mReg & ~(0x1F << 0)) | (0x1 << 2);

*REG_RW(UART4_C4) = mReg;

mReg = *REG_RW(UART4_C2); // Tx, Rx are enabled

mReg = (mReg & ~(0x1 << 2)) | (0x1 << 2);

mReg = (mReg & ~(0x1 << 3)) | (0x1 << 3);

*REG_RW(UART4_C2) = mReg;

mReg = *REG_RW(UART4_S2); // Most Significant Bit First

mReg = (mReg & ~(0x1 << 5)) | (0x0 << 0);

*REG_RW(UART4_S2) = mReg;

}

------------------------------------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello noah,

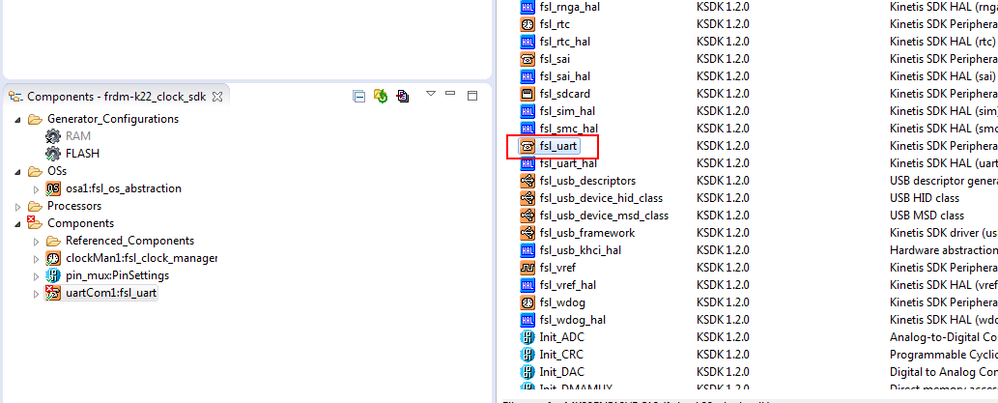

(1) Form your picture , i see you use KDS and KSDK, please tell me the version of KDS and SDK .

(2) IN you code, i see when initialize the UART component , you sue the code by yourself , and in the KSDK driver , there have

UART_DRV_Init , you can directly use , and under the SDK install directory , there are some UART demo , you can refer to :

...Freescale\KSDK_1.2.0\examples\frdmk64f\driver_examples\uart

(3) Also you can use the Processor Expert , directly add UART component , then configure , then it can generate code

(4) If you still want to know why is wrong about your code , please send your project to me , i will test it on my side .

Hope it helps

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------