- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- ColdFire/68K Microcontrollers and Processors

- :

- Where are the IO Models corresponding the Slew Rate Control Register SRCR_x ( MCF5441x)

Where are the IO Models corresponding the Slew Rate Control Register SRCR_x ( MCF5441x)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Where are the IO Models corresponding the Slew Rate Control Register SRCR_x ( MCF5441x)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

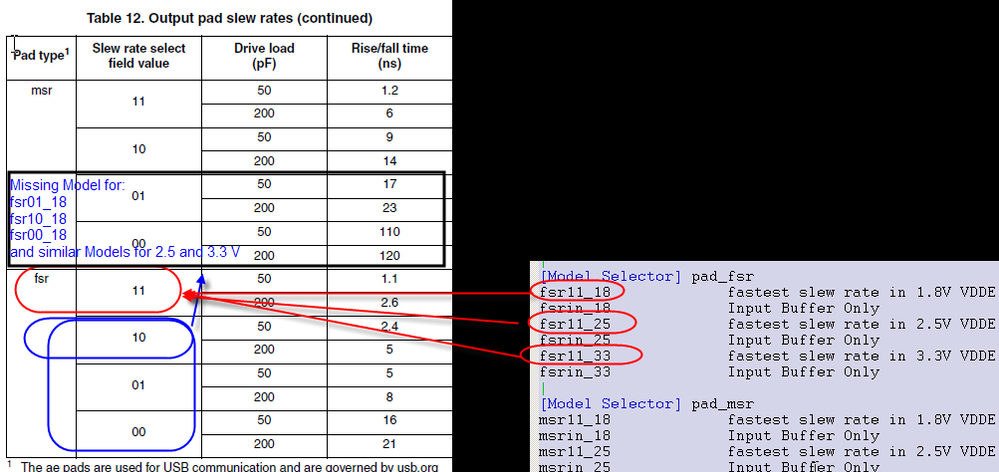

Looking at the SR Control register let's assume, that there were 4 different IBIS IO Models to simulate different slew rates within a given voltage rail lets say 3.3V

In the Ibis Model the Model Selector pad_fsr does only support Models for the voltages 1.8, 2,5 and 3,3V

How can Slew Rate control be established in simulation within the supported IBIS IO's / Model Selectors in the ibis File. Typycally these Models were expected whithin the default Model Selector pad_fsr

I've seen there were pad_msr and pad_ssr Model Selectors available but I haven't found a hint that these can be used for the physical Pin F3 also.

best regard

Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robert asks:

> let's assume, that there were 4 different IBIS IO Models

> In the Ibis Model the Model Selector pad_fsr

So DO you have an IBIS model for that part or not? I don't know what you do or don't have one. Or you're assuming there is one (that you don't have) and then hypothesizing from there. I need more context and background for your question.

I can't find an IBIS model for the MCF5441x. I do have them for the MCF5445x and the MCF5329. If you do have one for your part then please say where you got it and/or provide a link to it. Here's the MCF5445x one:

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=MCF5445X&fpsp=1&tab=Design_Tools_Tab

If the parts are similar enough you might be able to get some hints from the MCF5445x one. Reading the Data Sheets they're quite different (Slew Rate Controls versus Drive Strength Controls, or maybe they're just documented differently).

Freescale have very confusing "Drive Strength" documentation for other chips. I had problems with the MCF5329 Data Sheet:

MCF5329 with random SDRAM 1k "bit rot" corruptions

MCF5329 MSCR_FLEXBUS and MSCR_SDRAM Registers, how do they work in SDR mode?

You're lucky you're not using the MCF5301x chips. They DEFAULT to a "Drive Strength" that is documented in the Reference Manual as being RESERVED. I managed to work out what this means by doing some Archaeology on other Data Sheets. In order to understand the MCF5301X Drive Strength, read the MPC56XX manual. Gory details here:

Re: MCF5301X Drive strength settings

You may find the MCF5441X I/O better documented in the MPC (or other chip) manual the I/O circuitry was lifted from.

Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the info,

we have got the model under an NDA, so I could not share it.

As you can see there were also:

ssr ( Slow Slew Rate )

msr ( Middle Slew Rate )

fsr ( Fast Slew Rate)

Models for the 1.8, 2,5 and 3.3 Voltages.

Within the Flexbus Slew Rate Control Registers (SRCR_FB4) there are the folling four combinatination available:

SRE_x Slew rate control.

00 Lowest slew rate

01 Low slew rate

10 High slew rate

11 Highest slew rate

I missed the IBIS Models for the three patten (10,01,00) in the Slewrate Control Register.

regards

Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The device you cite is not a digital signal controller; please also enter your question in another MCU group to increase exposure.

Best Regards,

John L. Winters

Senior Applications Engineer

AMR/EU MCU & MPU AE Group

Freescale Inc.

2100 Elliot Road

This email and any associated attachments have been classified as:

Freescale Confidential and Proprietary