- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: LVDS0 in U-Boot 2015.04 at imx6qSabreSD-based board.

LVDS0 in U-Boot 2015.04 at imx6qSabreSD-based board.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all!

I am trying to display SplashScreen logo at LVDS display in U-Boot. My mx6sabre_common.h configs is next:

/* Framebuffer */

#define CONFIG_VIDEO

#define CONFIG_VIDEO_IPUV3

#define CONFIG_CFB_CONSOLE

#define CONFIG_VGA_AS_SINGLE_DEVICE

#define CONFIG_SYS_CONSOLE_IS_IN_ENV

#define CONFIG_SYS_CONSOLE_OVERWRITE_ROUTINE

#define CONFIG_VIDEO_BMP_RLE8

#define CONFIG_SPLASH_SCREEN

#define CONFIG_SPLASH_SCREEN_ALIGN

#define CONFIG_BMP_16BPP

#define CONFIG_VIDEO_LOGO

#define CONFIG_VIDEO_BMP_LOGO

#define CONFIG_IPUV3_CLK 260000000

#define CONFIG_IMX_HDMI

#define CONFIG_IMX_VIDEO_SKIP

Now I can see crystal clear logo at the HDMI channel, but when I unplug HDMI and plug LVDS and reboot board I see my logo badly corrupted.

My LVDS display is interfaced over LVDS0 0-3 data lanes

LVDS0_TX0_N

LVDS0_TX0_P

LVDS0_TX1_N

LVDS0_TX1_P

LVDS0_TX2_N

LVDS0_TX2_P

LVDS0_TX3_N

LVDS0_TX3_P

Here are my LVDS-related code snippets:

static void enable_lvds(struct display_info_t const *dev)

{

struct iomuxc *iomux = (struct iomuxc *)

IOMUXC_BASE_ADDR;

u32 reg = readl(&iomux->gpr[2]);

reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT |

IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT;

writel(reg, &iomux->gpr[2]);

}

struct display_info_t const displays[] = {{

.bus = -1,

.addr = 0,

.pixfmt = IPU_PIX_FMT_RGB666,

.detect = NULL,

.enable = enable_lvds,

.mode = {

.name = "Hannstar-XGA",

.refresh = 60,

.xres = 1024,

.yres = 768,

.pixclock = 15385,

.left_margin = 220,

.right_margin = 40,

.upper_margin = 21,

.lower_margin = 7,

.hsync_len = 60,

.vsync_len = 10,

.sync = FB_SYNC_EXT,

.vmode = FB_VMODE_NONINTERLACED

} }, {

.bus = -1,

.addr = 0,

.pixfmt = IPU_PIX_FMT_RGB24,

.detect = detect_hdmi,

.enable = do_enable_hdmi,

.mode = {

.name = "HDMI",

.refresh = 60,

.xres = 1024,

.yres = 768,

.pixclock = 15385,

.left_margin = 220,

.right_margin = 40,

.upper_margin = 21,

.lower_margin = 7,

.hsync_len = 60,

.vsync_len = 10,

.sync = FB_SYNC_EXT,

.vmode = FB_VMODE_NONINTERLACED

} }};

static void setup_display(void)

{

struct mxc_ccm_reg *mxc_ccm = (struct mxc_ccm_reg *)CCM_BASE_ADDR;

struct iomuxc *iomux = (struct iomuxc *)IOMUXC_BASE_ADDR;

int reg;

/* Setup HSYNC, VSYNC, DISP_CLK for debugging purposes */

imx_iomux_v3_setup_multiple_pads(di0_pads, ARRAY_SIZE(di0_pads));

enable_ipu_clock();

imx_setup_hdmi();

/* Turn on LDB0, LDB1, IPU,IPU DI0 clocks */

reg = readl(&mxc_ccm->CCGR3);

reg |= MXC_CCM_CCGR3_LDB_DI0_MASK | MXC_CCM_CCGR3_LDB_DI1_MASK;

writel(reg, &mxc_ccm->CCGR3);

/* set LDB0, LDB1 clk select to 011/011 */

reg = readl(&mxc_ccm->cs2cdr);

reg &= ~(MXC_CCM_CS2CDR_LDB_DI0_CLK_SEL_MASK

| MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_MASK);

reg |= (3 << MXC_CCM_CS2CDR_LDB_DI0_CLK_SEL_OFFSET)

| (3 << MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_OFFSET);

writel(reg, &mxc_ccm->cs2cdr);

reg = readl(&mxc_ccm->cscmr2);

reg |= MXC_CCM_CSCMR2_LDB_DI0_IPU_DIV | MXC_CCM_CSCMR2_LDB_DI1_IPU_DIV;

writel(reg, &mxc_ccm->cscmr2);

reg = readl(&mxc_ccm->chsccdr);

reg |= (CHSCCDR_CLK_SEL_LDB_DI0

<< MXC_CCM_CHSCCDR_IPU1_DI0_CLK_SEL_OFFSET);

reg |= (CHSCCDR_CLK_SEL_LDB_DI0

<< MXC_CCM_CHSCCDR_IPU1_DI1_CLK_SEL_OFFSET);

writel(reg, &mxc_ccm->chsccdr);

reg = IOMUXC_GPR2_BGREF_RRMODE_EXTERNAL_RES

| IOMUXC_GPR2_DI1_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_DI0_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_BIT_MAPPING_CH1_SPWG

| IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT

| IOMUXC_GPR2_BIT_MAPPING_CH0_SPWG

| IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT

| IOMUXC_GPR2_LVDS_CH0_MODE_ENABLED_DI0

| IOMUXC_GPR2_LVDS_CH1_MODE_DISABLED;

writel(reg, &iomux->gpr[2]);

reg = readl(&iomux->gpr[3]);

reg = (reg & ~(IOMUXC_GPR3_LVDS0_MUX_CTL_MASK

| IOMUXC_GPR3_HDMI_MUX_CTL_MASK))

| (IOMUXC_GPR3_MUX_SRC_IPU1_DI0

<< IOMUXC_GPR3_LVDS0_MUX_CTL_OFFSET);

writel(reg, &iomux->gpr[3]);

}

And another question: Is it possible to simultaneously display HDMI and LVDS0 at U-Boot?

I have not found answers to their questions on the forum.

Hope for your help!

Regards,

Ivan.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Just to clarify, you are trying that the logo shows up in either HDMI monitor or LVDS display depending on which one is detected?

Or you just want to display the logo in both screens? This is of course possible in HW but I have to skim through the u-boot code to try to add this feature.

Please provide more details about what you have tried in the code, I would be glad to help.

Best Regards,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Alejandro.

Thank you for your responce.

I want to display my logo in both screens at the same time. Problem is that I can't get LVDS0 working. I started to change mx6sabresd.c source file. I realized that in order for the screen displayed something I need set DATA_WIDTH to 24BIT. There are two possible ways: SPWG and JEIDA.

For SPWG:

diff --git a/board/freescale/mx6sabresd/mx6sabresd.c b/board/freescale/mx6sabresd/mx6sabresd.c

index 4198f61..b9804ef 100644

--- a/board/freescale/mx6sabresd/mx6sabresd.c

+++ b/board/freescale/mx6sabresd/mx6sabresd.c

static iomux_v3_cfg_t const usdhc4_pads[] = {

@@ -438,9 +438,10 @@ static void enable_lvds(struct display_info_t const *dev)

struct iomuxc *iomux = (struct iomuxc *)

IOMUXC_BASE_ADDR;

u32 reg = readl(&iomux->gpr[2]);

- reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT |

- IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT;

+ reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT |

+ IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT;

writel(reg, &iomux->gpr[2]);

+ //gpio_direction_output(DISP0_PWR_EN, 1);

}

struct display_info_t const displays[] = {{

@@ -546,18 +547,18 @@ static void setup_display(void)

| IOMUXC_GPR2_DI1_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_DI0_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_BIT_MAPPING_CH1_SPWG

- | IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT

+ | IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT

| IOMUXC_GPR2_BIT_MAPPING_CH0_SPWG

- | IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT

- | IOMUXC_GPR2_LVDS_CH0_MODE_DISABLED

- | IOMUXC_GPR2_LVDS_CH1_MODE_ENABLED_DI0;

+ | IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT

+ | IOMUXC_GPR2_LVDS_CH0_MODE_ENABLED_DI0

+ | IOMUXC_GPR2_LVDS_CH1_MODE_DISABLED;

writel(reg, &iomux->gpr[2]);

reg = readl(&iomux->gpr[3]);

- reg = (reg & ~(IOMUXC_GPR3_LVDS1_MUX_CTL_MASK

+ reg = (reg & ~(IOMUXC_GPR3_LVDS0_MUX_CTL_MASK

| IOMUXC_GPR3_HDMI_MUX_CTL_MASK))

| (IOMUXC_GPR3_MUX_SRC_IPU1_DI0

- << IOMUXC_GPR3_LVDS1_MUX_CTL_OFFSET);

+ << IOMUXC_GPR3_LVDS0_MUX_CTL_OFFSET);

writel(reg, &iomux->gpr[3]);

}

#endif /* CONFIG_VIDEO_IPUV3 */

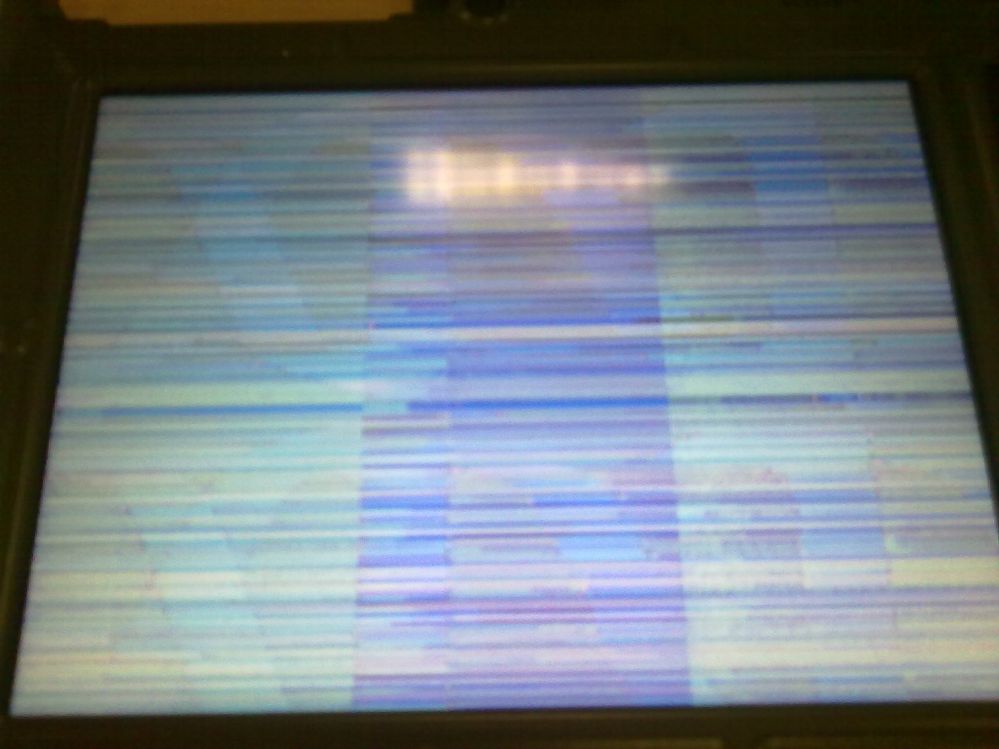

I got this:

For JEIDA:

diff --git a/board/freescale/mx6sabresd/mx6sabresd.c b/board/freescale/mx6sabresd/mx6sabresd.c

index 4198f61..ea618aa 100644

--- a/board/freescale/mx6sabresd/mx6sabresd.c

+++ b/board/freescale/mx6sabresd/mx6sabresd.c

static iomux_v3_cfg_t const usdhc4_pads[] = {

@@ -438,9 +438,10 @@ static void enable_lvds(struct display_info_t const *dev)

struct iomuxc *iomux = (struct iomuxc *)

IOMUXC_BASE_ADDR;

u32 reg = readl(&iomux->gpr[2]);

- reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT |

- IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT;

+ reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT |

+ IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT;

writel(reg, &iomux->gpr[2]);

+ //gpio_direction_output(DISP0_PWR_EN, 1);

}

struct display_info_t const displays[] = {{

@@ -546,18 +547,18 @@ static void setup_display(void)

| IOMUXC_GPR2_DI1_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_DI0_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_BIT_MAPPING_CH1_SPWG

- | IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT

- | IOMUXC_GPR2_BIT_MAPPING_CH0_SPWG

- | IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT

- | IOMUXC_GPR2_LVDS_CH0_MODE_DISABLED

- | IOMUXC_GPR2_LVDS_CH1_MODE_ENABLED_DI0;

+ | IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT

+ | IOMUXC_GPR2_BIT_MAPPING_CH0_JEIDA

+ | IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT

+ | IOMUXC_GPR2_LVDS_CH0_MODE_ENABLED_DI0

+ | IOMUXC_GPR2_LVDS_CH1_MODE_DISABLED;

writel(reg, &iomux->gpr[2]);

reg = readl(&iomux->gpr[3]);

- reg = (reg & ~(IOMUXC_GPR3_LVDS1_MUX_CTL_MASK

+ reg = (reg & ~(IOMUXC_GPR3_LVDS0_MUX_CTL_MASK

| IOMUXC_GPR3_HDMI_MUX_CTL_MASK))

| (IOMUXC_GPR3_MUX_SRC_IPU1_DI0

- << IOMUXC_GPR3_LVDS1_MUX_CTL_OFFSET);

+ << IOMUXC_GPR3_LVDS0_MUX_CTL_OFFSET);

writel(reg, &iomux->gpr[3]);

}

#endif /* CONFIG_VIDEO_IPUV3 */

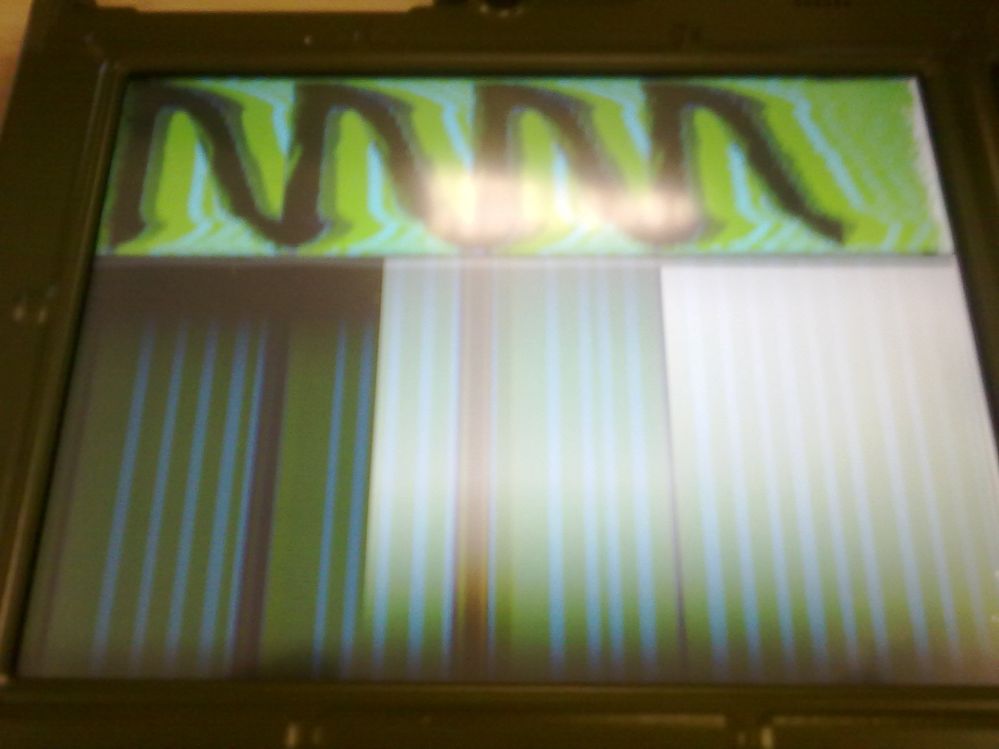

I got this:

Original image at the HDMI (from U-Boot):

That is all that I tried to change.

Please help me to understand what is the problem.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Have you checked that the frequency for the lvds panel is the correct one?

/Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Alejandro!

We started to check the frequency as you advised and found that we have a LVDS_TX3 pair instead of a LVDS_CLK pair :smileyconfused:.

We rerouted this wires and LVDS started work perfectly!

Thank you!