- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Model-Based Design Toolbox (MBDT)

- :

- Model-Based Design Toolbox (MBDT)

- :

- Having trouble with ADC clock configuration

Having trouble with ADC clock configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Having trouble with ADC clock configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using FreeMASTER, I'm able to get around 1.1ms reads from my ADC. I would like to be reading .1ms or even .01ms but I'm not having any luck. I'm pretty sure it's an issue with my model and not a FreeMASTER limitation because I've seen other forum posts that look like faster reads are happening.

For reference:

I started with the adc_pdb_trigger_s32k14x example model

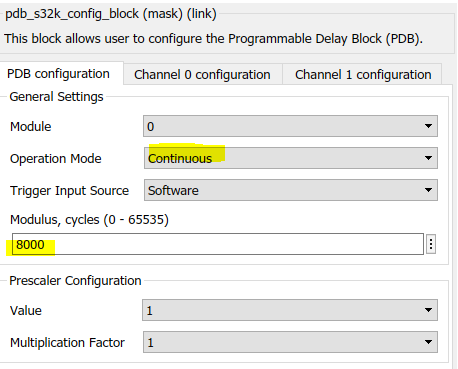

I'm running a fixed step size of .0001 at 80MHz system clock using the S32K144EVB. I'm using prescaler value of 2 in the PDB_Config block so (I believe) I'm operating the ADC clock at 40MHz.

It should be noted that using fixed step size of .001 and .0001 makes no discernible difference to my ADC read. Changing from .001 to .01 changed my ADC read from 1ms to 10ms, as expected.

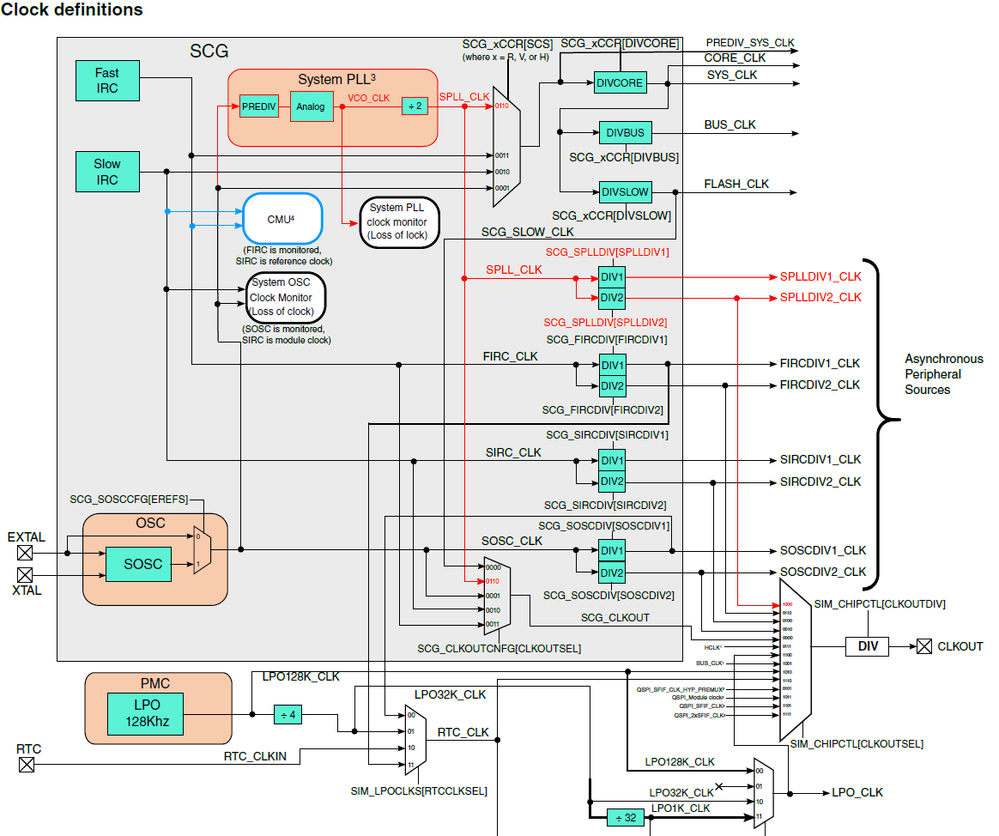

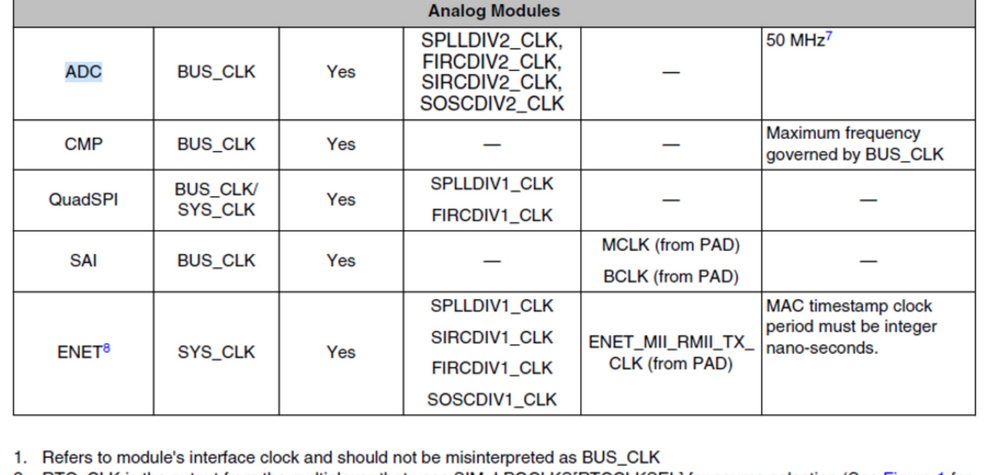

I'm struggling with clocking though so I'm pretty sure that's where the problem is. According to the data sheet, fadck has a max of 50MHz to operate reliably. I assume this means I need to scale the 80MHz down to 40MHz but is the PDB_Config the correct place? According to the help documentation, this prescaler is dividing the peripheral clock (BUS_CLK), not the system clock. I don't know where else I can divide the system clock. I'm having trouble following the clocking diagram in the ref manual but it looks like I would divide the system clock in the DIVBUS block. Not sure how to do that with the Simulink Toolbox. The only place I see for clock division is PDB_Config.

I'm seeing ADC using the BUS_CLK as peripheral clock but Note1 below says not to misinterpret the interface clock as BUS_CLK. I have no idea what that means:

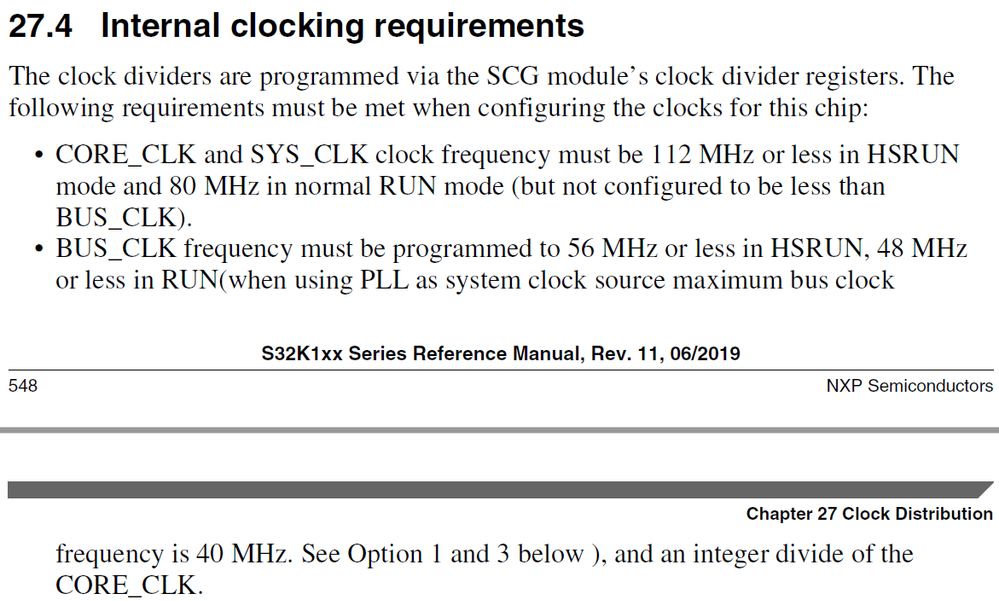

When I look at this section of ref manual, I'm further confused. My only two options for clock speed are 112 and 80. Those are both acceptable for HSRUN but only 80 is acceptable for RUN. Does this mean I'm always using HSRUN or am I switching between HSRUN and RUN by switching from 112 to 80? How does this affect SYS_CLK/BUS_CLK?

I've read through multiple forum posts and a large amount of documentation and I don't feel anything about ADC clocking is obvious with the Toolbox but other people seem to be successful with it so I'm either missing something or I'm just not as smart as I think I am! Using this post I was able to understand how and why the PDB works but it's not mentioned how he got his 8000 modulus. I assume he got it by dividing his step size of .0001 by the period of 80MHz (125n). That gives 8000. Not sure why he's using 80MHz though. At any rate, I've tried to replicate his .0001 readings using his settings and I'm unable to do it. No matter what I change, I always get around 1.1ms updates. I'm attaching my model. Any help would be appreciated.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sparkee,

Since my colleague constantinrazvan.chivu, has provided you a detailed explanation regarding the PIT peripheral clock and its capabilities on LPIT Timing and Step Tick Accuracy of S32K144?, I am going to explain a bit why you see no notable changes from a certain timing.

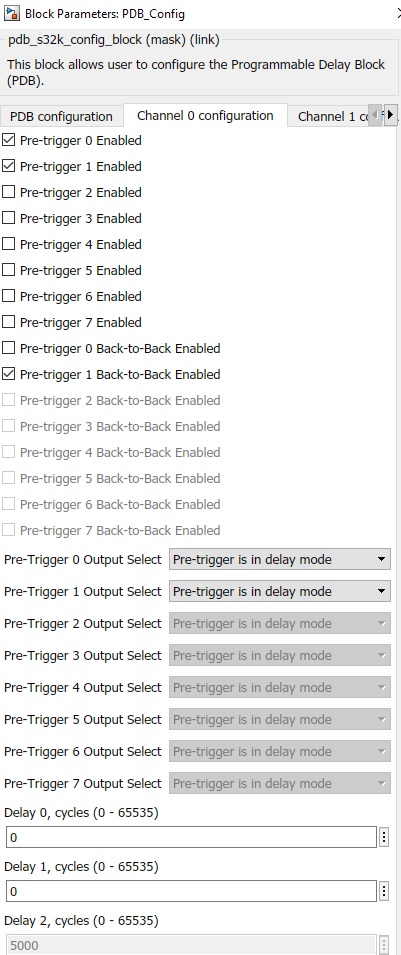

The PDB settings from that model you attached are the following:

1. Operating Mode - Continuous --- this means that once you software triggered this block using the PDB_Start_Soft_Trigger, the PDB will automatically retrigger the signals. So the One-Shot method is more suitable for testing. This means that for the each call of the PDB_Start_Stop_Trigger block, the PDB will perform only one set of triggers. To trigger again, the Start_Stop has to be called again. If you move this block to the step function call, basically each PIT step will provide a start trigger for PDB.

The Modulus represents the top value for the PDB Counter. So once the trigger came, the PDB will count until this value and reset. For this testing purposes, the value must be as low as possible.

In the next tab, the Delay 0 is used like this: once the PDB timer starts to count, when it will match this value, it will trigger the ADC conversion.

So basically, this model is only starting the continuous PDB conversion once and then will perform the conversions at constant time intervals.

Now, what I did in the attached model, I put the start conversion PDB_Start_Soft_Trigger on the step, so basically every PIT0 will start a conversion. I minimized the PDB Modulus and triggers to 0 and basically for every step, the PDB will trigger another conversion.

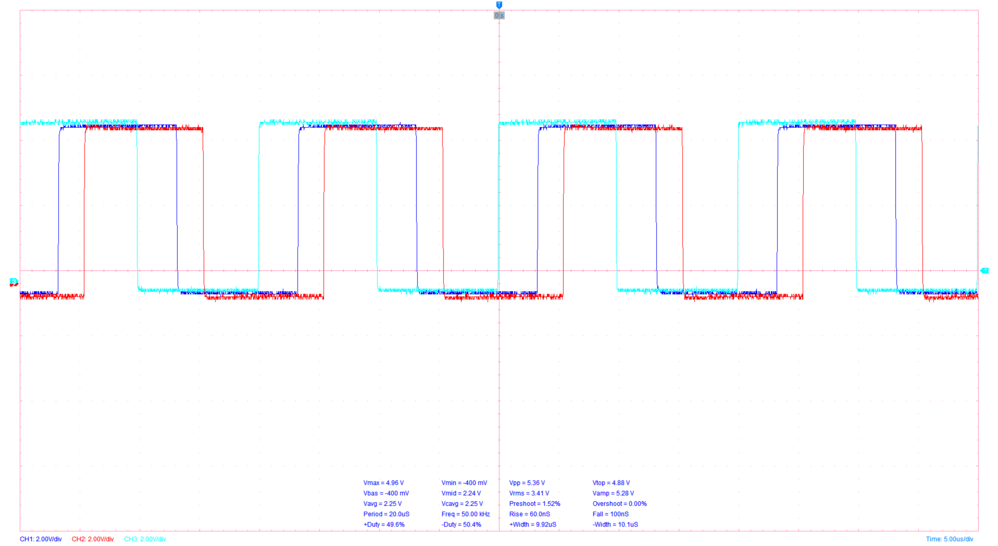

Now, I was able to low the Step Size to the value of 0.00001s. The first signal represents the step trigger, the second one, represents when the model entered the PDB trigger function while the red signals represents when the mcu exited the PDB interrupt function.

Since every step time we toggle the pin, the actual frequency is double than the one computed by the scope.

Hope this helps,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My apologies but I'm no longer getting any ADC read at all using your model and monitoring with FreeMASTER. The GPO Write at PTD7 is working though.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sparkee,

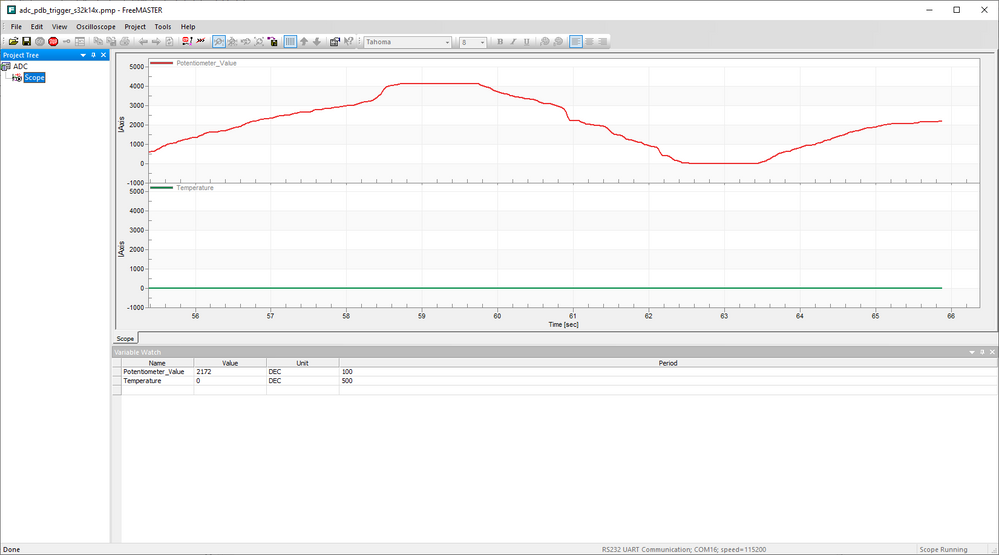

The model I've sent you, disables the second channel trigger in order to convert faster, but on my board, the potentiometer value is still converted fine. This is the FreeMaster screenshot.

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You're right Marius, I was looking at the ADC that you had disabled. I'm an idiot.

It took some time but I have figured out the proper configuration for back-to-back operation so that both ADCs will read in one-shot mode. I had pre-trigger0 in back-to-back mode which means there was never a first ADC read to kick off the sequence. I unchecked the box and it now starts when PDB triggers then pre-trigger1 fires as soon as that read is finished.

I still have a problem with the ADC read speed. I can see that the LED is switching at the step_tick timing as expected (on my scope) but the ADC is not matching that speed. I'm still seeing no faster than 1ms updates on ADC in FreeMASTER.

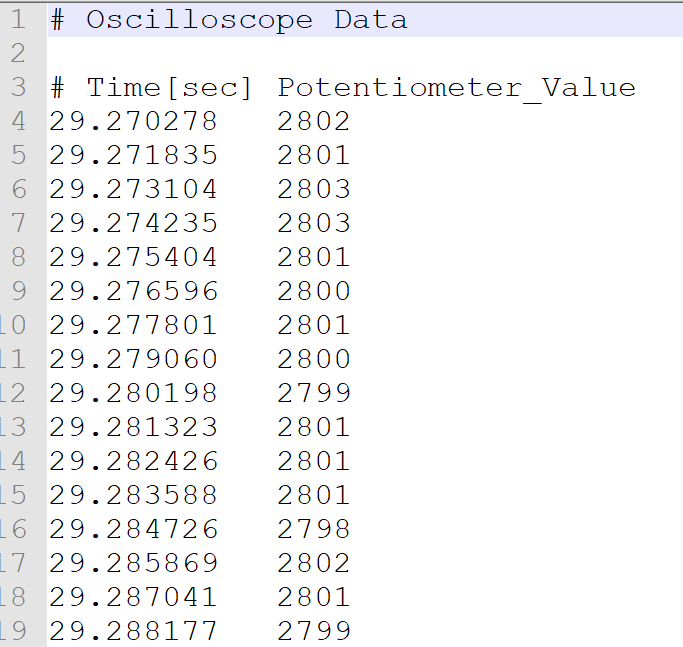

With step_tick at .001:

With step_tick at .0001:

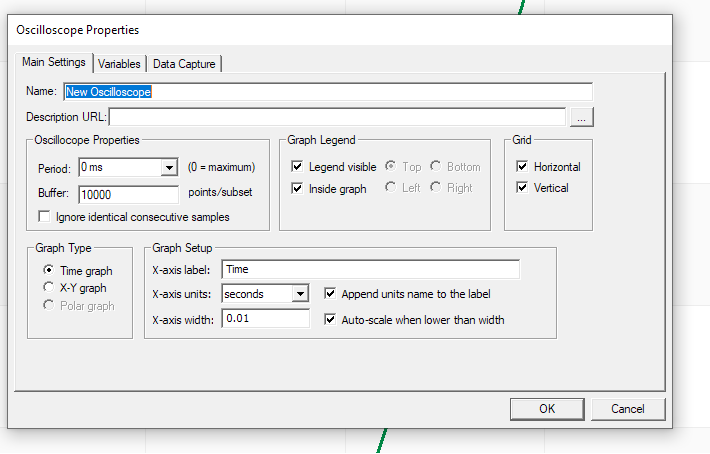

FreeMaster scope properties:

There must be something simple I'm missing or FreeMASTER just isn't capable of anything below 1ms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sparkee,

I am glad that now you can achieve the conversions right.

For the FreeMaster frequency, I think iulianstan can provide you more details.

Hope this helps,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sparkee, Marius,

There no much improvement that can be done when scope period is set to 0ms. The only options is to make sure that there are no other ongoing communication between the target and host PC - ex: make sure there a no variables in the "Variables Watch" widget. You can track all the messages in communication log (Tools→Communication Debug Log...).

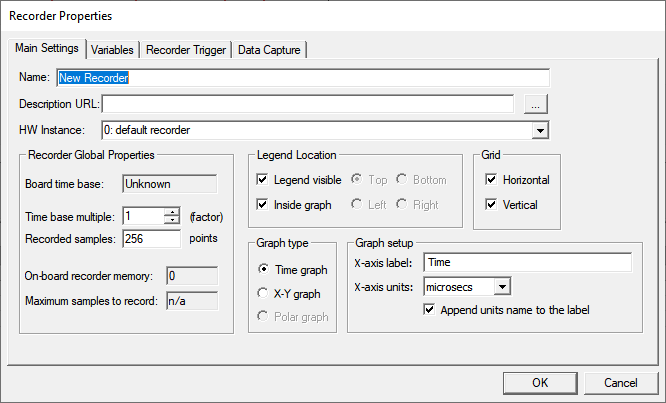

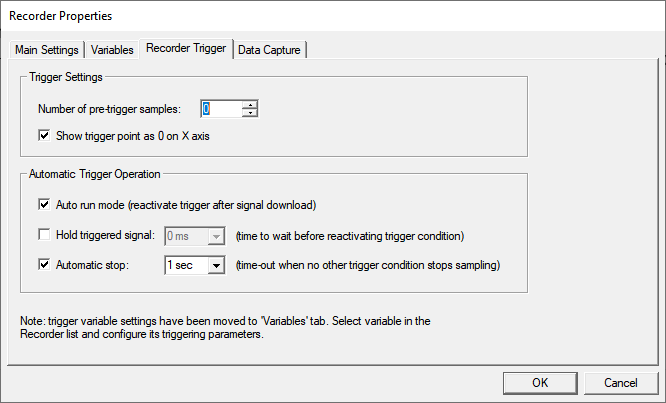

In case you need to capture the data around e specific event (trigger) you could use Recorder functionality (see user guide section 4.1.1.3). You can call the "recorder poll" function in a interrupt routine that will store data in an on-board array at specified frequency. Please note that it unlike the scope it is not meant for continuous data polling - FreeMASTER reads recorded data from the board only when the trigger condition is met or a timeout occurs.

Iulian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply iulianstan. I have attempted what you suggested by removing the variable watch and saw no improvement. I was unable to find the "recorder poll" function but I saw FreeMaster_Poll_Call and FreeMaster_Recorder_Call. I tried them both to limited success. I was able to get a sample on the recorder screen but it did not represent the signal it was reading. Something is breaking when I switch from Scope to Recorder. Scope is showing a square wave like I posted above then switch to recorder and I get a flatline series of samples that reside somewhere between high and low. When I switch back to Scope, the signal is stuck flatlined at max value 4095. I'm able to reset the MCU and the signal returns.

I feel like I'm trying to do something very basic and finding it extremely difficult.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello sparkee,

The Freemaster Recorder Call block that must be added in order to achieve this functionality is this one:

Now, the recorder must also be set int he FreeMaste_Config block.

For the FreeMaster application, The maximum allowed samples point is 256, you will see this error.

But what we believe it happens is that the step time is more faster than this recorder transfer has place. And this might be the reason why you get a constant value.

Hope this helps,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

mariuslucianandrei have you had a chance to look at the errors above?

I'm still unable to read ADC at rates faster than 1ms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes.

I can flip digital outputs at 5 and 10kHz no problem and I see them on the scope but they don't show up well in FreeMaster so I'm assuming my issue is with FreeMaster. Have you witnessed FreeMaster running that gives better than 1ms update time? If so could you send me the Project file so I can check against mine? Is there some other way to check the ADC speed?

My other thought is that it has something to do with the time it takes to write to a data store. Since I'm reading the data store into FreeMaster it's not being updated fast enough. How fast are data stores capable of being written to?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

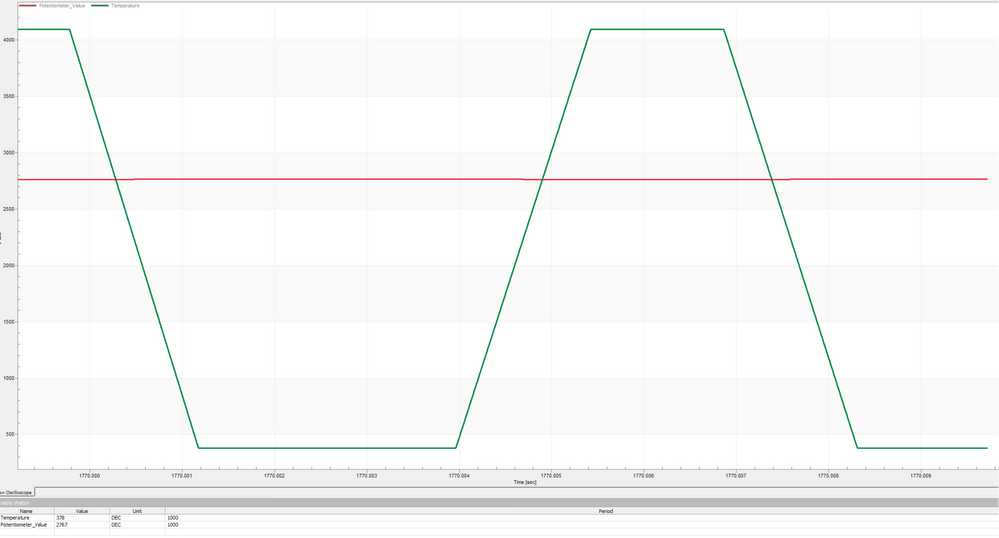

My issue persists. I already had the FreeMaster Recording Call in my model. The square wave being read is at 50kHz.

Note that I said the flatline was between high and low but is actually at 4095. The axis changed so it only looked like a midpoint.

Below is a video showing my issue that I uploaded to iCloud.

EDIT:

I forgot that I went into the debuglog in FreeMaster and saw the following errors. I was unable to locate much info except for it's a "could not open communications port" error.

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=

adOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

App:ReadValue(Temperature)

ReadVar(addr:0x20000598, size:0x0)

ReadVar32(addr:0x20000598) done [OK code=0]

done [OK code=0]

done [OK code=0]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

App:ReadValue(Potentiometer_Value)

ReadVar(addr:0x200005b4, size:0x0)

ReadVar32(addr:0x200005b4) done [OK code=0]

done [OK code=0]

done [OK code=0]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

ReadOscilloscopeDataV4(0)

ReadOscilloscopeDataV4Legacy(0) done [OK code=0]

done [ERROR code=0x80004005]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That makes perfect sense, thank you very much for that explanation. I think I will use the one-shot in my design so that I can control the timing of the ADC reads more precisely.