- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- RT1060 - use of OCRAM breaks fatfs example

RT1060 - use of OCRAM breaks fatfs example

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm working on a FreeRTOS project and plan to use all 1MB of the internal RAM on the RT1060. I've noticed that there is a change in the code behavior based off the location I store the global data.

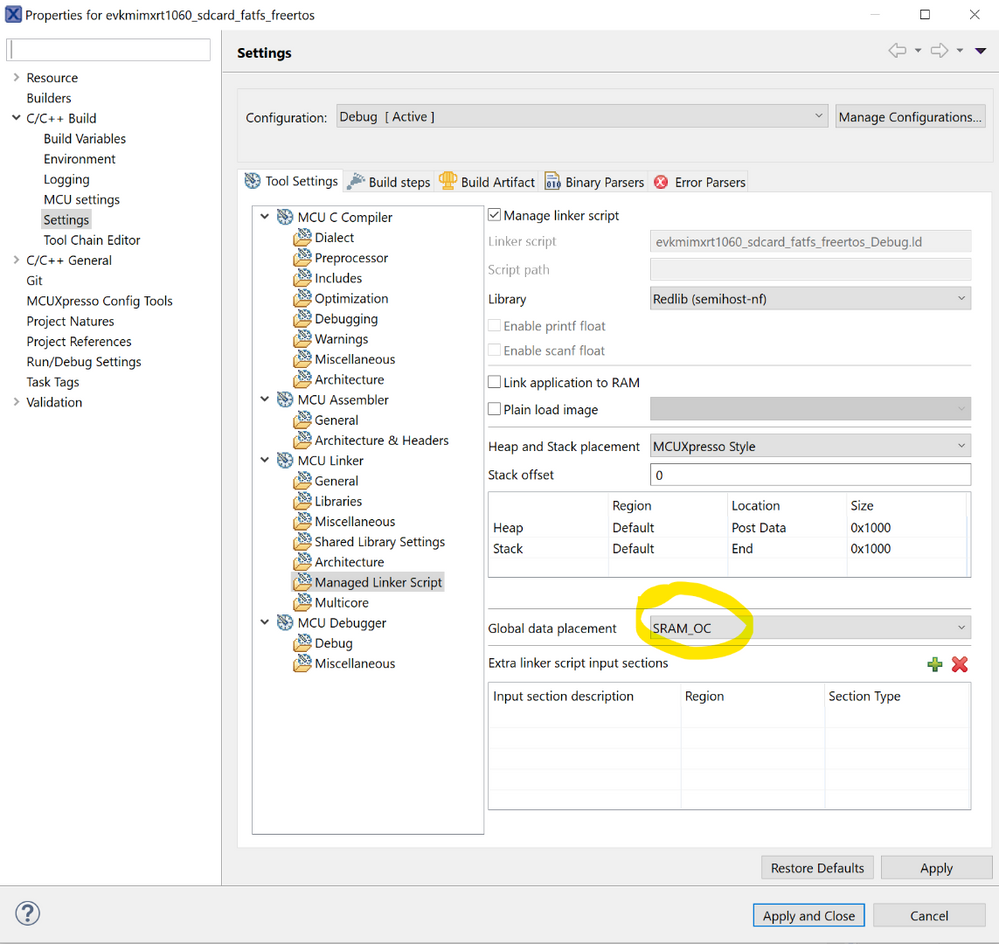

For example, currently I'm working with the RT1060EVK board with a uSD card and FatFS. I import the example project: evkmimxrt1060_sdcard_fatfs_freertos and change only one setting, which breaks the example. Out of the box, it run as expected. After moving the global data into the OCRAM (from DTCM), the application no longer writes to the SD card.

Can anyone explain to me what I'm missing, and why changing this from SRAM_OC to SRAM_DTC fixes some issues in the SD initialization.

FYI: the output from the example when it fails is as follows:

SDCARD fatfs freertos example.

Card inserted.

Make file system......The time may be long if the card capacity is big.

Make file system failed.

The example I am running is from SDK version 2.6.2.

Thanks,

Tim

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tim-san

Did you change MPU setting?

In Default Setting, OCRAM area is set to not shareable by BOARD_ConfigMPU.

So transfer using DMA does not work.

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tim,

This is because OCRAM default is cacheable. Since some SD control block in RAM is shared by SD peripheral and MCU, cache function cause data missing. When MCU write something to the block, it only write to cache actually. Peripheral can get it. When peripheral write something to the block, MCU also don't know. Because it only read from cache actually.

TCM is not cacheable. So, it hasn't this problem. For i.MXRT, shareable means non-cacheable by default. T.Kashiwagi's method can resolve the problem.

Regards,

Jing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Perfect, thanks so much for pointing that out. It all makes sense to me know.

Thanks,

Tim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tim-san

Did you change MPU setting?

In Default Setting, OCRAM area is set to not shareable by BOARD_ConfigMPU.

So transfer using DMA does not work.

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);

Best Regards,

T.Kashiwagi