- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Howto: 20-bit SPI transfer using SSP?

Howto: 20-bit SPI transfer using SSP?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Howto: 20-bit SPI transfer using SSP?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Considering using LPC MCUs for a project.

Need to interface to devices with 20-bit SPI frames, which is very common (for 20-bit ADCs, DACs, etc); for example:

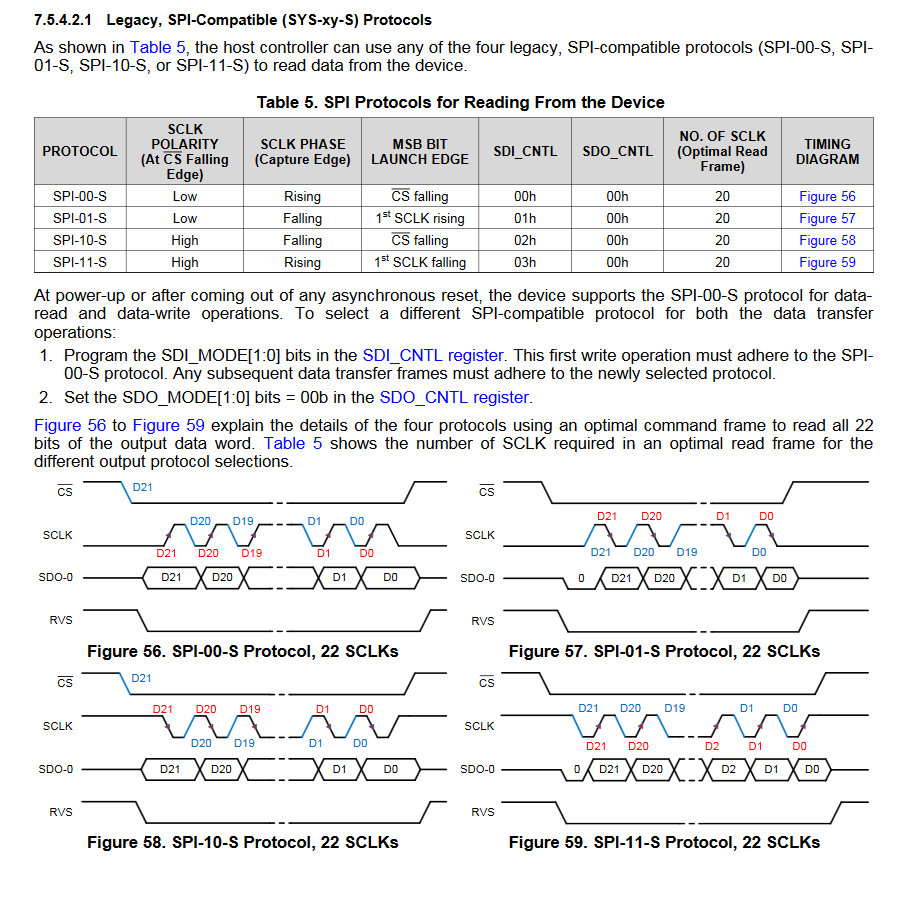

http://www.ti.com/lit/ds/symlink/ads8904b.pdf

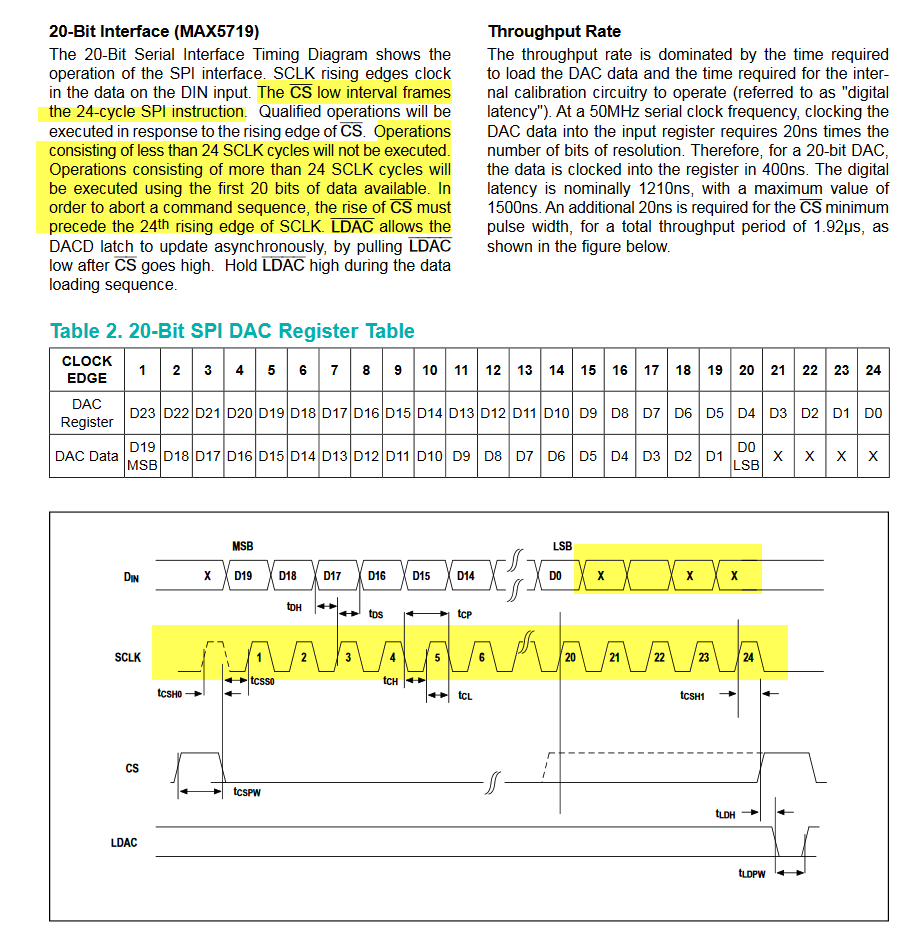

https://www.maximintegrated.com/en/ds/MAX5717-MAX5719.pdf

Note in particular the CS requirements in the either datasheet above (CS must be held low for 20-bit duration).

There many other 20-bit SPI parts with similar requirements.

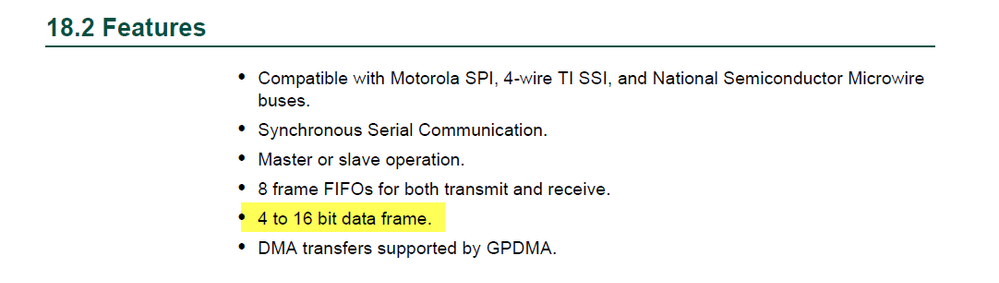

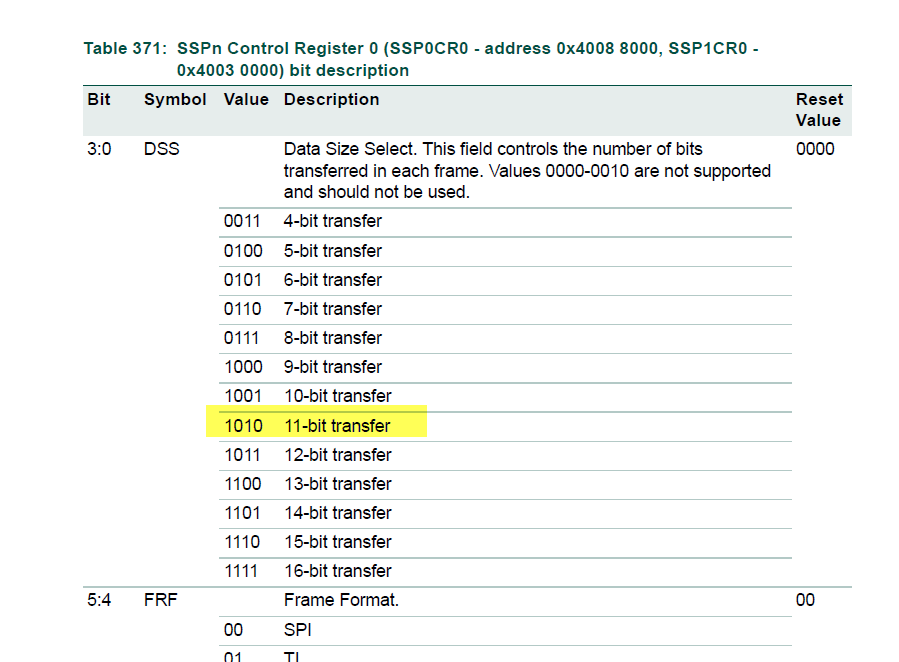

I had a quick read of the LPC176x SSP description here: https://www.nxp.com/docs/en/user-guide/UM10360.pdf

I can't see how one does a transfer longer than 16 bits (which is supported for example on Kinetis SPI).

How does one do a 20-bit SPI transfer?

Does this apply across all LPC family devices or do some have different SPI capabilities?

Thanks in advance,

Best Regards, Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dave Nadler,

LPC176X ssp can't support the 20bit SPI directly.

So, if you really want to use 20bit SPI, you need to use the GPIO to simulate it.

About the CS requirements, it's easy to realize it, just use the GPIO to control it.

But I have roughly review your SPI slaves:

1. ADS8904B from IT

page 37

You can find it actually need 22 clocks.

So, I think if you need to use SSP, you can use two 11 bits:

The CS can be controlled by the GPIO, don't use the SSP hardware CS function.

About the data, after you received two 11bits, you can combine two 11bits data together.

2. max5717 from maximintegrated

page 10.

You can find it is the 24 clocks, so you can use two 12 bits SSP or 3 8-bits SSP, then combine it together.

The CS pin still be controlled by the GPIO.

As I know, the SPI module in the LPC series, no chip can support 20 bits directly, so you need to divide it, or use the GPIO to simulate it.

Wish it helps you.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Kerry, but we need hardware to control CS properly; no software involvement until ADC data is read into SRAM, and no CPU involvement to output DAC values. If we used GPIO for CS, can the DMA of LPC parts frame the SPI transfer with proper CS assert-deassert using DMA chaining? Or perhaps controlled by a timer?

We can't control CS SPI framing in software, otherwise we end up spending a huge % of available CPU time mucking about with the SPI transfer; absolutely not OK in our applications.

Should we give up on LPC parts and use Kinetis, which can do 20-bit SPI easily with Kinetis' SPI controller?

Are Kinetis not recommended for new designs? I don't see any new parts or new smaller packages for Kinetis?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dave,

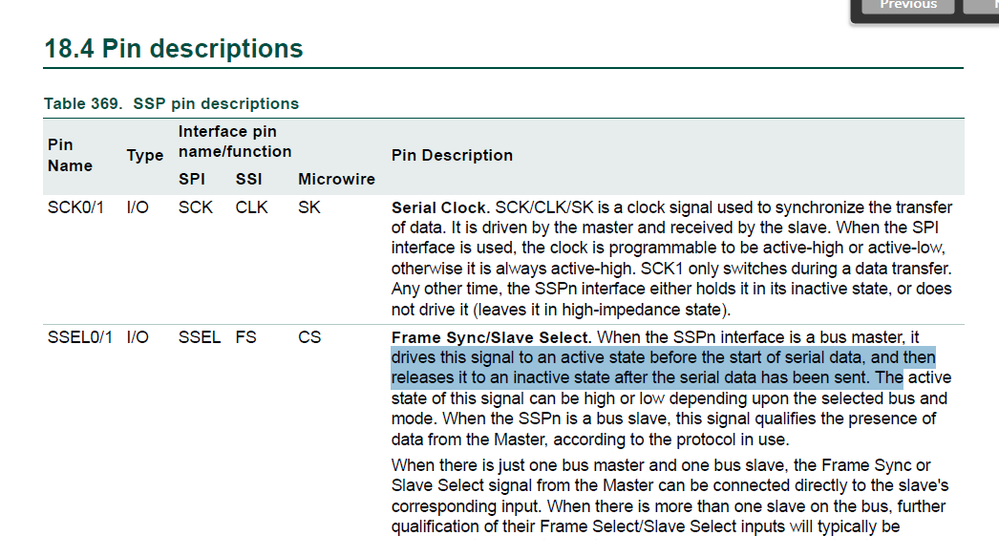

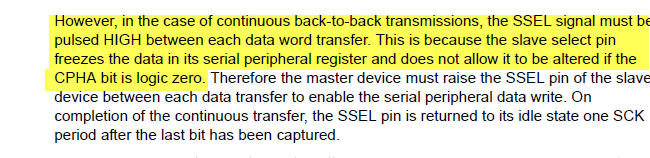

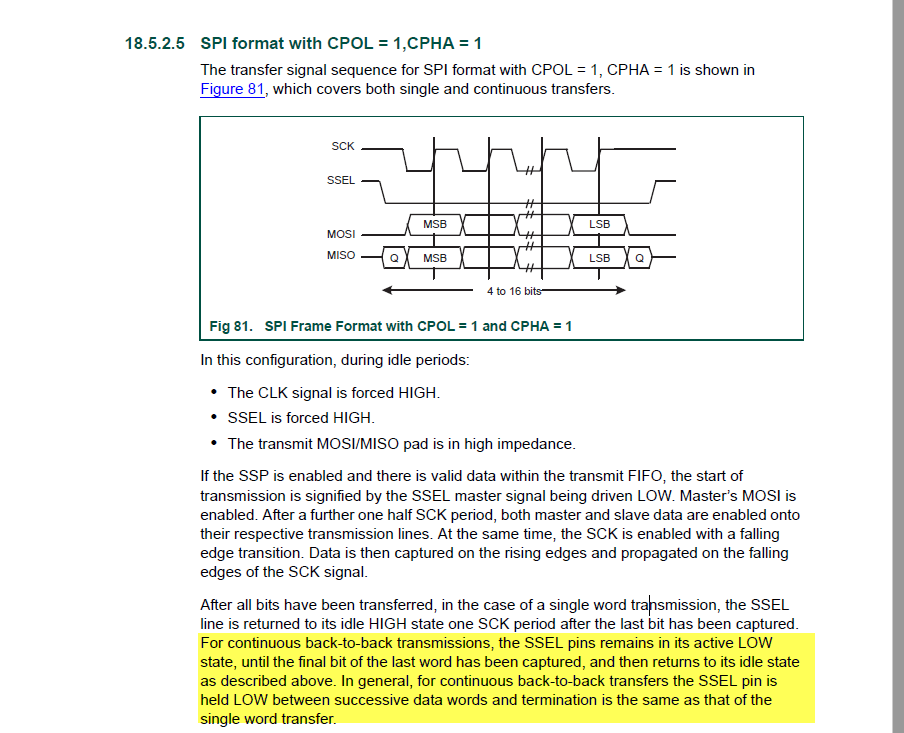

Hardware control CS idle state is determined by the status, please check this information:

So, if you want to use the hardware control, maybe you need to choose CPHA=1, but you need to check your SPI slave, if you choose this method, your slave should also have the same CPHA. Otherwise CPHA=0, the SSEL will be pull to idle status after each data word transfer.

If you are using DMA, you can consider to use the CPHA=1.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry, you have not answered the question. Can you confirm:

LPC MCUs hardware cannot support 20-bit SPI transfer bracketed by CS low without software bit-banging of at least CS control. No work-around using timers and/or DMA is possible; CPU involvement is required.

Thanks,

Best Regards, Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dave Nadler,

1. Yes, MCU can't support 20bit directly, but please check your slaver, actually it is 24 bits, so just as I told you, you can use 3*8bits to replace the 24bits. even it is the 20bits, you can use 2*10bits to replace it. But the data you need to prepare it in divide mode, then combine it together by yourself.

2. If the CS is low without software GPIO control, you need to use CPHA=1, this mode can keep the CS low without GPIO control. But CPHA=0, you still need to control it with the software. If you want to use the timers or DMA to control the CS, of course you can, but how to synchronize the SPI with the GPIO CS correctly is a problem, it will make problem more complicated. So, if you can't use CPHA=1, maybe you really need to consider to use cpu involvement.

Wish it helps you!

If you still have question about it, please kindly let me know.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------