- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- S12ZVLA ADC sampling time

S12ZVLA ADC sampling time

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S12ZVLA ADC sampling time

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I need information regarding the precise calculation of ADC sampling time, please go through the controller and configuration that I am using:

Controller: S12ZVLA96

f_bus(bus frequency): 32Mhz

ADC : 6-channel 10 bit

ADC operating mode: Restart Mode, Single access mode

ADC Command sequence list length: 36

Please help me with the information on, what will be the time required for completing conversion of one channel, once a command in command list has been loaded.

As per data sheet I found two calculation related to ADC sampling time, below I mentioned those two formula,

1) Conversion time = 5 Bus cycles + 2 ADC conversion cycles

2) Total Sample time = Buffer sample time + Final Sample time

= 2 ADC CLK + 2 ADC CLK

Can you provide how to correlate these two equations, and what will be the total time required for completing the 36 commands , for the above configuration?

Thanks ,

Vyshakh J

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vyshakh,

The ADC module needs a trigger to start sampling the first channel in Restart Mode.

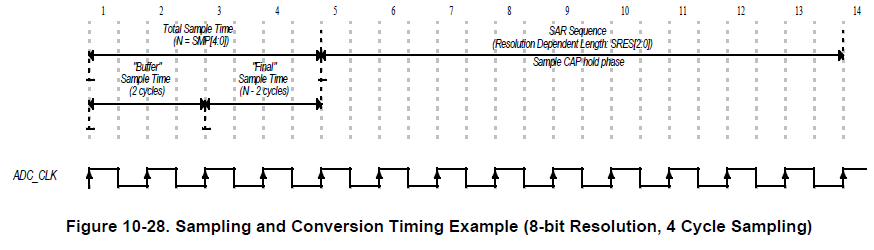

It takes 2 BUS cycles + 2 ADC Cycles (pump phase) from the Trigger Event (bit TRIG set) until the select channel starts to sample. The pump phase (buffer sample time) is already a part of the Total Sample Time (N = SMP[4:0]), as described in Figure 10-28.

And the Total Sample Time is a part of the entire ADC Conversion Period (Table C-1 ADC Operating Characteristics).

10-bit resolution:

min. 18 ADC cycles (4 S + 14 C)

max. 38 ADC cycles (24 S + 14 C)

During a conversion sequence (back to back conversions) it takes five Bus Clock cycles plus two ADC conversion clock cycles (pump phase) from current conversion period end until the newly selected channel is sampled in the following conversion period.

Again, the pump phase is a part of the Total Sample Time (N = SMP[4:0]).

The conversion time of 36 commands after Trigger event in Restart mode is:

2 BUS cycles + (36 * ADC Conversion Period (18 – 38 ADC cycles)) + ((36-1) * 5 BUS cycles between two conversions).

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your information, it was really helpful. But here ,I have one more query , please go through the below comments,

Out of 36 command in command sequence list, some of the command is for discharging the internal capacitance and one command for temperature sensor sampling

* What will be the time required for completing 'discharge internal capacitance' command? Is it same as ADC conversion time?

Thanks,

Vyshakh J

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vyshakh,

Each command specifies the length of the sample time in ADC cycles.

ADCCMD_2_SMP[4:0]. So it depends on that.

Regards,

Daniel