- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Continuation of FCCU DISCUSSION Previous THREAD Number : 466634

Continuation of FCCU DISCUSSION Previous THREAD Number : 466634

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Continuation of FCCU DISCUSSION Previous THREAD Number : 466634

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter & NXP Team,

After POWER ON RESET of MPC5741 , I find that there is NO STATUS LATCHED ERRORS and FCCU can able to go to CONFIG state and back to NORMAL. Once i give DEBUGGER RESET only, we find the below ERRORS.

* SYSTEM RAM CORRECTABLE ERRORS

* SYSTEM RAM UNCORRECTABLE ERRORS

* SYSTEM RAM OVERFLOW ERRORS.

And we got to know that , the above is happening because of BIST activation after RESET and we confirmed it by disbaling the BIST. Thanks for sharing the BIST disbale cmm file.

But the SAME CODE , if we flash it in MPC5744P, i find the following errors after POWER ON RESET.

* SAFETY CORE EXCEPTION ERROR. ---- NCF[ 44 ]

* FIRST TIMEOUT INTERRUPT REQUEST FROM SOFTWARE WATCH DOG OF SAFETY CORE --- NCF[72 ]

and FCCU is turning to FAULT STATE and could not able to enter into "CONFIG " state itself.

COULD YOU PLEASE HELP US IN UNDERSTANDING THE ABOVE CONTRADICTION...PLEASE...?

As a finite Solution for the above issue, we thought and working toward clearing all the FAULTS SOURCES before we initialize the FCCU . ( For Ex: Clearing the error flags of MEMU, CGM,PMC, ADC..........................).

REQUEST YOU TO GIVE YOUR COMMENTS OVER THE ABOVE ACTIVITY..? Is it worthwhile decision or Any other solution is there...?

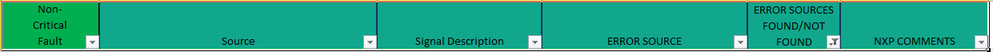

Here i attached an excel sheet containing the following columns.

Out of 74 faults, nearly 42 error sources have been found and remaining ( particularly BIST & CORE related stuffs ), we are feeling tough to progress over.

REQUEST YOU TO have look on the excel sheet and place your comments that would be HIGHLY HELPFUL for us for the further MOVE.

Your Guidence & SUPPORT is highly needed as the product application NEEDS FCCU activity for sure..

Expecting your reply/support...

Thanks & Regards

Santhosh Kumar.N

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was some days out of office as I was sick.

To see NCF[44] after power on reset is nothing strange. You can ignore it after PoR and just simply clear it with your SW. This is caused by design of reset phase in micro.

NCF[72] is cause by first expiration of watchdog SWT_0. Make sure you handle SWT in time predefined in TO register. Or disable SWT and you wont get this fault.

What comments do you want to hear? Did you checked my AN regarding panther FCCU faults?

https://www.nxp.com/docs/en/application-note/AN5259.pdf?fsrch=1&sr=3&pageNum=1

I tried to explain all FCCU fault sources on this device here.

Peter