- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- How does M4 and A9 on i.mx6sx access DDR

How does M4 and A9 on i.mx6sx access DDR

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How does M4 and A9 on i.mx6sx access DDR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In my i.mx6sx sdb board,there is only a DDR3(1G),How can I allocate some memory(such as 200M) as shared memory ? How dose M4 and A9 access the shared memory I allocated?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jingyang, Hello Carlos,

I have similar need for a 16MB shared space but using the i.MX7D. I built the rpmsg examples and they're great for what they are - a pingpong exchange and string echo. The maximum size allowed in the reference FreeRTOS rpmsg implementation is 512 bytes (.../middleware/multicore/open-amp/rpmsg/rpmsg_core.h line 44, RPMSG_BUFFER_SIZE definition). It seems doubtful that buffer size can be increased to 16 or 200MB.

I am looking at using a device tree reserved-memory object to define and access a shared memory block. See linux rel_imx_4.1.15_1.1.0_ga/arch/arm/boot/dts/imx6sx.dtsi for example defining a shared-dma-pool. Access could be managed using the Messaging Unit or other cooperative method. Is this a viable approach? The iMX7D DRM Section 4.3.3.3.2 provides a high level description as "Passing fixed-length data"; Section 4.3.3.8 and 4.3.3.9 discuss interrupt-based methodologies for access control. Does an example implementation exist?

Thank you, Joe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Joseph

Could you tell me how can the M4 access a device tree reserved-memory ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i.MX Development Miscellanea(i.MX 开发杂记)

https://community.nxp.com/docs/DOC-335198

i.MX6SX_M4_MPU_Settings_For_RPMSG_04132018.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Sun

Do you know why doesnot the IMX6SXRM talk about MPU for M4 in details?The resigters for MPU in FreeRTOS porject can not be found in IMX6SXRM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

M4 is the same way to use address to access the Linux reserved memory. Reserve just let Linux don't destroy the memory for M4. If the memory is for M4 only, you can use M4 to configure cacheable to make it fast. But for rpmsg. has to be non cacheable.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joe,

as you can see in Table 2-1. System memory map and Table 2-2. CM4 memory map, there are 1536MB available as shared memory at address 0x80000000 which is for the MMDC x32DDR Controller.

You may edit the RPMsg demo application to allocate and initialize the RPMsg driver resources in this area. You may find RPMsg APIS in RPMsg RTOS Layer User’s Guide (RPMsg_RTOS_Layer_User’s_Guide.pdf).

Regards,

Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

I've reviewed the rpmsg implementations in both the FreeRTOS and Linux code bases. Both define the used buffer size to 512 bytes, with Linux allocating 512 such buffers for a total of 256KB. I need to push a few MBs of control info from the A7 through the M4. It doesn't look like rpmsg is built for that.

I have defined a 16MB block as reserved-memory and can access it from the A7 and M4. Is there some mechanism one can use to force the relevant core cache flush and then indicate the flush is complete to the other core? Something akin to using the vertical blanking interval for video frame updates? At the moment it appears the M4 "misses" some memory updates 64 bytes at a time (I have the M4 continually reading memory blocks and dumping the contents).

Thank you, Joe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joe,

I don't see a direct way to indicate a core that the other core flushed cache. You may interrupt the other core when cache is flushed or use a message which would be the same process but in a higher layer using FreeRTOS services.

Regards,

Carlos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, I can figure out a way to signal, e.g. MU_ACR/MU_BCR or another mechanism. It doesn't appear that the "standard" Linux cacheflush() call is available. Is there another call which should be used?

When loading the M4 using u-boot we issue a "dcache flush" command. I tracked that functionality down into arch/arm/cpu/armv7/cmd_m4boot.c. Where does this capability live in the Linux tree?

All the best, Joe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Anyone knows?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jingyang xie,

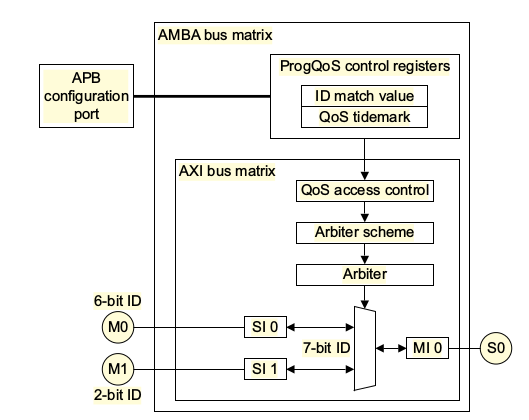

First look at Figure 43-1. NIC-301 Bus System. This drawing does have a couple of flaws: The dark blue box labeled ENET connected to the light blue box labeled Main should actually be a light blue box. The light blue boxes represent bus switches that route signals along AXI buses. Also, the Cortex A9 core in a dark blue box should connect directly to the Main switch. Ignore the top line of that page. There are seven switches, not five and the five listed are not the correct names (left over from i.MX6Q).

So what to do with this knowledge. The Table 43-6 QoS and tidemark parameters provide the "Quality of Service" values that are assigned to traffic as they enter the NIC-301 system. The switch M4 has 3 port listings: M4-0 and M4-1 are both assigned a QOS value of "2", by default. The gpv6 port goes to the Wakeup switch and is not important to this discussion. Then comes the Switch Main which has nine ports assigned. The two ports for A9-0 and A9-1 are the AXI buses to the A9 core. The are assigned a QoS factor of "0". There is also a port connecting the Main switch to the M4 switch. It has a QoS of "0", but that does not mean that traffic coming from the M4 gets its QoS reassigned to "0". The original QoS factor stays with the traffic throughout its lifetime.

Then, if you go to section 40.5.1.3 Dynamic scoring mode, you will see a discussion of how the MMDC will score and service traffic requests. It should be reasonably self explanatory. A higher score results in higher priority, so the QoS assigned by the NIC to M4 gives it an edge over the A9 core (except that the MMDC traffic from the M4 core does have to go through one extra switch than the A9 core for a little extra travel time).

The QoS values assigned by the NIC can be changed. First you need the base address of the appropriate NIC listed in Table 43-2. CM4 GPV ports memory allocations (see note below). For the M4 port, the base address starts at 0x41100000. Then look at Table 43-6 for the port number on the M4 switch: M4-0 = 66 and M4-1 =67. multiply that number by 0x1000 to get the start address for that port. Example: M4-0 = 66, so the setting for this port are stored at 0x41100000 + 66*0x1000 is 0x41142000. Then use the offsets from Table 43-5 to find the register address of the desired QoS score. There are two: One for Read accesses and one for Write accesses.

NOTE: If you look in the reference manual you will see a similar table Table 43-1 CA9 GPV ports memory allocations with different addresses. Even though they have different addresses, they access the same information from within the single AIPS table storage location. So if you set the QoS value using the registers for the M4 core (bit-30 = 'b1), the A9 core will find the same information using an address in which bit-30 = 'b0.

Regards,

Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have doubt with the QoS. If the QoS says the priority of the Master, why the PL301 has two arbitration schemes (LGR and RR)? Besides, I not able to find which one is the default one.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Carlos

Thanks for your prompt reply.But It's a bit complicated for me,Can you give me some example apps ?

PS : My intention is to allocate some memory form DDR3,and A9 can write data in the memory,M4 can read the data from the same memory.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jingyang xie,

you can take a look to RPMsg with FreeRTOS.

You can download FreeRTOS for IMx6SX here:

http://www.nxp.com/imx6SX > Software & Tools tab

FreeRTOS™ BSP 1.0.1 for the i.MX 6SoloX ARM® Cortex®-M4 core

You will need the following documentation:

i.MX_Linux_User's_Guide.pdf

3 Basic Terminal Setup

The USB to serial driver can be found under www.ftdichip.com/Drivers/VCP.htm

i.MX_Linux_Reference_Manual.pdf

51 Remote Processor Messaging (RPMsg)

Getting_Started_with_FreeRTOS_BSP_for_i.MX_6SoloX.pdf

6 Running Application with U-Boot

FreeRTOS_BSP_for_i.MX_6SoloX_Demo_User’s_Guide.pdf

10 RPMsg Ping-Pong FreeRTOS Demo with RTOS API

Once you installed FreeRTOS build rpmsg demos to generate .bin file. E.g. C:\NXP\FreeRTOS_BSP_1.0.1_iMX6SX\examples\imx6sx_sdb_m4\demo_apps\rpmsg\pingpong_freertos\<compiler>

Then boot in A9 core and stop in uboot to configure the M4 application. I have made in 2 different ways:

ONE

env default -a

setenv fdt_file imx6sx-sdb-m4.dtb

setenv m4image 'rpmsg_pingpong_freertos_example.bin'

setenv run_m4_tcm 'if run loadm4image; then cp.b ${loadaddr} 0x7f8000 0x8000; bootaux 0x7f8000; fi'

setenv bootcmd "run run_m4_tcm;${bootcmd}"

setenv mmcargs "${mmcargs} uart_from_osc"

saveenv

boot

TWO

env default –a

setenv m4image 'rpmsg_pingpong_freertos_example.bin'

setenv fdt_file imx6sx-sdb-m4.dtb

setenv bootcmd "run m4boot;${bootcmd}"

setenv mmcargs "${mmcargs} uart_from_osc"

run update_m4_from_sd

saveenv

boot

Finally launch M4 application from A9 cmd:

$ cd /lib/modules/4.1.15-1.2.0+g77f6154/kernel/drivers/rpmsg

$ insmod imx_rpmsg_pingpong.ko

$ rmmod imx_rpmsg_pingpong

Regards,

Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------