- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Flexbus and SDRAM Multiplex on K65F_169GBA

Flexbus and SDRAM Multiplex on K65F_169GBA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am going to use 2 32-bit SDRAMs on SDRAM controller. And want to add 16-bit external flash to Flexbus.

Could anybody check if the following pin assignment should be OK if I don't want to use external multiplex circuit?

/* Initialize the SDRAMC pins */

/* Ungate the port clock */

CLOCK_EnableClock(kCLOCK_PortA);

CLOCK_EnableClock(kCLOCK_PortB);

CLOCK_EnableClock(kCLOCK_PortC);

CLOCK_EnableClock(kCLOCK_PortD);

/* CLKOUT*/

PORT_SetPinMux(PORTA, 6UL, kPORT_MuxAlt5); // SDRAM CLKOUT

/* CAS/RAS*/

PORT_SetPinMux(PORTB, 0UL, kPORT_MuxAlt5); // SDRAM_CAS_b

PORT_SetPinMux(PORTB, 1UL, kPORT_MuxAlt5); // SDRAM_RAS_b

/* WE */

PORT_SetPinMux(PORTB, 2UL, kPORT_MuxAlt5); // ENET0_1588_TMR0/SDRAM_WE

/* CS */

PORT_SetPinMux(PORTB, 3UL, kPORT_MuxAlt5); // ENET0_1588_TMR1/SDRAM_CS0

PORT_SetPinMux(PORTB, 4UL, kPORT_MuxAlt5); // ENET0_1588_TMR2/SDRAM_CS1

/* SDRAM Data*/

PORT_SetPinMux(PORTA, 24UL, kPORT_MuxAlt5); /* SDRAM_D15/FB_A15*/

PORT_SetPinMux(PORTA, 25UL, kPORT_MuxAlt5); /* SDRAM_D14/FB_A14*/

PORT_SetPinMux(PORTA, 26UL, kPORT_MuxAlt5); /* SDRAM_D13/FB_A13*/

PORT_SetPinMux(PORTA, 27UL, kPORT_MuxAlt5); /* SDRAM_D12/FB_A12*/

PORT_SetPinMux(PORTA, 30UL, kPORT_MuxAlt5); /* SDRAM_D11/FB_A11*/

PORT_SetPinMux(PORTA, 31UL, kPORT_MuxAlt5); /* SDRAM_D10/FB_A10*/

PORT_SetPinMux(PORTB, 6UL, kPORT_MuxAlt5); /* SDRAM_D23*/

PORT_SetPinMux(PORTB, 7UL, kPORT_MuxAlt5); /* SDRAM_D22*/

PORT_SetPinMux(PORTB, 8UL, kPORT_MuxAlt5); /* SDRAM_D21*/

PORT_SetPinMux(PORTB, 9UL, kPORT_MuxAlt5); /* SDRAM_D20*/

PORT_SetPinMux(PORTB, 10UL, kPORT_MuxAlt5); /* SDRAM_D19*/

PORT_SetPinMux(PORTB, 11UL, kPORT_MuxAlt5); /* SDRAM_D18*/

PORT_SetPinMux(PORTB, 12UL, kPORT_MuxAlt5); /* SDRAM_D9/FB_A9*/

PORT_SetPinMux(PORTB, 13UL, kPORT_MuxAlt5); /* SDRAM_D8/FB_A8*/

PORT_SetPinMux(PORTB, 14UL, kPORT_MuxAlt5); /* SDRAM_D7/FB_A7*/

PORT_SetPinMux(PORTB, 15UL, kPORT_MuxAlt5); /* SDRAM_D6/FB_A6*/

PORT_SetPinMux(PORTB, 16UL, kPORT_MuxAlt5); /* SDRAM_D17*/

PORT_SetPinMux(PORTB, 17UL, kPORT_MuxAlt5); /* SDRAM_D16*/

PORT_SetPinMux(PORTB, 20UL, kPORT_MuxAlt5); /* SDRAM_D31*/

PORT_SetPinMux(PORTB, 21UL, kPORT_MuxAlt5); /* SDRAM_D30*/

PORT_SetPinMux(PORTB, 22UL, kPORT_MuxAlt5); /* SDRAM_D29*/

PORT_SetPinMux(PORTB, 23UL, kPORT_MuxAlt5); /* SDRAM_D28*/

PORT_SetPinMux(PORTC, 12UL, kPORT_MuxAlt5); /* SDRAM_D27*/

PORT_SetPinMux(PORTC, 13UL, kPORT_MuxAlt5); /* SDRAM_D26*/

PORT_SetPinMux(PORTC, 14UL, kPORT_MuxAlt5); /* SDRAM_D25*/

PORT_SetPinMux(PORTC, 15UL, kPORT_MuxAlt5); /* SDRAM_D24*/

PORT_SetPinMux(PORTC, 24UL, kPORT_MuxAlt5); /* SDRAM_D5/FB_A5*/

PORT_SetPinMux(PORTC, 25UL, kPORT_MuxAlt5); /* SDRAM_D4/FB_A4*/

PORT_SetPinMux(PORTC, 26UL, kPORT_MuxAlt5); /* SDRAM_D3/FB_A3*/

PORT_SetPinMux(PORTC, 27UL, kPORT_MuxAlt5); /* SDRAM_D2/FB_A2*/

PORT_SetPinMux(PORTC, 28UL, kPORT_MuxAlt5); /* SDRAM_D1/FB_A1*/

PORT_SetPinMux(PORTC, 29UL, kPORT_MuxAlt5); /* SDRAM_D0/FB_A0*/

/* SDRAM Address*/

PORT_SetPinMux(PORTB, 18UL, kPORT_MuxAlt5); /* SDRAM_A23*/

PORT_SetPinMux(PORTC, 0UL, kPORT_MuxAlt5); /* SDRAM_A22*/

PORT_SetPinMux(PORTC, 1UL, kPORT_MuxAlt5); /* SDRAM_A21*/

PORT_SetPinMux(PORTC, 2UL, kPORT_MuxAlt5); /* SDRAM_A20*/

PORT_SetPinMux(PORTC, 4UL, kPORT_MuxAlt5); /* SDRAM_A19*/

PORT_SetPinMux(PORTC, 5UL, kPORT_MuxAlt5); /* SDRAM_A18*/

PORT_SetPinMux(PORTC, 6UL, kPORT_MuxAlt5); /* SDRAM_A17*/

PORT_SetPinMux(PORTC, 7UL, kPORT_MuxAlt5); /* SDRAM_A16*/

PORT_SetPinMux(PORTC, 8UL, kPORT_MuxAlt5); /* SDRAM_A15*/

PORT_SetPinMux(PORTC, 9UL, kPORT_MuxAlt5); /* SDRAM_A14*/

PORT_SetPinMux(PORTC, 10UL, kPORT_MuxAlt5); /* SDRAM_A13*/

PORT_SetPinMux(PORTD, 2UL, kPORT_MuxAlt5); /* SDRAM_A12*/

PORT_SetPinMux(PORTD, 3UL, kPORT_MuxAlt5); /* SDRAM_A11*/

PORT_SetPinMux(PORTD, 4UL, kPORT_MuxAlt5); /* SDRAM_A10*/

PORT_SetPinMux(PORTD, 5UL, kPORT_MuxAlt5); /* SDRAM_A9*/

/* SDRAM_CKE*/

PORT_SetPinMux(PORTD, 7UL, kPORT_MuxAlt5);

/* SDRAM_DQM */

PORT_SetPinMux(PORTC, 16UL, kPORT_MuxAlt5); /* SDRAM_DQM2*/

PORT_SetPinMux(PORTC, 17UL, kPORT_MuxAlt5); /* SDRAM_DQM3*/

PORT_SetPinMux(PORTC, 18UL, kPORT_MuxAlt5); /* SDRAM_DQM1*/

PORT_SetPinMux(PORTC, 19UL, kPORT_MuxAlt5); /* SDRAM_DQM0*/

/* Flexbus high address */

PORT_SetPinMux(PORTD, 8UL, kPORT_MuxAlt6); /* FB_A16*/

PORT_SetPinMux(PORTD, 9UL, kPORT_MuxAlt6); /* FB_A17*/

PORT_SetPinMux(PORTD, 10UL, kPORT_MuxAlt6); /* FB_A19*/

PORT_SetPinMux(PORTD, 11UL, kPORT_MuxAlt6); /* FB_A19*/

PORT_SetPinMux(PORTD, 12UL, kPORT_MuxAlt6); /* FB_A20*/

PORT_SetPinMux(PORTD, 13UL, kPORT_MuxAlt6); /* FB_A21*/

PORT_SetPinMux(PORTD, 14UL, kPORT_MuxAlt6); /* FB_A22*/

PORT_SetPinMux(PORTD, 15UL, kPORT_MuxAlt6); /* FB_A23*/

PORT_SetPinMux(PORTA, 29UL, kPORT_MuxAlt6); /* FB_A24*/

PORT_SetPinMux(PORTA, 28UL, kPORT_MuxAlt6); /* FB_A25*/

/* Flexbus RW, OE, chip select and etc signal */

PORT_SetPinMux(PORTB, 19UL, kPORT_MuxAlt5); /* FB_OE_b*/

PORT_SetPinMux(PORTC, 11UL, kPORT_MuxAlt5); /* FB_RW_b*/

PORT_SetPinMux(PORTD, 0UL, kPORT_MuxAlt5); /* FB_CS1_b*/

PORT_SetPinMux(PORTD, 1UL, kPORT_MuxAlt5); /* FB_CS0_b*/

Thanks,

Christie

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1> When BLS=0, FB_AD[0:15] will be driven as address during FLEXBUS read/write. And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write.

2> When BLS=1, FB_AD16~~AD31 will be driven as address during FLEXBUS read/write. And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write.

The SDRAM and Flexbus multiplexed pins was automatically switched, customer could refer AN5095 about some detailed info.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My question: As my pin assignment, during Flexbu read/write, the address will be available on FB_AD0~~FB_AD15 on the first clock, then will be switch to data. But, FB_AD16~~FD_AD31 will always be valid data if I use 16-bit port. At the same time, FB_A0~~FB_A25 will be always valid address during read/write, so I can use these for Flexbus address to access the external device in non-multiple mode.

Can someone confirm my pin assignment?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

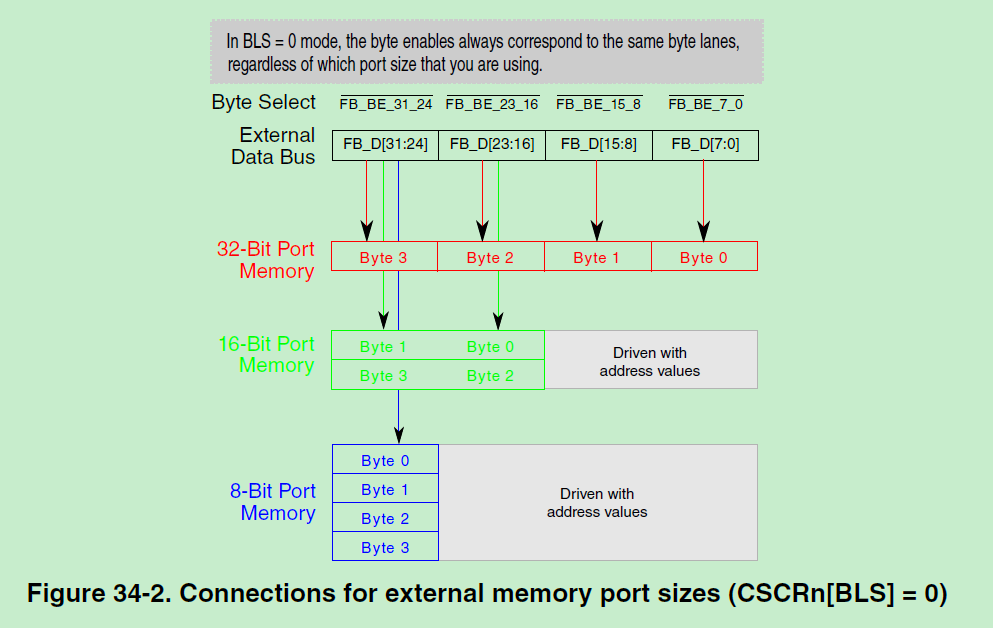

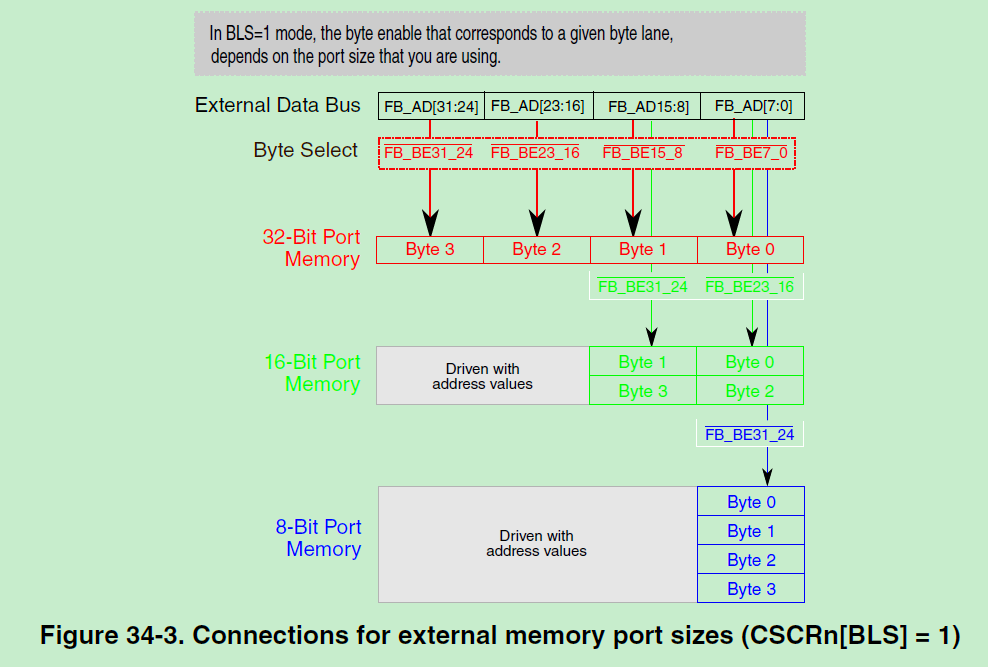

The Flexbus data-byte alignment and physical connections based on FB_CSCRn[BLS] bit setting:

During the Flexbus operation, the FB_A[0:25] pins are always driven as address function. Customer can use those pins as Flexbus address pins.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ma Hui,

Thank you for youe answers. I just want to confirm the following because I am doing the hardware design for now.

I am using FLEXBUS for 16-bit operation:

1) If BLS=0, FB_AD0~~AD15 will be driven as address during FLEXBUS read/write? And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write? So, I can use FB_AD[0:15]+FB_A[16:25] as no multiplex address and will be the same function as I use FB_A[0:25]?

2) if BLS=1, FB_AD16~~AD31 will be driven as address during FLEXBUS read/write? And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write? So, I can use FB_A[0:15]+FB_AD[16:25] as no multiplex address and will be the same function as I use FB_A[0:25]?

All above signals will be switched automatically between SDRAM and FLEXBUS operation? Do I need to configure for FLEXBUD multiplex/non-multiplex mode?

Thanks,

Christie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1> When BLS=0, FB_AD[0:15] will be driven as address during FLEXBUS read/write. And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write.

2> When BLS=1, FB_AD16~~AD31 will be driven as address during FLEXBUS read/write. And at the same time, FB_A0~~FB_A25 will be driven as address during FLEXBUS read/write.

The SDRAM and Flexbus multiplexed pins was automatically switched, customer could refer AN5095 about some detailed info.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------