- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX6, LDB_DI0_SERIAL_CLK_ROOT clock source change

IMX6, LDB_DI0_SERIAL_CLK_ROOT clock source change

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

What is the correct procedure for changing the clock source for LDB_DI0_SERIAL_CLK_ROOT?

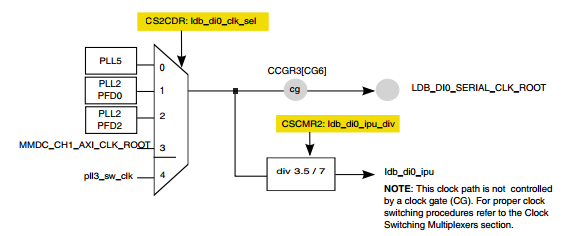

Currently we are showing startup image on LVDS display already in U-Boot. First we configure PLL5 to have needed frequency for LVDS interface (33MHz) and then set the mux (picture below) in reqister CS2CDR to use PLL5. However, occasionally in cold boot the LVDS interface does not drive any signal to the TFT panel. This jamming happens already in U-Boot. When the default clock source MMDC_CH1_AXI_CLK_ROOT is used the LVDS interface is not detected to fail, although then the clock frequency is incorrect for the TFT panel.

In reference manual is mentioned that for proper clock switching procedure both the current clock and the clock to be selected must remain active during the entire selection process. So could you provide a code or pseudo code, what is the correct setting sequence to select PLL5 for LDB_DI0_SERIAL_CLK_ROOT and LDB_DI0_IPU? U-Boot base is boundarydevices U-boot dated 25.3.2013.

-Jani

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jani

one can look at Support-LVDS-clock-source-from-PLL5.patch

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jani

for changing pll frequency procedure one can look at sect.18.5.1.6

Disabling / Enabling PLLs i.MX6DQ Reference Manual (rev.3 7/2015)

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6DQRM.pdf

and EB790 Configuration of Phase Fractional Dividers

http://cache.freescale.com/files/32bit/doc/eng_bulletin/EB790.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Igor,

Thank you for the information. The linked documents refer mainly to PLL configuration which is important information. As the note in reference manual says "proper clock switching" procedures should be followed.

Does that mean that the MUX in this case should be set to use PLL5 after the PLL5 is enabled or should the mux be switched before enabling PLL5?

I have seen Linux patches for rather odd mux configuration sequence, as in discussion linked below.

[PATCH] ARM: imx6: Fix procedure to switch the parent of LDB_DI_CLK

And should the IPU/LDB be configured before or after clock enabling?

Kind regards,

-Jani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jani

general procedure is to enable/lock pll then switch muxes

and enable modules. Referenced patch seems described some

special case.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Still I would like to know how to switch from default clock source (MMDC_CH1_AXI_CLK_ROOT) to PLL5, without introducing a glitch to the divider? Please see the picture in the original post. It is mentioned in the reference manual that:

"The input clocks to the mux are required to be gated before switching the source clock in

the CCM clock mux and the output should also be gated. If the input and output clocks

are not gated, clock glitches can propagate to the logic that follows the clock mux,

causing the logic to behave unpredictably."

If I have understood correctly the default clock MMDC_CH1_AXI_CLK_ROOT is not gated. So how to handle "gating" since the default clock does not have a gate (CG)?

Kind regards,

-Jani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jani

one can look at Support-LVDS-clock-source-from-PLL5.patch

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thank you for your help. The default clock MMDC_CH1_AXI_CLK_ROOT change seemed to be the problem. In the patches, that you listed, is preformed a certain procedure for clock source change. If it is not done according to the patch LVDS interface may jam occasionally.

-Jani