- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- How to cacluate the bus clock of S12ZVMC12

How to cacluate the bus clock of S12ZVMC12

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to cacluate the bus clock of S12ZVMC12

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

Could some body can tell me on which DOC can find the detaild description of S12ZVMC12 clock ,

and how to caculate the bus clock , and the biggest bus clock ?

Thank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The busclk you can use to calculate setupr reqisters for is within interval from1MHz to 50MHz for temperature range from -40deg.C. to +150deg.C. Over this temperature range max bus frequency is limited to 40MHz.

Calculation is simple. you can either select as a source clock internal 1MHz oscillator or some external oscillator.

On the basis of used oscillator and configuration of the circuitry you can select between PEI, PBE and PEE modes.

PLL Engaged Internal (PEI)

— This is the default mode after System Reset and Power-On Reset.

— The Bus Clock is based on the PLLCLK.

— After reset the PLL is configured for 50MHz VCOCLK operation.

Post divider is 0x03, so PLLCLK is VCOCLK divided by 4, that is 12.5MHz and Bus Clock is

- 6.25MHz.

The PLL can be re-configured for other bus frequencies.

— The reference clock for the PLL (REFCLK) is based on internal reference clock IRC1M.

• PLL Engaged External (PEE)

— The Bus Clock is based on the PLLCLK.

— This mode can be entered from default mode PEI by performing the following steps:

– Configure the PLL for desired bus frequency.

– Program the reference divider (REFDIV[3:0] bits) to divide down oscillator frequency if

- necessary.

– Enable the external oscillator (OSCE bit).

– Wait for oscillator to start up (UPOSC=1) and PLL to lock (LOCK=1).

• PLL Bypassed External (PBE)

— The Bus Clock is based on the Oscillator Clock (OSCCLK).

— The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to

make sure a valid PLL configuration is used for the selected oscillator frequency.

— This mode can be entered from default mode PEI by performing the following steps:

– Make sure the PLL configuration is valid for the selected oscillator frequency.

– Enable the external oscillator (OSCE bit).

– Wait for oscillator to start up (UPOSC=1).

– Select the Oscillator Clock (OSCCLK) as source of the Bus Clock (PLLSEL=0).

— The PLLCLK is on and used to qualify the external oscillator clock.

The calculation of setup registers is realy simple by formulas presented in capters

- 8.3.2.2 S12CPMU_UHV_V6 Synthesizer Register (CPMUSYNR)

- 8.3.2.3 S12CPMU_UHV_V6 Reference Divider Register (CPMUREFDIV)

- 8.3.2.4 S12CPMU_UHV_V6 Post Divider Register (CPMUPOSTDIV)

The only you have to think about is that BUSCLK = fpll/2 for PEI and PEE modes and fosc/2 in the PBE mode.

The example for CPMU setup in the PEI mode is presented in the reference manual:

- 8.7.3 Application Information for PLL and Oscillator Startup

If you would like to help with calculation for specific case you want to use do not hesitate to reply.

If this does not answer your question(s), or I have forgotten something, or if you need more assistance, please contact me again.

- This issue will auto close in 7 days upon no reply.

Best Regards, Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thank !

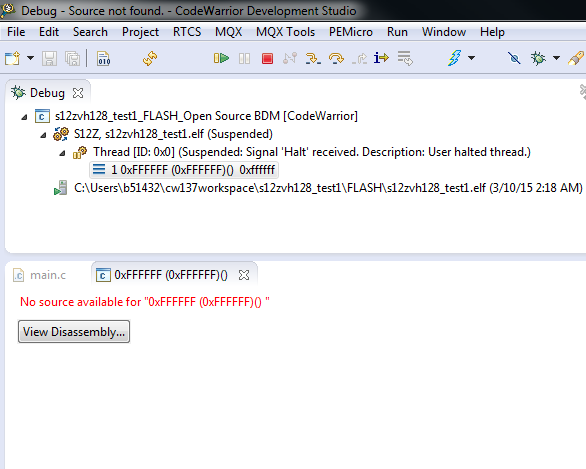

I use CW 10.6 , create PE project .

When i use "Internal clock" , it is 1MHZ, what's the biggest bus clock ?

When i select 30MHZ or 50 MHZ "Internal bus clock " , when build , there is no error ,while , when debug , it show

Could you tell me what's wrong with me .

And when i select 20 MHZ bus clock , it can work well .

Thank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As mentioned initially, the 'biggest' bus clock is 50MHz. I tested this using PE tool and the bus clock works OK (there is some deviation from target freq, but it works). It looks like you are having some other problem during debug. Are you stepping through the code?

Sometimes it is better to use breakpoints, run the code and observe signals on the scope or use LED indication. For example, you can use ECLK on PP0 pin to see the bus clock. This can be enabled by clearing the NECLK bit in ECLKCTL reg.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i do not know.

Could you please share you project to check it.

I would like to ask you, if possible, when you pack the project, could you please check whether it is able to be run in another PC. I really do not want to spend time to solving issues relaed to missing paths or files.

Btw; if you send me your requirement and inputs I am able to provide you functional example. I never use PE because it causes a lot of issues if you are not experienced about MCU. moreover analyzin "magic numbers" in generated SW is really wasting life.

OSCCLK = oscclk or ircclk ...... = ? MHz in the case of oscclk

BUSCLK =

PEI,PEE or PBE

Best regards,

Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You should check the S12ZVM reference manual, Chapter 8 - S12 Clock, Reset and Power Management Unit (S12CPMU_UHV_V6).

The bus clock can be derived from external clock (PEE and PBE mode) or from internal IRC1M clock (PEI mode)

The max bus clock can be set to 50MHz. The CPMU register of interest to calculate the bus frequency are:

CPMUPOSTDIV, CPMUREFDV and CPMUSYNR. In CPMUOSC register you can select the source clock.

Refer to chapter 8.7.3 Application Information for PLL and Oscillator Startup. There is an example how to set the bus clock.

Regards,

iggi