- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Baremetal MCG setting in Kinetis for FRDM-K20D50M ?

Baremetal MCG setting in Kinetis for FRDM-K20D50M ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am using FRDM-K20D50M board. I have done few programs using Processor expert and now i want to learn to code in baremetal without processor expert.How do I configure the following

MCG Mode : PEE

OSCERCLK: 8 Mhz

Core Clock : 50Mhz

Bus Clock : 50Mhz

Flash Clock: 25Mhz

I am sure many new user may be having issues in MCG settings as almost everything is related to this, being, PWM, UART, I2C, SPI, USB...., infact all peripherals. I tried learning from KQRUG

But was unable to. So please help me and others like me to figure this out.I also generated the code from processor expert but that was also confusing how things was done.

The below code is generated by processor expert for above configurations copied from "cpu.c".

/* System clock initialization */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=1,??=0,??=0,??=0,??=0,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x01) |

SIM_CLKDIV1_OUTDIV4(0x03); /* Set the system prescalers to safe value */

/* SIM_SCGC5: PORTA=1 */

SIM_SCGC5 |= SIM_SCGC5_PORTA_MASK; /* Enable clock gate for ports to enable pin routing */

if ((PMC_REGSC & PMC_REGSC_ACKISO_MASK) != 0x0U) {

/* PMC_REGSC: ACKISO=1 */

PMC_REGSC |= PMC_REGSC_ACKISO_MASK; /* Release IO pads after wakeup from VLLS mode. */

}

/* SIM_CLKDIV1: OUTDIV1=1,OUTDIV2=1,??=0,??=0,??=0,??=0,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x01) |

SIM_CLKDIV1_OUTDIV2(0x01) |

SIM_CLKDIV1_OUTDIV4(0x03); /* Update system prescalers */

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= (uint32_t)~(uint32_t)(SIM_SOPT2_PLLFLLSEL_MASK); /* Select FLL as a clock source for various peripherals */

/* SIM_SOPT1: OSC32KSEL=3 */

SIM_SOPT1 |= SIM_SOPT1_OSC32KSEL(0x03); /* LPO 1kHz oscillator drives 32 kHz clock for various peripherals */

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA_PCR18 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* PORTA_PCR19: ISF=0,MUX=0 */

PORTA_PCR19 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* Switch to FBE Mode */

/* MCG_C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG_C2 = (MCG_C2_RANGE0(0x02) | MCG_C2_EREFS0_MASK);

/* OSC0_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0_CR = OSC_CR_ERCLKEN_MASK;

/* MCG_C7: OSCSEL=0 */

MCG_C7 &= (uint8_t)~(uint8_t)(MCG_C7_OSCSEL_MASK);

/* MCG_C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x02) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK);

/* MCG_C4: DMX32=0,DRST_DRS=0 */

MCG_C4 &= (uint8_t)~(uint8_t)((MCG_C4_DMX32_MASK | MCG_C4_DRST_DRS(0x03)));

/* MCG_C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=1 */

MCG_C5 = MCG_C5_PRDIV0(0x01);

/* MCG_C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=1 */

MCG_C6 = MCG_C6_VDIV0(0x01);

while((MCG_S & MCG_S_OSCINIT0_MASK) == 0x00U) { /* Check that the oscillator is running */

}

while((MCG_S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to PBE Mode */

/* MCG_C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=1 */

MCG_C6 = (MCG_C6_PLLS_MASK | MCG_C6_VDIV0(0x01));

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

while((MCG_S & MCG_S_LOCK0_MASK) == 0x00U) { /* Wait until locked */

}

/* Switch to PEE Mode */

/* MCG_C1: CLKS=0,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK);

while((MCG_S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */

}

/*** End of PE initialization code after reset ***/

Kind Regards

Amit

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Amit

1) I didn't get how 8MHz value of oscillator is being feeded.

- The crystal oscillator is started using MCG_C2 and being connected using MCG_C1.

2) How the calculation is being done so that

Core Clock : 50Mhz

Bus Clock : 50Mhz

Flash Clock: 25Mhz

The system and bus and flash dividers are set in SIM_CLKDIV1

3) What is the limitation of each modes? i.e is it possible to get 50Mhz core clock in some other mode except PEE mode.

FEE can be used but is not very flexible - 50Mhz is not possible from 8MHz crystal (45.75MHz is possible with (8MHz / 256) * 1464). It is more useful when using a 32kHz crystal but has more jitter than PEE. 48MHz is possible from 32k, which can be used for USB.

[By the way, if not using USB a K10 would probably be more suitable than K20]

4) I couldn't find where it is mention what is the requirement for each mode in the K20P64M50SFORM ?

Question not specific enough.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit,

Please check below link, which is K20 50MHz example source code. There provides FRDM-K20D50M board MCG setting: external crystal clock 8MHz, system and bus clock run at 50MHz, flash clock runs at 25MHz.

http://cache.freescale.com/files/32bit/software/KINETIS_50MHZ_SC.zip

Please check MCG clock setting at [frdm-k20d50m-demo_freedom] project.

I also use Processor Expert tool generates related code below for your reference:

/* System clock initialization */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=1,??=0,??=0,??=0,??=0,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x01) |

SIM_CLKDIV1_OUTDIV4(0x03); /* Set the system prescalers to safe value */

/* SIM_SCGC5: PORTA=1 */

SIM_SCGC5 |= SIM_SCGC5_PORTA_MASK; /* Enable clock gate for ports to enable pin routing */

if ((PMC_REGSC & PMC_REGSC_ACKISO_MASK) != 0x0U) {

/* PMC_REGSC: ACKISO=1 */

PMC_REGSC |= PMC_REGSC_ACKISO_MASK; /* Release IO pads after wakeup from VLLS mode. */

}

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=0,??=0,??=0,??=0,??=0,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x00) |

SIM_CLKDIV1_OUTDIV4(0x01); /* Update system prescalers */

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= (uint32_t)~(uint32_t)(SIM_SOPT2_PLLFLLSEL_MASK); /* Select FLL as a clock source for various peripherals */

/* SIM_SOPT1: OSC32KSEL=3 */

SIM_SOPT1 |= SIM_SOPT1_OSC32KSEL(0x03); /* LPO 1kHz oscillator drives 32 kHz clock for various peripherals */

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA_PCR18 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* PORTA_PCR19: ISF=0,MUX=0 */

PORTA_PCR19 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* Switch to FBE Mode */

/* MCG_C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG_C2 = (MCG_C2_RANGE0(0x02) | MCG_C2_EREFS0_MASK);

/* OSC0_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0_CR = OSC_CR_ERCLKEN_MASK;

/* MCG_C7: OSCSEL=0 */

MCG_C7 &= (uint8_t)~(uint8_t)(MCG_C7_OSCSEL_MASK);

/* MCG_C1: CLKS=2,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x02) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK);

/* MCG_C4: DMX32=0,DRST_DRS=0 */

MCG_C4 &= (uint8_t)~(uint8_t)((MCG_C4_DMX32_MASK | MCG_C4_DRST_DRS(0x03)));

/* MCG_C5: ??=0,PLLCLKEN0=0,PLLSTEN0=0,PRDIV0=3 */

MCG_C5 = MCG_C5_PRDIV0(0x03);

/* MCG_C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=1 */

MCG_C6 = MCG_C6_VDIV0(0x01);

while((MCG_S & MCG_S_OSCINIT0_MASK) == 0x00U) { /* Check that the oscillator is running */

}

while((MCG_S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to PBE Mode */

/* MCG_C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=1 */

MCG_C6 = (MCG_C6_PLLS_MASK | MCG_C6_VDIV0(0x01));

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

while((MCG_S & MCG_S_LOCK0_MASK) == 0x00U) { /* Wait until locked */

}

/* Switch to PEE Mode */

/* MCG_C1: CLKS=0,FRDIV=3,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK);

while((MCG_S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */

}

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hui_Ma

Thanks for replying. is there any issue in writing

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= ~(SIM_SOPT2_PLLFLLSEL_MASK);

or

SIM_SOPT2 &= SIM_SOPT2_PLLFLLSEL_SHIFT;

in place of the code generated by PE. i.e

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= (uint32_t)~(uint32_t)(SIM_SOPT2_PLLFLLSEL_MASK); /* Select FLL as a clock source for various peripherals */

Kind Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit,

Below writing without any problem:

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= ~(SIM_SOPT2_PLLFLLSEL_MASK);

While, below writing is wrong:

SIM_SOPT2 &= SIM_SOPT2_PLLFLLSEL_SHIFT; same as SIM_SOPT2 &= 0x10;

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hui_Ma

I tried understanding the code generated by Processor expert, I wrote the following code according to PE and Mark's Code.

void mcg_init()

{

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x01) |

SIM_CLKDIV1_OUTDIV4(0x01); /* Set the system prescalers to safe value */

/* Enabling Gate Clk of POART A */

SIM_SCGC5 |= SIM_SCGC5_PORTA_MASK;

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM_SOPT2 &= SIM_SOPT2_PLLFLLSEL_MASK;

/* SIM_SOPT1: OSC32KSEL=3 */

SIM_SOPT1 |= SIM_SOPT1_OSC32KSEL(0x03); /* LPO 1kHz oscillator drives 32 kHz clock for various peripherals */

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA_PCR18 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* PORTA_PCR19: ISF=0,MUX=0 */

PORTA_PCR19 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* Switch to FBE Mode */

MCG_C2 |= (MCG_C2_RANGE0(0x02) | MCG_C2_EREFS0_MASK | MCG_C2_HGO0_MASK);

OSC0_CR = OSC_CR_ERCLKEN_MASK; // Enable external clock

MCG_C1 = (MCG_C1_CLKS(0x02) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK); //clk src =External clk, Ref clk= internal ref clk

MCG_C5 = MCG_C5 = MCG_C5_PRDIV0(0x03); // PRDIV0=3

MCG_C6 = MCG_C6_VDIV0(0x01); // VDIV0=1

while((MCG_S & MCG_S_OSCINIT0_MASK) == 0x00U) {}/* Check that the oscillator is running */

while((MCG_S & MCG_S_IREFST_MASK) != 0x00U) {} /* Check that the source of the FLL reference clock is the external reference clock. */

while((MCG_S & 0x0CU) != 0x08U) {} /* Wait until external reference clock is selected as MCG output */

/* Switch to PBE Mode */

MCG_C6 = (MCG_C6_PLLS_MASK | MCG_C6_VDIV0(0x01));

while((MCG_S & 0x0CU) != 0x08U) {} /* Wait until external reference clock is selected as MCG output */

while((MCG_S & MCG_S_LOCK0_MASK) == 0x00U) {} /* Wait until locked */

/* Switch to PEE Mode */

MCG_C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x03) | MCG_C1_IRCLKEN_MASK);

while((MCG_S & 0x0CU) != 0x0CU) {} /* Wait until output of the PLL is selected */

}

In The above code I have following concerns :

1) I didn't get how 8MHz value of oscillator is being feeded.

2) How the calculation is being done so that

Core Clock : 50Mhz

Bus Clock : 50Mhz

Flash Clock: 25Mhz

3) What is the limitation of each modes? i.e is it possible to get 50Mhz core clock in some other mode except PEE mode.

4) I couldn't find where it is mention what is the requirement for each mode in the K20P64M50SFORM ?

Kind Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Amit

1) I didn't get how 8MHz value of oscillator is being feeded.

- The crystal oscillator is started using MCG_C2 and being connected using MCG_C1.

2) How the calculation is being done so that

Core Clock : 50Mhz

Bus Clock : 50Mhz

Flash Clock: 25Mhz

The system and bus and flash dividers are set in SIM_CLKDIV1

3) What is the limitation of each modes? i.e is it possible to get 50Mhz core clock in some other mode except PEE mode.

FEE can be used but is not very flexible - 50Mhz is not possible from 8MHz crystal (45.75MHz is possible with (8MHz / 256) * 1464). It is more useful when using a 32kHz crystal but has more jitter than PEE. 48MHz is possible from 32k, which can be used for USB.

[By the way, if not using USB a K10 would probably be more suitable than K20]

4) I couldn't find where it is mention what is the requirement for each mode in the K20P64M50SFORM ?

Question not specific enough.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark

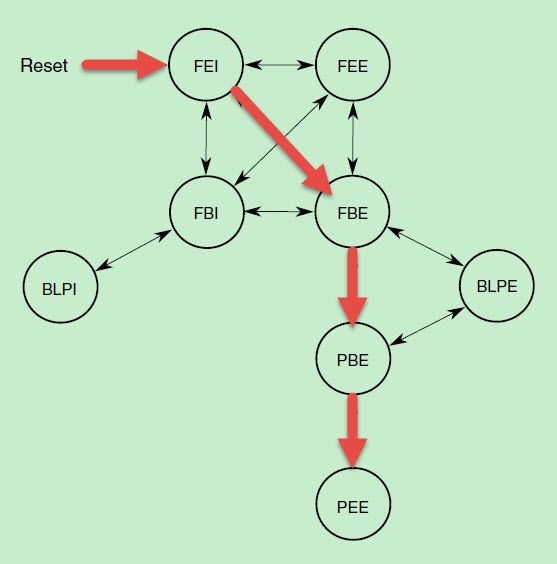

According to the above Figure to configure to PEE mode we have to go through FEI(Default)-------> FEE(Not Done in above code)--------->FBE(Done)------->PBE(Done)---------->PEE(Done).

But still the code worked.

Thanks For the support.

Kind Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit,

MCG mode switch is using below ways: from FEI to PEE

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hui_Ma

Thanks for clarification I realized this later.

Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot Mark.

In my 4th point I wanted to know what are the register settings for each mode. As I was unable to locate that in user manual. Rest all the points are crystal clear now.

Warm Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit,

The K20_50MHz reference manual chapter 24.4.1.1 MCG modes of operation with Table 24-16 shows register value during difference MCG mode.

I do recommend customer to use Processor Expert tool to setting MCG clock mode, which will be more easy and flexible.

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Amit

50MHz is achieved by setting CLOCK_MUL to 25 (rather than 24) but note that USB will then not be able to work from the internal clock since it needs a 48MHz frequency.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Amit

The following code shows how to set 48MHz system clock with 24MHz bus and flash clocks.

There is no cde there that is not relevant to this task and the defines used should be more understandable that the ones in the PE generated code. I have also written the hex values that are actually programmed to the registers so that you can compare with the user manual's register descriptions.

MCG_C2 = (MCG_C2_RANGE_1M_8M | MCG_C2_GAIN_MODE | MCG_C2_EREFS | MCG_C2_LOCRE0); // select crystal oscillator [0x14]

MCG_C1 = (MCG_C1_CLKS_PLL_FLL | MCG_C1_CLKS_EXTERN_CLK | MCG_C1_FRDIV_256); // switch to external source (the FLL input clock is set to as close to its input range as possible, although this is not absolutely necessary if the FLL will not be used) [0x98]

while (!(MCG_S & MCG_S_OSCINIT)) {} // loop until the crystal source has been selected

while (MCG_S & MCG_S_IREFST) {} // loop until the FLL source is no longer the internal reference clock

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_EXTERN_CLK) {} // loop until the external reference clock source is valid

MCG_C5 = ((CLOCK_DIV - 1) | MCG_C5_PLLSTEN0); // now move from state FEE to state PBE (or FBE) PLL remains enabled in normal stop modes [0x23]

MCG_C6 = ((CLOCK_MUL - MCG_C6_VDIV0_LOWEST) | MCG_C6_PLLS); // [0x40]

while ((MCG_S & MCG_S_PLLST) == 0) {} // loop until the PLLS clock source becomes valid

while ((MCG_S & MCG_S_LOCK) == 0) {}// loop until PLL locks

SIM_CLKDIV1 = (((SYSTEM_CLOCK_DIVIDE - 1) << 28) | ((BUS_CLOCK_DIVIDE - 1) << 24) | ((FLASH_CLOCK_DIVIDE - 1) << 16)); // prepare bus clock divides [0x00110000]

MCG_C1 = (MCG_C1_CLKS_PLL_FLL | MCG_C1_FRDIV_1024); // finally move from PBE to PEE mode - switch to PLL clock [0x28]

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_PLL) {} // loop until the PLL clock is selected

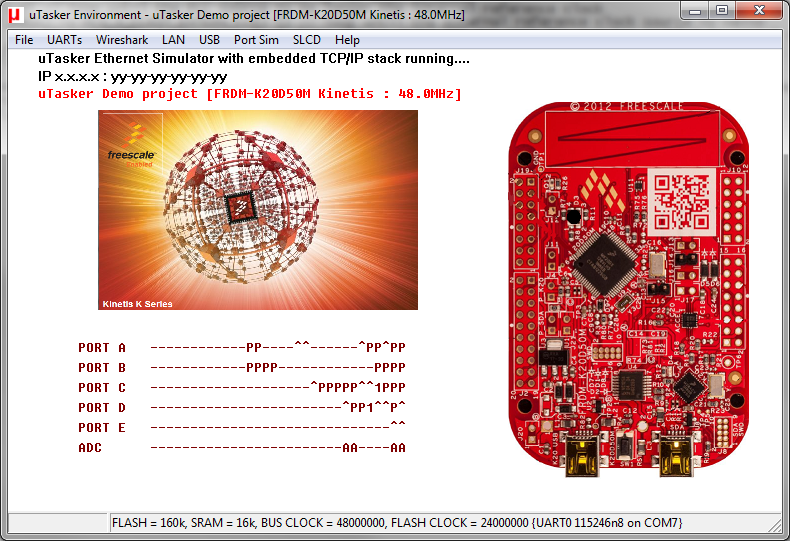

When using a crystal the loading resistors and capacitors in the circuit are important since the oscillator gain must be set to mathc - if it doesn't match the ocillator may not start. In the case of the FRDM-K20D50M the loading is low so the gain must be set to low (MCG_C2_GAIN_MODE is 0). The code is taken from the uTasker project which allows simple configuration and will warn in case of setting anything out of range. It's simulator shows the achieved settinmgs when it runs. The user level setup for the FRDM-K20D50M is as follows:

#define OSC_LOW_GAIN_MODE // oscillator without feedback resistor or load capacitors so use low gain mode

#define CRYSTAL_FREQUENCY 8000000 // 8 MHz crystal

#define CLOCK_DIV 4 // input must be divided to 2MHz..4MHz range (/1 to /25 possible)

#define CLOCK_MUL 24 // the PLL multiplication factor to achieve system/core operating frequency of 48MHz (x24 to x55 possible)

#define BUS_CLOCK_DIVIDE 1 // bus clock without divide for 48MHz

#define FLASH_CLOCK_DIVIDE 2 // flash clock divided by 2 for 24MHz

#define USB_CLOCK_GENERATED_INTERNALLY // use USB clock from internal source rather than external pin

As you can see, it is very simple to adjust any settings without needing to get involved with the values to put in the registers themselves.

Below is the simulator showing the operation with these settings.

The project includes configurations for almost every Freescale development board (KE, KL and K series) and the simulator will accurately verify just about all processor types.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark

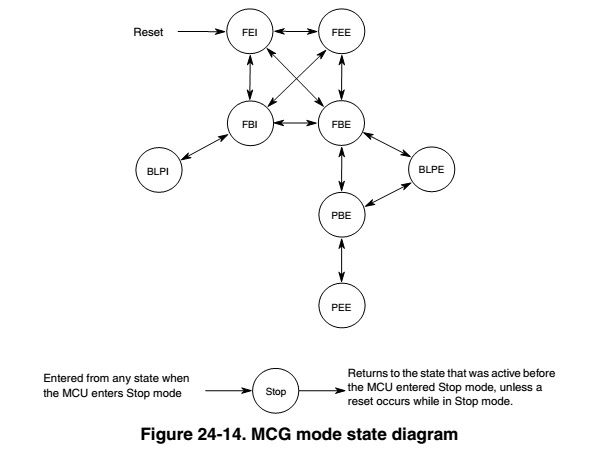

Thanks for the concise code. I will go through this and try to get the related info. Meanwhile I found this fig.

I realized that the config I want to do is the last one i.e PEE. so such huge process is required .

Kind Regards

Amit