- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- rt1170 jtag/swd

rt1170 jtag/swd

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

rt1170 jtag/swd

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

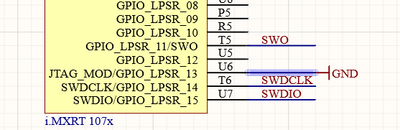

we have a custom board similar to rt1170 evk.How i can config cpu to work in SWD mode?

i need pull up at JTAG_MUX_MOD GPIO_LPSR_13?

How can i check what mode is configured? i need to be sure i am SWD.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

we connected JTAG_MUX_MOD GPIO_LPSR_13 to Ground

and hardware eng check out all nxp pin requirements

SWD not stable i cannot access peripheral registries and gpios

i can burn flash erase flash and it ok

please help us to find out what the problem here?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

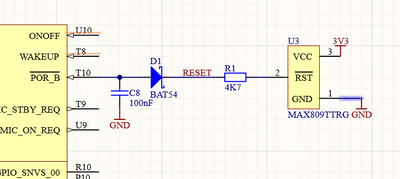

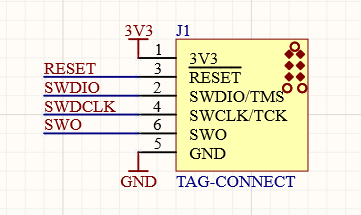

I use this on my boards which works:

Regards,

Carsten

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1)How I can config CPU to work in SWD mode?

-- By default, the RT1170 silicon can use both SWD and JTAG modes using the Arm stitching sequence.

2) How can I check what mode is configured? I need to be sure I am SWD.

-- During debug process, IDE has the option of debug interface and assures select the SWD interface.

Definitely, please follow the 5 Debugging and programming section in the attached guide to designing an appropriate SWD interface on your board.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

we connected JTAG_MUX_MOD GPIO_LPSR_13 to Ground

and hardware eng check out all nxp pin requirements

SWD not stable i cannot access peripheral registries and gpios

i can burn flash erase flash and it ok

please help us to find out what the problem here?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

Firstly, the SWD interface is good after reviewing the above schematic.

Next, I'm not clear about the unstable behaves of SWD you mentioned, for instance, can't access peripheral registries and gpios, can you provide the testing steps in detail?

Last, I'd like to know what debug tool you used.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

its seems i know what is my problem!!!

the RT1170 rev B is reset via debugger (SYSRESET_REQ), the boot ROM will not jump to the flash application although it is valid but enter a debug loop at a fixed PC address (0x00223104). The debugger then needs to initialize PC and SP manually in order to jump to the user application.

we are rev. B MCUXpresso IDE v11.3.0 and EVK is rev. A

how to config rt1170 reset script forMCUXpresso IDE v11.3 ?

do i need to upgrade IDE version ?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) Do I need to upgrade the IDE version?

-- Yes, I think so.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

we still have a problem!

we use nxp MCU-Link connected to SWD pins

blinky demo app flashed but i cannot stop at main()

its stopsat 0x0 address of RAM and faulted

our cpu is rt1170 rev B

we use reset and connect scripts RT1170_reset.scp and RT1170_connect_M7_wake_M4.scp

why its doesnt works ? its looks RT1170_reset.scp cannot reset CPU properly

pls see screenshots and log below

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

I'd like to suggest you do three more testings.

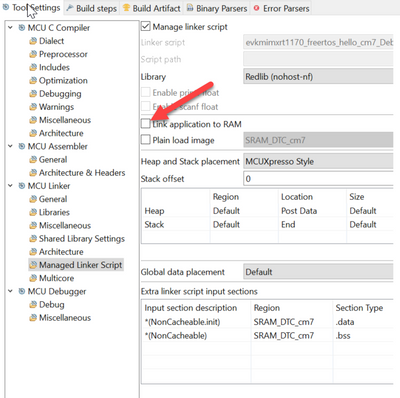

1) After opting the Link application to RAM, then give a debug.

2) Use the tool to program the image to QSPI, then check the board whether can boot up successfully.

3) Please use other IDEs such as IAR, Keil to do debug testing.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I checked RAM image its works.

I also check QSPI flash burn works ok.

The problem here is Rev B of the CPU and workaround scripts NXP didnt work

i suppose its still in debug loop

Did you fix it in CPU rev C ? please can you ask guys in R&D ?

pls see log below reste script reset cannot reset cpu

Regards

Vladimir

Reconnected to existing LinkServer process.

============= SCRIPT: RT1170_connect_M7_wake_M4.scp =============

RT1170 Connect M7 and Wake M4 Script

DpID = 6BA02477

APID = 0x84770001

Releasing M4

View cores on the DAP AP

DpID = 6BA02477

TAP 0: 6BA02477 Core 0: M7 APID: 84770001 ROM Table: E00FD003*

TAP 0: 6BA02477 Core 1: M4 APID: 24770011 ROM Table: E00FF003

============= END SCRIPT ========================================

Probe Firmware: MCU-LINK (r0FF) CMSIS-DAP V2.245 (NXP Semiconductors)

Serial Number: V11WCQGT00G2T

VID:PID: 1FC9:0143

USB Path: /dev/hidraw1

Using memory from core 0 after searching for a good core

debug interface type = CoreSight DP (DAP DP ID 6BA02477) over SWD TAP 0

processor type = Cortex-M7 (CPU ID 00000C27) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 6BA02477. CpuID: 00000C27. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C Gen SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 Gen DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E Gen (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 Gen ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04004BB906 CSt type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0043000: CID B105900D PID 04001BB908 CSt CSTF type 0x12 Trace Link - Trace funnel/router

NXP: MIMXRT1176xxxxx

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT1170_SFDP_QSPI.cfx

Image 'iMXRT1170_FlexSPI_SFDP_QSPI Sep 14 2021 15:10:32'

Opening flash driver MIMXRT1170_SFDP_QSPI.cfx

Sending VECTRESET to run flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (16MB = 256*64K at 0x30000000)

Closing flash driver MIMXRT1170_SFDP_QSPI.cfx

Connected: was_reset=false. was_stopped=false

Awaiting telnet connection to port 3330 ...

GDB nonstop mode enabled

Opening flash driver MIMXRT1170_SFDP_QSPI.cfx (already resident)

Sending VECTRESET to run flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (16MB = 256*64K at 0x30000000)

Writing 28004 bytes to address 0x30000000 in Flash

Sectors written: 0, unchanged: 1, total: 1

Erased/Wrote sector 0-0 with 28004 bytes in 15msec

Closing flash driver MIMXRT1170_SFDP_QSPI.cfx

Flash Write Done

Flash Program Summary: 28004 bytes in 0.01 seconds (1823.18 KB/sec)

============= SCRIPT: RT1170_reset.scp =============

SYSTEM Reset

DpID = 6BA02477

TAP 0: 6BA02477 Core 0: M7 APID: 84770001 ROM Table: E00FD003*

TAP 0: 6BA02477 AP 1: APID: 24770011 ROM Table: E00FF003

TAP 0: 6BA02477 AP 2: APID: 54770002 ROM Table: 00000002

APID = 0x84770001

Setting M4 spin code

Setting M4 clock

Resetting M4 core

Releasing M4

View cores on the DAP AP

DpID = 6BA02477

TAP 0: 6BA02477 Core 0: M7 APID: 84770001 ROM Table: E00FD003*

TAP 0: 6BA02477 Core 1: M4 APID: 24770011 ROM Table: E00FF003

R15 = 0x00223104

Vector table SP/PC is the reset context.

PC = 0x00000000

SP = 0x00000040

XPSR = 0x01000000

VTOR = 0x30002000

============= END SCRIPT ===========================

Stopped: <cannot read registers>Unknown

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

According to your reply, it's available to debug after opting the Link application to RAM, meanwhile, the custom board can boot up from the QSPI if burn the application image to it before.

Is my understanding right?

Further, I'd like to whether you ever try to use other IDEs such as IAR, Keil to do debug testing and how is going on?

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI!

I cannot boot from QSPI firmware not running cannot blink LED.

The only thing working is burning/erasing flash.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

Actually, your chip is still an A version, not the Rev B.

In my opinion, the issue is related to the hardware and I'd like to whether the issue happens on all custom boards.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

First of all pls see the photo of ref board CPU its not the same.

in xpresso there is cpu reset script RT1170reset.scp

there is a rev. check inside of RT1170reset.scp

REM Check RT1170 Rev: no special handling for Rev A

IF v% & 0x00FFFFF0 == 0x1170B0 Then print REV. B and we here print is is rev B

IF v% & 0x00FFFFF0 == 0x1170A0 Then print REV. A

The local distributor also said there is not rev. A anymore

I sure its rev. B some patch of ot

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

Actually, I was a bit confused about the Rev B you mentioned, as I don't find any Rev B information in the uploaded log.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

(gdb) x 0x40C84800

0x40c84800: 0x001170b0

at the chip its rev. A but chip id from debug is B

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

I was wondering if you can introduce your testing environment, for instance, the version of the MCUXpress IDE, the firmware of the MCU-link, as I've no idea of how to get the below information you shared.

(gdb) x 0x40C84800

0x40c84800: 0x001170b0

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi!

first and foremost our design is similar to NXP evk.we checked with logic NOR flash burn at EVK and our board its the same

power up sequance the same at EVK and our board and not the same as hardware development guideMIMXRT1170 Rev 1 depicts it .We dont see VDD_SNVS_DIG line from CPU its always zero at both boards. When we checked SWD with logic analyzier we see turn signal behavior is different state at EVK and out board.

pls see sceenshot i want to access 0x40800000

unsigned int *p=(unsigned int*)0x40800000;

gdb cannot access value of p wiht error Cannot access memory at address 0x207dd0

at EVK the same code the result is p=0x40800000

SWD is unstable what the problem here?

i found out there is errata about SWD

ERR006941: Core: Asynchronous sampling of SWDIOTMS might cause incorrect

operation of SerialWire/JTAG Debug Port

Regards